Professional Documents

Culture Documents

EE8451 - LIC - by WWW - LearnEngineering.in PDF

EE8451 - LIC - by WWW - LearnEngineering.in PDF

Uploaded by

Chiraag ChiruOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

EE8451 - LIC - by WWW - LearnEngineering.in PDF

EE8451 - LIC - by WWW - LearnEngineering.in PDF

Uploaded by

Chiraag ChiruCopyright:

Available Formats

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.

in

ENGINEERING COLLEGES

2017-2018 ODD SEMESTER

IMPORTANT QUESTIONS AND ANSWERS

DEPARTMENT OF EEE

SUBJECT CODE: EE 6303

SUBJECT NAME: LINEAR INTEGRATED CIRCUITS AND APPLICATIONS

Regulation: 2013 Year and Semester: II/III

Prepared by

Affiliating

Si.No Name of the Faculty Designation

College

1 Mr. S. Murugan Associate Professor FXEC

2 Mrs. R. Banumathy Assistant Professor FXEC

IMPORTANT QUESTIONS AND ANSWERS

3 Mr.S. Ebanezar Pravin Assistant Professor SCADCET

4 Mr. A. Rathinavel Pandian Assistant Professor SMTEC

DEPARTMENT OF EEE

SUBJECT CODE: EE 8451

SUBJECT NAME: LINEAR INTEGRATED CIRCUITS AND APPLICATIONS

Verified By DLI, CLI and Approved by the Centralized Monitoring Team

Regulation: 2017

Dated.01.07.2017

Year and Sem : II/IV

COPYRIGHT @ SCAD

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

REGULATION 2017

EE 8451LINEAR INTEGRATED CIRCUITS AND APPLICATIONS L TPC

3 0 03

UNIT I IC FABRICATION 9

IC classification, fundamental of monolithic IC technology, epitaxial growth, masking

and etching, diffusion of impurities. Realization of monolithic ICs and packaging.

Fabrication of diodes, capacitance, resistance and FETs.

UNIT II CHARACTERISTICS OF OPAMP 9

Ideal OP-AMP characteristics, DC characteristics, AC characteristics, differential

amplifier; frequency response of OP-AMP; Basic applications of op-amp – Inverting

and Non-inverting Amplifiers-V/I & I/V converters,summer, differentiator and integrator.

UNIT III APPLICATIONS OF OPAMP 9

Instrumentation amplifier, Log and Antilog Amplifiers, first and second order active

filters, comparators, multivibrators, waveform generators, clippers, clampers, peak

detector, S/H circuit, D/A converter (R- 2R ladder and weighted resistor types), A/D

converters using op-amps.

UNIT IV SPECIAL ICs 9

Functional block, characteristics & application circuits with 555 T imer IC-566

voltage controlled oscillator IC, 565-phase lock loop IC ,Analog multiplier ICs.

UNIT V APPLICATION ICs 9

IC voltage regulators –LM78XX,79XX Fixed voltage regulators - LM317, 723 Variable

voltage regulators, switching regulator- SMPS- LM 380 power amplifier- ICL 8038

function generator IC.

TOTAL: 45 PERIODS

TEXT BOOKS:

1. David A. Bell, ‘Op-amp & Linear ICs’, Oxford, 2013.

2. D. Roy Choudhary, Sheil B.Jani, ‘Linear Integrated Circuits’, II edition, New

Age, 2003.

3. Ramakant A.Gayakward, ‘Op-amps and Linear Integrated Circuits’, IV edition,

Pearson Education, 2003, PHI. 2000.

REFERENCES:

1. Fiore,‘Op-amps & Linear Integrated Circuits Concepts &

Applications’,Cengage,2010.

2

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

2. Floyd , Buchla, ‘Fundamentals of Analog Circuits’, Pearson, 2013.

3. Jacob Millman, Christos C.Halkias, ‘Integrated Electronics - Analog and Digital

circuits system’, Tata McGraw Hill, 2003.

4. Robert F.Coughlin, Fredrick F. Driscoll, ‘Op-amp and Linear ICs’, PHI Learning,

6th edition, 2012.

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

SCAD Group of Institutions

Department of Electrical and Electronics Engineering

Detailed Lesson Plan

Name of the Subject& Code: EE 8451& LINEAR INTEGRATED CIRCUITS

AND APPLICATIONS

TEXT BOOKS:

1. David A. Bell, ‘Op-amp & Linear ICs’, Oxford, 2013.

2. D. Roy Choudhary, Sheil B.Jani, ‘Linear Integrated Circuits’, II edition, New

Age, 2003.

3. Ramakant A.Gayakward, ‘Op-amps and Linear Integrated Circuits’, IV

edition, Pearson Education, 2003, PHI. 2000.

REFERENCES:

& Linear Integrated Circuits Concepts &

1. Fiore,‘Op-amps

Applications’,Cengage,2010.

2. Floyd , Buchla, ‘Fundamentals of Analog Circuits’, Pearson, 2013.

3. Jacob Millman, Christos C.Halkias, ‘Integrated Electronics - Analog and

Digital circuits system’, Tata McGraw Hill, 2003.

4. Robert F.Coughlin, Fredrick F. Driscoll, ‘Op-amp and Linear ICs’, PHI

Learning, 6th edition, 2012.

Hours

Sl. Cumulative Books

Unit Topic / Portions to be Covered Required /

No Hrs Referred

Planned

UNIT I IC FABRICATION

1 I IC classification 1 1 T2

Fundamental of monolithic IC

2 I 1 2 T2

technology

3 I Epitaxial growth 1 3 T2

4 I Masking and etching 1 4 T2

5 I Diffusion of impurities 1 5 T2

Realization of monolithic ICs and

6 I 1 6 T2

packaging

7 I Fabrication of diodes 1 7 T2

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

8 I Fabrication of capacitance 1 8 T2

9 I Fabrication of resistance 1 9 T2

10 I Fabrication of FETs 1 10 T2

UNIT II CHARACTERISTICS OF OPAMP

11 II Ideal OP-AMP characteristics 1 11 T2

12 II DC characteristics 1 12 T2

13 II AC characteristics 1 13 T2

14 II Differential amplifier 1 14 T2

15 II Frequency response of OP-AMP 1 15 T2

Basic applications of op-amp – Inverting

16 II 2 17 T2

and Non-inverting Amplifiers

17 II V/I & I/V converters 1 18 T2

18 II Summer, differentiator and integrator 2 20 T2

UNIT III APPLICATIONS OF OPAMP

19 III Instrumentation amplifier 1 21 T2

20 III Log and Antilog Amplifiers 1 22 T2

21 III First and second order active filters 1 23 T2

22 III Comparators 1 24 T2

23 III Multivibrators 1 25 T2

24 III Waveform generators 1 26 T2

Clippers, clampers, peak detector, S/H

25 III 2 28 T2

circuit

D/A converter (R- 2R ladder and

26 III 1 29 T2

weighted resistor types)

27 III A/D converters using op-amps 1 30 T2

UNIT IV SPECIAL ICs

28 IV Functional block of 555 Timer 1 31 T2

29 IV Characteristics of 555 Timer 1 32 T2

30 IV Application circuits with 555 Timer 2 34 T2

31 IV IC-566 voltage controlled oscillator IC 1 35 T2

32 IV IC 565-phase lock loop IC 1 36 T2

33 IV Analog multiplier ICs 2 38 T2

UNIT V APPLICATION ICs

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

34 V IC voltage regulators –LM78XX,79XX 2 40 T2

35 V Fixed voltage regulators 1 41 T2

36 V LM317, 723 Variable voltage regulators 2 43 T2

37 V Switching regulator 1 44 T2

38 V SMPS 1 45 T2

39 V LM 380 power amplifier 1 46 T2

40 V ICL 8038 function generator IC 1 47 T2

Faculty Incharge HoD

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

INDEX

Unit No Q.NO Content Page No

Cover page 1

Syllabus 2-3

Lesson plan 4-6

I 1-12 Part A 9-11

I 1-5 Part B 11-25

Steps involved in fabrication of

I 1 11-14

IC

Fabrication of diodes and

I 2 14-17

capacitors

I 3 Fabrication of Resistors & FET 17-21

I 4 Photolithography 21-23

I 5 Different IC packages 24-25

II 1-15 Part A 26-28

II 1-6 Part B 28-52

II 1 Dc characteristics of Op-amp 28-33

II 2 Ac characteristics of Op-amp 33-37

II 3 Differentiator & Integrator 37-41

II 4 Differential amplifier 42-45

Inverting and Non-inverting

II 5 45-48

amplifier

II 6 Applications of Op-amp 48-52

III 1-10 Part A 53-54

III 1-5 Part B 55-68

III 1 Instrumentation amplifier 55-58

III 2 Schmitt trigger 58-60

III 3 R-2R DAC 60-62

III 4 Successive approx. type ADC 62-64

III 5 II order LPF 64-68

IV 1-15 Part A 69-70

IV 1-4 Part B 71-79

IV 1 Monostable multivibrator 71-72

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

IV 2 Astable multivibrator 73-74

IV 3 PLL 75-77

IV 4 VCO 77-79

V 1-15 Part A 80-83

V 1-5 Part B 83-98

V 1 LM 380 power amplifier 83-87

IC 723 general purpose

V 2 87-88

regulator

V 3 IC 8038 Function generator 89-91

V 4 LM 317 IC 92-94

V 5 Optocoupler IC 94-98

University question papers 99-118

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

UNIT I

IC FABRICATION

Part - A

1. Define an Integrated circuit.

An integrated circuit(IC) is a miniature, low cost electronic circuit consisting of

active and passive components fabricated together on a single crystal of silicon. The

active components are transistors and diodes and passive components are resistors

and

capacitors

2. What are the basic processes involved in fabricating ICs using planar

technology? (April/May 2015)

1. Silicon wafer (substrate) preparation

2. Epitaxial growth

3. Oxidation

4. Photolithography

5. Diffusion

6. Ion implantation

7. Isolation technique

8. Metallization

9. Assembly processing & packaging

3. List out the steps used in the preparation of Si – wafers.

1. Crystal growth &doping

2. Ingot trimming & grinding

3. Ingot slicing

4. Wafer policing & etching

5. Wafer cleaning

4. Write the basic chemical reaction in the Epitaxial growth process of pure

silicon.

The basic chemical reaction in the Epitaxial growth process of pure silicon is the

Hydrogen reduction of silicon tetrachloride

1200oC

SiCl 4 + 2H2 <-----------> Si + 4 HCl

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

5. What are the two important properties of SiO2?

SiO2 is an extremely hard protective coating & is unaffected by almost all

reagents except by hydrochloric acid. Thus it stands against any

contamination.

By selective etching of SiO2, diffusion of impurities through carefully

defined windows in the SiO2 can be accomplished to fabricate various

components.

6. Explain the process of oxidation.

The silicon wafers are stacked up in a quartz boat & then inserted into quartz

furnace tube. The Si wafers are raised to a high temperature in the range of 950 to

1150oC & at the same time, exposed to a gas containing O2 or H2O or both. The

chemical action is

Si + 2H2O -----------> SiO2 + 2H2

7. What is lithography?

Lithography is a process by which the pattern appearing on the mask is

transferred to the wafer. It involves two steps: the first step requires applying a few

drops of photo resist to the surface of the wafer & the second step is spinning the

surface to get an even coating of the photo resist across the surface of the wafer.

8. What are the two processes involved in photolithography?

a) Making a photographic mask :

The development of photographic mask involves the preparation of initial

artwork and its reduction, decomposition of initial artwork or layout into several mask

layers.

b) Photo etching :

Photo etching is used for the removal of SiO2 from desired regions so that the

desired impurities can be diffused.

9. Define diffusion. (April/May 2015)

The process of introducing impurities into selected regions of a silicon wafer

is called diffusion. The rate at which various impurities diffuse into the silicon will be of

the order of 1µm/hr at the temperature range of 900oC to 1100o C .The impurity atoms

have the tendency to move from regions of higher concentrations to lower

concentrations.

10

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

10. What are the advantages

ages of ion implantation technique? (April/Ma

ril/May 2015)

• It is performed at low te

temperature. Therefore, previously diffused

sed regions

r have

a lesser tendency for lateral

late spreading.

• In diffusion process,

s, tem

temperature has to be controlled over a large area inside

the oven, whereas in io

ion implantation process, accelerating poten

potential & beam

content are dielectrically

rically controlled from outside.

11. What are the advantages

tages of IC over discrete components? (April/May

(Apri 2015)

(Nov/Dec 2014) (Nov/Dec 201

c 2016)

• Miniaturization and hence

henc increased equipment density.

• Cost reduction due

e to ba

batch processing.

• Increased system reliab

reliability due to elimination of soldered joints.

• Increased functional per

al performance.

• Increased operating spe

g speed.

• Reduction in powerr consumption

cons

12. Name the different types

ypes IIC packages?

There are three different

nt pac

packages available. They are

• Metal can

n pack

package

• Ceramic flat pa

package

• Dual-in-line

ne pa

package

Part -B

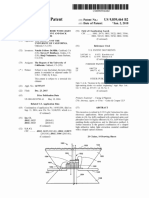

1. With the help off nea

neat sketches completely describe vari

various stages

involved in the fabricat

brication of ICs (OR)

R)

With neat diagram

m ex

explain the steps involved in the fabrica

abrication of the

circuit shown in figure

igure by using IC technology.

The various steps in the fabric

fabrication of monolithic IC is described below

1. Wafer preparation 2. Epitaxial

Epi growth 3 .Oxidation

4. Isolation diffusion 5. Bas

Base diffusion 6.Emitter diffusion

7. Aluminum metallization

ation

11

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

i. Wafer Preparation:

• The starting material called

ca the substrate is a p-type silicon wafer. The wafers

are usually 10cm diamet

iameter and 0.4mm thickness.

• The resistivity is 10Ω/cm

Ω/cm corresponding to the concentration of ac

acceptor atom

NA=1.4X1015atoms/cm

Step 1

p – Type substrate

su

10 Ω – cm rresistivity NA = 1.4 x 1015 atoms/cm3 400 µm

Fig 1.1 Wafer preparation

ii. Epitaxial growth:

• An n-type epitaxiall film is grown on the p-type as shown in fig. This

Th ultimately

becomes the collector

ctor re

region of the transistor or an elementt of th

the diode and

diffused capacitor assoc

associated with the circuit.

N – epi layer 0.1 – 0.5 Ω - cm 5 – 25 µm

p – Typ

ype substrate 10 Ω - cm

Fig 1.2 Epitaxial growth

iii. Oxidation

• A SiO2 layer of thickness

kness of the order 0.02-2µcm is grown on the

he n-epitaxial

n

layer.

Step 3

N – epi layer

yer 0.1

0. – 0.5 Ω - cm 5 – 25 µm

p – Type substr

substrate 10 Ω - cm

Fig 1.3 Oxidation

12

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

iv. Isolation layer:

• In the circuit, four components

compo have to be fabricated, so we require

equired four island

which are isolated(four

(four components

c are resistor, transistor, capacito

pacitor, diode)

Fig 1.4 Isolation layer

• For this, SiO2 is removed

moved from five different places using Photolitho

tolithography.

• The wafer is next subjected

subjec to heavy p-type diffusion for a long

ng time

tim interval so

that p-type impurities

ties penetrate

pe the n-type epitaxial layer and reach

reac the p-type

substrate.

v. Base Diffusion:

• A new SiO2 layer is grown

gr over entire pattern and a new pattern

attern of opening

formed using photolitho

tolithography technique.

• Now p-type impurities

rities such as Boron is diffused into the region

regio of n-type

epitaxial silicon the

e diffusion

diffu of p-type silicon should be such that it should not

penetrate through n-laye

layer to the substrate.

Fig 1.5 Base diffusion

vi. Emitter Diffusion :

• A new type of SiO2 layer

laye is grown over the entire wafer and selec

selectively etched

to open a new set of win

windows and n-type impurity is diffused throug

through them.

• This forms the transisto

nsistor emitter and cathode region.

13

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 1.6 Emitter diffusion

The reason for using

ng hea

heavily doped n-region can be explained as follows:

fo

• Aluminum normal

ormally used for making interconnection, is a p-type

p impurity

in silicon and

nd can

ca produce an unwanted rectifying contac

ontact with lightly

doped n-material.

terial.

• avy cconcentration of Phosphorous (n+) layer

However heavy er makes

ma a good

ohmic contact

ct with

wit Al-layer. Hence it is desirable to use

e heavily

heav doped n-

region.

vii. Aluminium Metallization:

tion:

• Now the IC chip

ip is complete

c with all active and passive devic

devices and only

interconnection betwe

between the various components have to be

e made.

ma

• Then a thin coating

ting o

of Al is vacuum deposited over the entire

tire su

surface of the

wafer.

• The interconnection

ction between the components is then formed

forme by photo

resistive techniques.

ques.

• The undesired Al areas

are are etched away leaving a pattern

rn interconnection

inte

between transistor,

tor, re

resistor, diode, and capacitor is shown below.

below

Fig 1.7 Aluminium metallization

14

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

2. Explain the various methods of fabricating diodes and capacitors in

monolithic integrated circuits. (April/May 2015)

Fabrication of Diode:

• Diodes find extensive use in Integrated Circuits. The integrated diode is

used as Schottky Barrier Diode. The other name of this diode is metal

semiconductor diode.

• The metal to semiconductor junction can be ohmic as well as rectifying. The

ohmic contact is used when a load is to be attached to a semiconductor

device. This rectifying conduct is called as a metal semiconductor diode.

• Aluminum is a p-type impurity in silicon. The ohmic contact will be formed

between Al and n-type silicon and no pn junction is formed.

• The metal contacts are required to be ohmic and no PN junctions to be

formed between the metal and silicon layers.

• The N+ diffusion region serves the purpose of generating ohmic contacts.

• On the other hand, if aluminum is deposited directly on the N-type silicon,

then a metal semiconductor diode can be said to be formed.

• Such a metal semiconductor diode junction exhibits the same type of V-I

Characteristics as that of an ordinary PN junction.

• The cross sectional view and symbol of a Schottky barrier diode as shown

in figure. Contact 1 shown in figure is a Schottky barrier and the contact 2 is

an ohmic contact.

• The contact potential between the semiconductor and the metal generated

a barrier for the flow of conducting electrons from semiconductor to metal.

15

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

• When the junction is forward biased this barrier is lowered and the electron

flow is allowed from semiconductor to metal, where the electrons are in

large quantities.

• The majority carriers carry the conduction current in the Schottky diode

whereas in the PN junction diode, minority carriers carry the conduction

current and it incurs an appreciable time delay from ON state to OFF state.

• This is due to the fact that the minority carriers stored in the junction have

to be totally removed.

Integrated Capacitor:

• Monolithic capacitors are not frequently used in integrated circuits since they

are limited in the range of values obtained and their performance.

• The capacitance is proportional to the area of the junction and inversely

proportional to the depletion thickness.

C α A, where a is the area of the junction and

C α T, where t is the thickness of the depletion layer

There are, however, two types available,

i) The junction capacitor (ii)MOS and thin film capacitor

Junction Capacitor:

• In monolithic ICs junction capacitor is a reverse biased PN junction formed

by the collector-base or emitter-base diffusion of the transistor. Figure

shows the cross sectional view the junction capacitor and the equivalent

circuit.

Fig 1.9 Junction capacitor & its equivalent circuit

• There are two junctions in the diffused capacitor. They are J1 and J2. The

two diodes are idealized diodes.

16

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

• The parasitic capacitance C1 is inevitable due to the junction J1 between n-

type epitaxial layer and the substrate.

• The substrate must be held at the most negative point in the circuit to

minimize C1.

• During the reverse biased condition J2 will produce the desired capacitance.

• The value of the capacitance C2 will depends upon the area of the junction,

impurity concentration of the n-type epitaxial layer and the voltage across

the junction.

• The capacitor C2 is polarized and is obtained only when the junction J2 is

reverse biased.

MOS and Thin film capacitor:

• Commonly used capacitor is the metal oxide semiconductor capacitor,

the cross sectional view and the equivalent circuit is,

Fig 1.10 MOS and Thin film capacitor

• It is basically a parallel plate capacitor with SiO2 as the dielectric. During

emitter diffusion the heavily doped n+ region formed in the lower plate.

The thin film Al metallization is formed in upper plate of the capacitor with

SiO2 as the dielectric.

• In the equivalent circuit, the parasitic effect consist of a small series

resistance R due to n+ region, a collector substrate junction J1 and its

associated capacitance C1.

Thin film Capacitors:

• Thin film capacitors structures used in thin dielectric film layer between two

metal layers.

17

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

• It requires additional masking and deposition steps beyond the MOS

structure. In thin film structure aluminum or tantalum is used as capacitor

plates Al2O5 or Ta2O5 as dielectric material.

• Ta2O5 is preferred for large value of capacitors. This is a destructive and

irreversible failure mechanism and may require over voltage protection.

Disadvantage:

• Thin film capacitor fails when the voltage rating exceeds due to breakdown

of the dielectric.

3. Completely describe in detail the various stages involved in the

fabrication of a R and FET in a single chip. (April/May 2015)

Integrated Resistors:

• A resistor in a monolithic integrated circuit is obtained by utilizing the bulk

resistivity of the diffused volume of semiconductor region. The commonly

used methods for fabricating integrated resistors are

a. Diffused resistor

b. Epitaxial resistor

c. Pinched resistor

d. Thin film techniques.

a. Diffused Resistor:

• The diffused resistor is formed in any one of the isolated regions of epitaxial

layer during base or emitter diffusion processes.

• This type of resistor fabrication is very economical as it runs in parallel to

the bipolar transistor fabrication.

• The N-type emitter diffusion and P-type base diffusion are commonly used

to realize the monolithic resistor.

• The diffused resistor has a severe limitation in that, only small valued

resistors can be fabricated.

• The surface geometry such as the length, width and the diffused impurity

profile determine the resistance value.

• The commonly used parameter for defining this resistance is called the

sheet resistance. It is defined as the resistance in ohms/square offered by

the diffused area.

18

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

• In the monolithic

ic res

resistor, the resistance value is expressed

ed by R = Rs L/W,

where R= resistanc

istance offered (in ohms), Rs = sheet resistance

resist of the

particular fabrication

ication process involved (in ohms/square), L = length

l of the

diffused area and W = width of the diffused area.

• The sheet resistance

istance of the base and emitter diffusion in 200

200Ω/square and

2.2Ω/square respect

spectively.

b. Epitaxial Resistor:

Fig 1.11 Epitaxial resistor

• The N-epitaxial layer

yer ca

can be used for realizing large resistance

ance values. The

figure shows the cross

cross-sectional view of the epitaxial resistor

tor fo

formed in the

epitaxial layer between t two N+ aluminum metal contacts.

een the

c. Pinched resistor:

Fig 1.12 Pinched resistor

• The sheet resistance

nce o

offered by the diffusion regions can be increased

in by

narrowing down itss cros

cross-sectional area. This type of resistance

tance is normally

achieved in the base

se reg

region. Figure shows a pinched base diffused

fused resistor.

• It can offer resistance

nce o

of the order of mega ohms in a comparati

paratively smaller

area.

19

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

• In the structure shown, no current can flow in the N-type material since the

diode realized at contact 2 is biased in reversed direction.

• Only very small reverse saturation current can flow in conduction path for the

current has been reduced or pinched.

• Therefore, the resistance between the contact 1 and 2 increases as the width

narrows down and hence it acts as a pinched resistor.

d. Thin film resistor:

Fig 1.13 Thin film resistor

• The thin film deposition technique can also be used for the fabrication of

monolithic resistors.

• A very thin metallic film of thickness less than 1µm is deposited on the silicon

dioxide layer by vapour deposition techniques.

• Normally, Nichrome (NiCr) is used for this process. Desired geometry is

achieved using masked etching processes to obtain suitable value of resistors.

• Ohmic contacts are made using aluminum metallization as discussed in earlier

sections.

• The cross-sectional view of a thin film resistor as shown in figure. Sheet

resistances of 40 to 400Ω/ square can be easily obtained in this method and

thus 20kΩ to 50kΩ values are very practical.

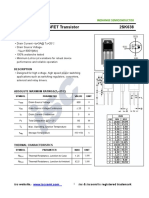

Fabrication of FET:

Unipolar monolithic ICs use JFET or MOSFET as active device .The fabrication

techniques of (i). JFET

(ii). MOSFET

(iii) CMOS is discussed below

JFET Fabrication:

The basic process of JFET Fabrication is same as in BJT fabrication

20

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 1.14 JFET fabrication

• The epitaxial layer whic

which formed the collector of the BJT is used

use as the n-

channel of the JFET. The P+ gate is formed in the n-channell by th

T. Th the process of

plantation. The n+ regions have been formed

diffusion or Ion implanta ed th

the drain and

source contact region

ion to provide good ohmic contact.

4. Explain the proces

rocess involved in the epitaxiall gr

growth and

photolithography. (April/May

(Apr 2015)

Epitaxial Growth:

• Epitaxy is described

d as a

arranged atoms in a single crystal fashion

hion upon

u a single

crystal substrate. The basic

b chemical reaction used for the epitaxi

pitaxial growth of

pure silicon is the hydrog

ydrogen reaction of SiCl4

o

SiCl4+2H2 1200 C Si+4HCL

• In an IC fabrication

tion e

epitaxial films with specific impurity concentration

conce are

required. This is accom

accomplished by introducing phosphine (PH3) for the n-type

Bi-Borane (B2H6) for P

P-type doping into the silicon-tetrachloride

ride hydrogen

h gas

stream.

Fig 1.15 Epitaxial growth

21

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

• The process is carried out in a reaction chamber consisting of a long cylindrical

quartz tube encircled by an RF induction coil.

• The silicon wafers are placed on a rectangular graphite rod called a boat. This

boat is then placed in the reaction chamber where the graphite is heated

inductively to a temperature 12000C.

• The various gases required for the growth of desired epitaxial layers are

introduced into the system through a control console.

Photolithography:

It can be used to produce microscopically small circuit and device patterns on

Si-wafers. Photolithography involves two processes, namely

1. Making of a photographic mask

2. Photo etching

Making of a photographic mask:

It involves the following sequence of operations

1. The preparation of artwork

2. Its reduction

• The initial layout or artwork of an IC is normally done at a scale several hundred

times larger than the final dimension of the finished monolithic circuit. This is

because for a tiny chip more accurate is the final mask. This initial layout is then

decomposed into several mask layers.

• The artwork is usually produced on a precision drafting machine known as

coordinagraph.

• The coordinagraph has a cutting head that can be positioned accurately and

moved along two perpendicular axes.

• The coordinagraph out lines pattern cutting through the red mylar without

damaging the clear layer underneath.

• This rubylith pattern of individual mask is photographed and then reduced in

step by a factor of 5 or 10 several times to finally obtain the exact image size.

• The final image size also must be repeated many times in a matrix array, so

that many ICs will be produced in one process.

• The photo repeating is done with a step and repeat camera. This is an imaging

device with a photographic plate on a removable platform.

22

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Photo etching:

• Photo etching is used for the removal of SiO2 from desired regions so that the

desired impurities can be diffused. The wafer is coated with a film of

photosensitive emulsion (Kodak Photo resist KPR). The thickness of the film in

the range 5000-10000A0

Fig 1.16 (a) Photo etching step 1

• Then the wafer is exposed to ultraviolet light so that KPR becomes polymerized

beneath the transparent regions of the mask.

Fig 1.16 (b) Photo etching step 2

• Then the mask is removed and the wafer is developed using a chemical

(trichloroethylene) which dissolves the unexposed/un polymerized regions, in

the photo resist and leaves the pattern

Fig 1.16 (c) Photo etching step 3

• The polymerized photo resist next fixed or curved, so that it becomes immune

to certain chemicals called etchants used in subsequent processing steps. The

chip is immersed in the etching solution of HCl, which removes the SiO2 from

the area which are not protected by KPR

23

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 1.16 (d) Photo etching step 4

• After diffusion of impurities the photo resist is removed with a chemical solvent

(H2SO4) and mechanical abrasion. This etching process is a wet etching

process and the chemical reagents used are in liquid form.

5. Explain the different IC packages.

MONOLITHIC IC PAKAGE:

There are 3 different package configurations are available they are

1. Metal can package

2. Ceramic flat package

3. Dual-in-line package

METAL CAN or TRANSISTOR PACKAGE:

• The chip is encapsulated in a metal or plastic case. The transistor pack is

available with 3, 5, 8, 10 or 12 pins.

• The metal can package is best suited for power amplifiers because metal is

good heat conductor and consequently has a better dissipation capability than

the flat back or dual-in-line package.

Fig 1.17 Metal can

24

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

• The metal can package permits the use of external heat sink. Most of the

general purpose of Op-Amps comes in 8, 10 or 12 pin packages.

• Voltage regulator ICs such as LM117 has 3-pins. Power Op-Amps and audio

power amplifiers are usually available in 5 pin packages.

CERAMIC FLAT PACKAGE

• The chip is enclosed in a rectangular ceramic case with terminal leads

extending through the sides and ends.

• The flat pack comes with 8, 10, 14 or 16 leads.

• These leads accommodate the power supplies, inputs, outputs and several

special connections required to complete the circuits.

Fig 1.18 Ceramic flat package

DUAL-IN-LINE PACKAGE

• The chip is mounted inside a plastic or ceramic case. The DIP is the most

widely used package type because it can be mounted easily.

• The 8-pin dual-in-line package is called as mini DIPs.

• DIPs are also available with 12, 14, 16 and 20 pins. The density of components

integrated on the same chip increases.

• Digital ICs are DIP packages; Metal can packages are also available with dual-

in-line formed leads (DIL-CAN) and with radial formed leads.

• Different outlines exist within each package style to accommodate various die

sizes and number of pins.

• For Example TO-99, TO-100 and TO-101 are some of the outlines available in

a transistor.

25

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 1.19 Dual-in-line package

26

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

UNIT II

CHARACTERISTICS OF OP-AMP

Part - A

1. What are the advantages of ICs over discrete circuits?

Minimization & hence increased equipment density.

Cost reduction due to batch processing.

Increased system reliability

Improved functional performance.

Matched devices.

Increased operating speeds

Reduction in power consumption

2. What is OPAMP?

An operational amplifier is a direct coupled high gain amplifier consisting of one

or more differential amplifiers, followed by a level translator and an output stage. It is a

versatile device that can be used to amplify ac as well as dc input signals & designed

for computing mathematical functions such as addition, subtraction, multiplication,

integration & differentiation

.3. List out the ideal characteristics of OPAMP?

Characteristics of an ideal operational amplifier:

1. Open loop voltage gain AOL = ∞ (infinity)

2. Input impedance Ri = ∞ (infinity)

3. Output impedance Ro = 0 (zero)

4. Zero offset Vo = 0 (zero)

5. Band width BW = ∞ (infinity)

4.what are the different kinds of packages of IC741?

a) Metal can (TO) package

b) Dual- in- line package

c) Flat package or flat pack

5. What are the assumptions made from ideal op amp characteristics?

• The current drawn by either of the input terminals(non -inverting/inverting)

is negligible.

• The potential difference between the inverting & non- inverting input terminals is

zero.

27

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

6. Mention some of the linear applications of op – amps:

Adder, subtractor, voltage –to- current converter, current –to- voltage

converters, Instrumentation amplifier, analog computation, power amplifier, etc are

some of the linear op-amp circuits.

7. Mention some of the non – linear applications of op-amps:-

Rectifier, peak detector, clipper, clamper, sample and hold circuit, log amplifier,

anti –log amplifier, multiplier are some of the non – linear op-amp circuits.

8. What are the areas of application of non- linear op- amp circuits?

Industrial instrumentation

Communication

Signal processing

9. Define input offset voltage.

A small voltage applied to the input terminals to make the output voltage as

zero when the two input terminals are grounded is called input offset voltage.

10. Define input offset current. State the reasons for the offset currents at the

input of the op-amp.

The difference between the bias currents at the input terminals of the op-amp

is called as input offset current. The input terminals conduct a small value of dc current

to bias the input transistors. Since the input transistors cannot be made identical, there

exists a difference in bias currents.

11. Define CMRR of an op-amp.

The relative sensitivity of an op-amp to a difference signal as compared to a

common –mode signal is called the common –mode rejection ratio. It is expressed in

decibels. CMRR= Ad/Ac

12. Define slew rate.

The slew rate is defined as the maximum rate of change of output voltage

caused by a step input voltage. An ideal slew rate is infinite which means that op-

amp’s output voltage should change instantaneously in response to input step voltage.

13. Why IC 741 is not used for high frequency applications?

IC741 has a low slew rate because of the predominance of capacitance

present in the circuit at higher frequencies. As frequency increases the output gets

distorted due to limited slew rate.

28

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

14. What causes slew rate?

There is a capacitor with- in or outside of an op-amp to prevent oscillation. It is

this capacitor which prevents the output voltage from responding immediately to a fast

changing input.

15. Define thermal drift.

The bias current, offset current & offset voltage change with temperature. A circuit

carefully nulled at 25oC may not remain so when the temperature rises to 35oC.This is

called thermal drift. Often, offset current drift is expressed in nA/oC and offset voltage

drift in mV/oC.

Part - B

1. Explain in detail about the DC characteristics of the OP-AMP.

DC Characteristics of op-amp:

DC output voltages are,

1. Input bias current

2. Input offset current

3. Input offset voltage

4. Thermal drift

1. Input bias current:

The op-amp’s input is differential amplifier, which may be made of BJT or FET.

In an ideal op-amp, we assumed that no current is drawn from the input

terminals.

The base currents entering into the inverting and non-inverting terminals (IB- &

IB+ respectively).

Even though both the transistors are identical, IB- and IB+ are not exactly equal

due to internal imbalance between the two inputs.

Manufacturers specify the input bias current IB

Input bias current IB as the average value of the base currents entering into the

terminals of the op-amp

29

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 2.1 Input bias current

I B+ + I B−

So, IB = V0 = ( I B − ) R f

2 and

Where a compensation resistor Rcomp has been added between the non-inverting input

terminal and ground as shown in the figure below.

Fig 2.2 Bias current compensation

Current IB+ flowing through the compensating resistor Rcomp, then by KVL we get,

-V1 + 0 + V2 -Vo = 0 (or)

Vo = V2 – V1 (1)

By selecting proper value of Rcomp, V2 can be cancelled with V1 and the Vo = 0. The

value of Rcomp is derived a

V1 = IB+ Rcomp (or)

IB+ = V1/Rcomp (2)

The node ‘a’ is at voltage (-V1). Because the voltage at the non-inverting input terminal

is (-V1). So with Vi = 0 we get,

I1 = V 1 / R 1 (3)

30

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

I2 = V2 / Rf (4)

For compensation, Vo should equal to zero (Vo = 0, Vi = 0). i.e. from equation (1) V2 =

V1. So that,

I2 = V1 / Rf (5)

KCL at node ‘a’ gives,

IB- = I2 + I1

f / fa

A= − V1 V1 ( R1 + R f )

1 + ( f / fb ) 2 I B = + = V1

R f R1 R1R f

Assume IB- = IB+ and using equation (4) & (8) we get

V1

(R + R ) =

1 f V1

R1R f Rcomp

R1 R f

Rcomp = = R1 R f

R1 + R f

Rcomp = R1 || Rf (6)

i.e. to compensate for bias current, the compensating resistor, Rcomp should be equal

to the parallel combination of resistor R1 and Rf.

2. Input offset current:

Bias current compensation will work if both bias currents IB+ and IB- are equal.

Since the input transistor cannot be made identical. There will always be some

small difference between IB+ and IB-. This difference is called the offset current

|Ios| = IB+ - IB- (1)

Offset current Ios for BJT op-amp is 200nA and for FET op-amp is 10pA. Even with

bias current compensation, offset current will produce an output voltage when Vi = 0.

V1 = IB+ Rcomp (2)

And I1 = V1/R1 (3)

KCL at node ‘a’ gives,

I2 = (IB—I1)

Rcomp

I 2 = ( I B − − I1 ) = I B − − I B + (Sub the value of I2)

R1

Again, V0 = I2 Rf – V1

Vo = I2 Rf - IB+ Rcomp

31

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

R

Vo = I B − − I B+ comp R f − I B+ Rcomp (4)

R1

Substitute the value Rcomp in equation (4) and after algebraic manipulation,

V o = R f I B− − I B+

Vo = R f I 0 s

The offset current can be minimized by keeping feedback resistance small.

Unfortunately to obtain high input impedance, R1 must be kept large.

R1 large, the feedback resistor Rf must also be high, so as to obtain reasonable

gain.

The T-feedback network is a good solution. This will allow large feedback

resistance, while keeping the resistance to ground low (in dotted line).

The T-network provides a feedback signal as if the network were a single

feedback resistor.

Fig 2.3 T-network

3. Input offset voltage:

• Inspite of the use of the above compensating techniques, it is found that the

output voltage may still not be zero with zero input voltage [Vo ≠ 0 with Vi = 0].

• This is due to unavoidable imbalances inside the op-amp and one may have to

apply a small voltage at the input terminal to make output (Vo) = 0.

• This voltage is called input offset voltage Vos. This is the voltage required to be

applied at the input for making output voltage to zero (Vo = 0).

32

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 2.4 Input offset voltage & its equivalent circuit

Let us determine the Vos on the output of inverting and non-inverting amplifier. If Vi = 0

(Fig (b) and (c)) become the same as in figure (d). The voltage V2 at the negative input

R1

terminal is given by, V2 = Vo

R1 + R f

R1 + R f

Vo = V2

R1

Rf

Vo = 1 + V2

R1

Vios = Vi − V2 and Vi=0, Vios = 0 − V2 = V2

33

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Rf

Vo = 1 + Vios

R1

This is the output offset voltage of an op-amp in closed loop configuration

4. Thermal drift:

A circuit nulled at 250C may not remain so the temperature rises to 350C.This is called

drift. Bias current, offset current, offset voltage change with temperature.

offset current drift is expressed as nA/oC

offset voltage drift is expressed as mV/oC.

These indicate the change in offset for each degree Celsius change in

temperature.

2. Explain in detail about the AC characteristics of the OP-AMP.

AC Characteristics:

• For small signal sinusoidal (AC) application one has to know the ac

characteristics such as frequency response and slew-rate.

Frequency Response:

• The variation in operating frequency will cause variations in gain magnitude and

its phase angle.

• The manner in which the gain of the op-amp responds to different frequencies

is called the frequency response.

• Op-amp should have an infinite bandwidth Bw = ∞ (i.e) if its open loop gain in

90dB with dc signal its gain should remain the same 90 dB through audio and

onto high radio frequency.

• The op-amp gain decreases (roll-off) at higher frequency what reasons to

decrease gain after a certain frequency reached.

• There must be a capacitive component in the equivalent circuit of the op-amp.

• For an op-amp with only one break (corner) frequency all the capacitors effects

can be represented by a single capacitor C.

• Below fig is a modified variation of the low frequency model with capacitor C at

the o/p.

34

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 2.5 Frequency response equivalent circuit

There is one pole due to R0 C and one -20dB/decade. The open loop voltage gain of

an op-amp with only one corner frequency is obtained from above fig.

− jXc

Vo = AolVd

Ro − jXc

Divide by jXc both numerator and denominator

AolVd

Vo =

Ro (Vin=Vd)

+ 1

− jXc

Vo Aol

=

Vin Ro (Xc=1/2πfc)

1+ j

Xc

Aol

A=

(1 + 2πRoC

Aol

A= (1)

1 + j ( f / f 1)

where f1= 1/2πfRoC

f1 is the corner frequency or the upper 3 dB frequency of the op-amp. The magnitude

and phase angle of the open loop volt gain are fu of frequency can be written as,

Aol

Magnitude A= (2)

1 + ( f / f 1)

2

Phase angle φ = tan −1 ( f / f 1)

(3)

35

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

The magnitude and phase angle characteristics from equations (2) and (3)

• For frequency f<< f1 the magnitude of the gain is 20 log AOL in dB.

• At frequency f = f1 the gain in 3 dB down from the dc value of AOL in dB. This

frequency f1 is called corner frequency.

• For f > > f1 the fain roll-off at the rate off -20dB/decade or -6dB/decade.

Fig 2.6 Frequency response characteristics

From the phase characteristics

the phase angle is zero at frequency f =0.

At the corner frequency f=f1 the phase angle is -450

-900 phase angle occurs at frequency (at f=∞)

The voltage transfer in a S-domain can be written as

Aol Aol

A= =

1 + j ( f / f 1) 1 + j (ω / ω1)

36

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Aol.ω1 Aol.ω1

A= = (4)

jω + ω1 S + ω1

The transfer f0 of as op-amp with 3 break frequency can be assumed as,

Aol

A= 0 < f1< f 2< f3

(1 + jf / f 1)(1 + jf / f 1)(1 + f / f 3)

Aol.ω1.ω 2.ω 3

A= 0<ω1<ω2< ω3

( S + ω1)(S + ω 2)(S + ω 3)

Fig 2.7 Frequency response of op-amp

Slew Rate:

• Another important frequency related parameter of an op-amp is the slew rate.

(Slew rate is the maximum rate of change of output voltage with respect to time.

Specified in V/µs).

Reason for Slew rate:

• There is usually a capacitor within 0, outside an op-amp oscillation.

• It is this capacitor which prevents the o/p voltage from fast changing input.

• The rate at which the volt across the capacitor increases is given by

dVc / dt = I/C (1)

• I = Maximum amount furnished by the op-amp to capacitor C. Op-amp should

have the either a higher current or small compensating capacitors.

• For 741 IC, the maximum internal capacitor charging current is limited to about

15µA. So the slew rate of 741 IC is

37

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

SR = dVc / dt |max = Imax/C.

• For a sine wave input,

put, th

the effect of slew rate can be calculated

d as consider

c volt

follower -> The input

ut is la

large amp, high frequency sine wave.

• If Vs = Vm Sinwt then output V0 = Vm sinwt . The rate of change

hange of output is

given by dV0/dt = Vm w coswt.

Fig

ig 2.8 Input and output waveforms

The max rate of change off outp

output across when coswt =1

(i.e) SR = dV0/dt |max = wVm.

wVm

SR = 2∏fVm V/s = 2∏fVm v/m

v/ms.

Thus the maximum frequency

ency fmax

f at which we can obtain an undistorte

storted output volt

of peak value Vm is given by

fmax (Hz) = Slew rate/6.28

8 * Vm

V .

called the full power response

ponse. It is maximum frequency of a large

ge amplitude

am sine

wave with which op-amp can ha

have without distortion.

3. Explain the operation

tion of

o differentiator and integrator by using

sing OP-AMP.

O

(a) Differentiator:

• One of the simplest

est o

of the op-amp circuits that contains capacitor

capa in the

differentiating amplifier.

lifier.

• As the name implies,

plies, the circuit performs the mathematical

tical o

operation of

differentiation (i.e) the output

ou waveform is the derivative of the input waveform.

• The differentiator may

ay be constructed from a basic inverting amplifi

mplifier if an input

resistor R1 is replaced

ced by a capacitor C1.

38

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 2.9 Differentiator circuit

Analysis:

Node N is virtual

rtual g

grounded.

VN = 0

Current iC through

ugh tthe capacitor,

d dV

ic = C1 (Vi − VN ) = C1 i → (1)

dt dt

Current if through

ugh fe

feedback resistor is

V0

if = -----------

------------>(2)

Rf

Apply KCL at node N

ic + i f = 0

dVi V0

C1 + =0

dt R f

dVi

V0 = − R f C1 -----------------

------>(3)

dt

Thus the output V0 is equal

al to RF C1 times the negative rate of change of th

the input

voltage Vin with time.

The –sign indicates a 1800 phase

ph shift of the output waveform V0 with

ith respect

re to the

input signal.

Phasor equivalent of output

ut vol

voltage is

V0 ( S ) = − R f C1.SVi ( S )

39

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

V0

A= = R f C1S = jω R f C1 = ω R f C1

Vi

f 1

A= where fa =

fa 2π R f C1

(2)

Input and Output Waveforms:

rms:

Fig

ig 2.10 Input and output waveforms

The input signal will be differen

ifferentiated properly, if the time period T of the input

in signal is

larger than or equal to RF C1 (i.e)

(i.e T > RF C1

40

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

(b) Integrator:

• A circuit in which the

e out

output voltage waveform is the integral off the iinput voltage

waveform is the integrato

tegrator or Integration Amplifier.

• Such a circuit is obtained

tained by using a basic inverting amplifier config

configuration if the

feedback resistor RF is re

replaced by a capacitor CF .

Fig 2.11 Integrator circuit

Analysis:

Let Vin is the input voltage appli

applied to the inverting terminal

Current through Capacitor Cf= C

Current through Ri

Vin − VB d

= C f (VB − Vo ) (1)

Ri dt

(∴VB = VA = 0)

Vin d

(1)-------------> = C f Vo

Ri dt

d 1

Vo = − Vin

dt Ri C f

1

Ri C f ∫

Vo = − Vin dt (2)

Equation (2) indicates thatt the output is directly proportional to the negativ

egative integral of

the input volts and inversely

ely pro

proportional to the time constant R1 CF . In phasor

ph method

the output voltage can be writte

written as

41

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

R f / Ri

A=− 1

(1 + jf / f a ) Vo ( s ) = − Vi ( s )

sR1C f

H ( jω ) = R f / Ri

In steady state, put s = jω and we

w get

1

Vo ( jω ) = − Vi ( jω )

jω R1C f

So the magnitude of the gain

ain or integrator transfer function is

Vo ( jω ) 1 1

A= =− =

Vi ( jω ) jω R1C f ω R1C f

Ex: If the input is sine wave ->

> output

o is cosine wave.

If the input is square wave ->

> output

ou is triangular wave.

Fig 2.12 Input and output waveforms

• These waveform with

ith as

assumption of R1 Cf = 1, Vout = 0V (i.e) C = 0.

42

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

• When Vin = 0 the integrator works as an open loop amplifier because the

capacitor CF acts an open circuit to the input offset voltage Vio. (Or)

• The Input offset voltage Vio and the part of the input is charging capacitor CF

produce the error voltage at the output of the integrator.

4. Explain in detail about differential amplifier using op-amp.

• The op-amp amplifies the difference between the two input signals is called

differential amplifier. Classify these arrangements according to the number of

op-amps used. i.e

1. Differential amplifier with one op-amp

2. Differential amplifier with two op-amps.

• Differential amplifiers are used in instrumentation and industrial applications to

amplify differences between 2 input signals such as output of the wheatstone

bridge circuit.

• Differential amplifier preferred to these application because they are better able

to reject common mode (noise) voltages than single input circuit such as

inverting and non-inverting amplifier.

1. Differential Amplifier with one op-amp:

Figure shows the differential amplifier with one op-amp.

Fig 2.13 Differential amplifier circuit with 1 op-amp

To analyze this circuit by deriving voltage gain and input resistance. This circuit is a

combination of inverting and non-inverting amplifier. (i.e)

• When Vx is reduced to zero the circuit is non-inverting amplifier and

• When Vy is reduced to zero the circuit is inverting amplifier.

43

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Voltage Gain:

The circuit has 2 inputs Vx and Vy . Use superposition theorem, when Vy = 0V,

becomes inverting amplifier. Hence the output due to Vx only is

−R f (Vx )

Vox =

R1

Similarly, when Vx = 0V, becomes Non-inverting amplifier having a voltage divider

network composed of R2 and R3 at the Non – inverting input.

R3 (Vy )

V1 =

R2 + R3

And the output due to Vy then is

R

Voy = 1 + f V1

R1

Note: the gain of the differential amplifier is same as that of inverting amplifier.

Input Resistance:

The input resistance Rif of the differential amplifier is resistance determined looking

into either one of the 2 input terminals with the other grounded,

With Vy = 0V,

Inverting amplifier, the input resistance which is,

RiFx ≈ R1 (1)

Similarly Vx = 0V,

Non-inverting amplifier, the input resistance which is,

RiFy ≈ (R2 + R3) (2)

• Vx and Vy are not the same. Both the input resistance can be made equal, if we

modify the basic differential amplifier. R1 and (R2 + R3) can be made much

larger than the source resistances. So that the loading of the signal sources

does not occur.

Note: If we need a variable gain, we can use the differential amplifier. In this circuit

R1 = R2 , RF = R3 and the potentiometer Rp = R4.Depending on the position of the

wiper in R voltage can be varied from the closed loop gain of -2RF /R1 to the open loop

gain of A.

44

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 2.14 Differential amplifier circuit with 1 op-amp i/p resistance

2. Differential Amplifier with 2 op-amps:

We can increase the gain of the differential amplifier and also increase the

input resistance Rif if we use 2 op-amps.

Voltage gain:

It is composed of 2 stages 1. Non-inverting amplifier 2. Differential amplifier with gain.

Fig 2.15 Differential amplifier circuit with 2 op-amps

By finding the gain of these 2 stages, we can obtain the overall gain of the circuit, The

o/p

R

V2 = 1 + 3 V y − − − − − − − − − −− > (1)

R2

By applying superposition theorem to the second stage, we can obtain the output

voltage,

Rf Rf

V0 = − V2 + 1 + V x − − − −− > (2)

R1 R1

45

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Sub. The value of V2 in eqn. (2)

R f R3 R

V0 = − 1 + V y + 1 + f Vx − − > (3)

R1 R2 R1

Since R1=R3 and Rf=R2

Rf

V0 = 1 + (Vx − V y )

R1

R3 R1 + R f

V0 y = V y − − − − − − − −− > (4)

R2 + R3 R1

Since R1=R2 and Rf=R3

Rf

Voy = V y − − − − − − − − − − − − − − − − − −− > (5)

R1

From eqn.(1) and (5) the net output voltage is,

V0 = V0 x + Voy

Rf

V0 = − (V x − Vy )

R1

Rf

V0 = − (V ) xy

R1

Or the output voltage gain,

V0 Rf

AD = =−

V xy R1

The gain of the differential amplifier is same as that of the inverting amplifier.

5. Explain in detail about inverting and non inverting operational amplifier?

Inverting Amplifier:

• An amplifier which provides a phase shift of 1800 between the input and the

output is called as inverting amplifier. The basic circuit diagram of inverting

amplifier is shown below

46

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 2.16

2. Inverting amplifier circuit

Analysis:

Current through the resistance

tance R is,

Vin − V A

I= [VA=VB=0 Virtual ground]

R1

Vin

I=

R1

Current through RF is,

V A − V0 V

I= =− 0

RF RF

Vin V

=− 0

RF RF

V0 R

A= =− F

Vin R1

RF/R1 is called gain of amplifier

plifiers. Negative sign indicates that polarity of the output is

opposite to that of the input.

ut. So the inverting amplifier is also called ass sign changer.

Sign Changer:

Let K= RF/R1 is called scale factor.

V0=-KVin

Since the output voltage iss chan

changing according to the scale factor K and input

in voltage

Vin the inverting amplifier is cal

called as Scale changer. The input and output

utput waveforms

are shown below

47

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 2.17 Inverting amplifier waveforms

If the value of RF/R1=1, then the output is exactly 1800 phase shift with

en th ith respect

res to the

input. Hence it is called ass Phas

Phase shift circuit (or) phase inverter.

Non-inverting amplifier:

• An amplifier which amplifies

ampli the input without any phase shift betwe

between them is

called a non-inverting

ing am

amplifier.

The basic circuit diagram is sho

shown below

Fig 2.18 Non-inverting amplifier circuit

Analysis:

I through R1 is,

V − VA

I=

R1

Vin

I= −

R1

48

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Current through RF is,

V A − V0 Vin − V0

I= =

RF RF

Vin Vin V0

− = −

R1 R F RF

V0 Vin Vin

= −

R1 R1 R F

V0 Vin R F

= 1 +

Vin RF R1

V R

A = 0 = 1+ F

Vin R1

The above equation is called

lled as the gain for non-inverting amplifier.

The input and output waveform

eforms are shown below.

Fig 2.19

.19 N

Non-Inverting amplifier waveforms

Applications of op-amp:

It is classified into 2 types,

• Linear application

• Non-linear Application

49

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

6. Explain the basic appli

applications of op-amp?

Summing Amplifier:

Op-amp may be used

sed tto design a circuit whose output is the

e sum of several

input signals. Such a circuit

uit is ccalled a summing amplifier or a summer.

Adder is classified as

Inverting summer

mmer

Non-inverting

g summer

sum

Inverting Summing Amplifier:

lifier:

In this circuit all the inputt signals

signa to be added are applied to the inverting

verting terminal of

the op-amp. The circuit with two

tw input signals V1, V2 , input resistors

tors R1, R2 and a

feedback resistor Rf is shown

own in figure

Fig 2.20

.20 Inverting

In summing amplifier circuit

As point B is grounded

nded, due to virtual ground concept the node A is also at

virtual ground potential.VA=0

Now from the inputt side

V1 − V A V1

I1 = = − − − − − − − − − −− > (1)

R1 R1

V2 − V A V 2

I2 = = − − − − − − − − − −− > (2)

R2 R2

Applying KCL at node

de A and as input op-amp current is zero,

I=I1+I2 ------------------------

------------------------>(3)

From the output side

V A − V0 V

I= = − 0 − − − − − − − − − − > ( 4)

Rf Rf

50

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Substitute eqn.(1), (2), (4)

(4 in eqn.(3)

− V0 V1 V2

= + − − − − − − − − − − − −− > (5)

Rf R1 R2

Rf Rf

V0 = − V1 + V 2 − − − − − − − − > ( 6)

R1` R2

If the three resistance

ce ar

are equal R1= R2= Rf

V 0 = − (V1 + V 2 )

By properly selecting Rf , R1 and R2 we can have weighted addition

dition of the input

signals like aV1+aV2 as indicat

ndicated in eqn(6)

Non-Inverting Summing Amplifier:

Amp

Here the input signals

nals to be added and applied to the non-inverting

verting terminal of

the op-amp. The circuit diagram

iagram is shown in figure

Fig 2.21 Non

Non-Inverting summing amplifier circuit

Analysis:

Let the voltage of node B is VB . Now the node A is at the same potential

tential as that of B

due to virtual ground.

VA=VB------------------------

------------------>(1)

From the input side

V1 − V B

I1 = − − − − − − − − − −− > (2)

R1

V2 − V B

I2 = − − − − − − − − − −− > (3)

R2

Input current of op-amp is zero

I1 + I2 = 0--------------------

--------------------->(4)

51

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

V1 − VB V2 − VB

+ =0

R1 R2

V1 V2 1 1

+ = VB +

R1 R2 R1 R2

R V + R1V2

VB = 2 1 − − − − − − − − > (5)

R + R2

Now at node A

V A VB

I= = − − − − − − − − − −− > (6)

R R

and

V0 − V A V0 − V B

I= = − − − −− > (7)

Rf Rf

Equqting eqn. (6) and (7)

R + Rf

V0 = V B − − − − − − − − > (8)

R

Substitute eqn.(5) in (8)

R2 (R + R f ) R1 (R + R f )

V0 = V1 + V2 − − > (9)

R(R1 + R2 ) R(R1 + R2 )

The eqn(9) shows that the output is weighted some of the inputs.

If R1 = R2 = R = Rf we get

V0=V1+V2

Subtractor:

• A basic differential amplifier can be used as a subtractor as shown in the above

figure. If all resistors are equal in value, then the output voltage can be derived

by using superposition principle.

52

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 2.22 Subtractor amplifier circuit

To find the output V01 due to V1 alone, make V2 = 0.

Then the circuit of figure as shown in the above becomes a non-inverting

amplifier having input voltage V1/2 at the non-inverting input terminal and the output

becomes

V1 R

V01 = 1 + = V1 − − − − − − − − − −− > (1)

2 R

Similarly the output V02 due to V2 alone (with V1 grounded) can be written

simply for an inverting amplifier as

R

V02 = − V2 = −V2 − − − − − − − − − − − −− > (2)

R

Thus the output voltage Vo due to both the inputs can be written as

V0 = V01 + V02

V0 = V1 − V2

Thus the output voltage is the difference between the two inputs and hence it act as

the subtractor.

53

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

UNIT-III

APPLICATIONS OF OPAMP

Part – A

1. What is the need for an instrumentation amplifier?

In a number of industrial and consumer applications, the measurement of physical

quantities is usually done with the help of transducers. The output of transducer has to

be amplified So that it can drive the indicator or display system. This function is

performed by an instrumentation amplifier.

2. What is a sample and hold circuit? Where it is used?

A sample and hold circuit is one which samples an input signal and holds on to its last

sampled value until the input is sampled again. This circuit is mainly used in digital

interfacing, analog to digital systems, and pulse code modulation systems.

3. What is a comparator?

A comparator is a circuit which compares a signal voltage applied at one input of an

opamp with a known reference voltage at the other input. It is an open loop op - amp

with output ± Vsat .

4. What is a multivibrator?

Multivibrators are a group of regenerative circuits that are used extensively in timing

applications. It is a wave shaping circuit which gives symmetric or asymmetric square

output. It has two states either stable or quasi- stable depending on the type of

multivibrator.

5. Draw the circuit of log amplifier using op-amps

54

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

6. Draw the circuit of log amplifier using op-amps

7. What is a zero crossing detector?

Zero crossing detector(ZCD) is a voltage comparator that switches the output between

+Vsat and –Vsat. The output is driven into –Vsat when the input signal passes through

zero to positive direction. Conversely, when input signal passes through zero to

negative direction, the output switches to +Vsat.

8. What are the applications of comparator?

• Zero crossing detectors

• Window detector

• Time marker generator

• Phase detector

9. Define conversion time.

It is defined as the total time required converting an analog signal into its digital output.

It depends on the conversion technique used & the propagation delay of circuit

components. The conversion time of a successive approximation type ADC is given by

T (n+1) where T---clock period Tc---conversion time n- no. of bits.

10. What are the different types of filters?

• Based on functions: Low pass filter, High pass filter, Band pass filter, Band

reject filter

• Based on order of transfer function : first, second, third higher order filters.

• Based on configuration: Bessel, Chebychev, Butterworth filters.

55

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Part - B

1. Draw and explain the working of Instrumentation amplifier using Op-Amp

and derive its output voltage equation.

• In a number of industrial and consumer applications, one is required to measure

and control physical quantities.

• Some typical examples are measurement and control of temperature, humidity,

light intensity, water flow etc. these physical quantities are usually measured

with help of transducers.

• The output of transducer has to be amplified so that it can drive the indicator or

display system.

• This function is performed by an instrumentation amplifier.

• The important features of an instrumentation amplifier are

high gain accuracy

high CMRR

high gain stability with low temperature coefficient

low output impedance

• There are specially designed op-amps such as µA725 to meet the above stated

requirements of a good instrumentation amplifier.

• Monolithic (single chip) instrumentation amplifier are also available

commercially such as AD521, AD524, AD620, AD624 by Analog Devices,

LM363.XX (XX -->10,100,500) by National Semiconductor and INA101, 104,

3626, 3629 by Burr Brown.

Fig 3.1 Basic differential amplifier circuit

Consider the basic differential amplifier,

The output voltage Vout is given by,

56

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

R2 1 R

V0 = − V2 + V1 1 + 2

R1 R R1

1+ 3

R4

+ R4

V = V1

R3 + R4

R 1 R1

V0 = − 2 V2 − + 1V1

R1 R R2

1+ 3

R4

R1 R3

For = we obtain

R2 R4

R2

V0 = (V1 − V2 )

R1

• In the circuit of figure 6(a), source V1 sees an input impedance = R3+R4 (=101K)

and the impedance seen by source V2 is only R1 (1K).

• This low impedance may load the signal source heavily.

• Therefore, high resistance buffer is used preceding each input to avoid this

loading effect as shown in figure 6(b).

• The op-amp A1 and A2 have differential input voltage as zero. For V1=V2, that is,

under common mode condition, the voltage across R will be zero.

Fig 3.2 Instrumentation amplifier circuit

57

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

As no current flows through R and R’ the non-inverting amplifier. A1 acts as voltage

follower, so its output

V2’=V2.

Similarly op-amp A2 acts as voltage follower having output

V1’=V1.

However, if V1≠V2, current flows in R and R’, and (V2’-V1’)>(V2-V1). Therefore, this

circuit has differential gain and CMRR more compared to the single op-amp circuit of

figure 6(a).

The output voltage Vo can be calculated as follows

R2V1'

The voltage at the (+) input terminal of op-amp A3 is . Using superposition

R1 + R2

theorem, we have,

R2 ' R2 R2V1'

V0 = − V2 + 1 +

R1 R1 R1 + R2

=−

R1

(

R2 '

)

V1 − V2' ---------------->(1)

Since, no current flows into op-amp, the current I flowing (upwards) in R is

I = (V1-V2)/R and passes through the resistor R’.

R'

V1' = R ' I + V1 = (V1 − V2 ) + V1

R

R'

And V2' = − R ' I + V2 = − (V1 − V2 ) + V2

R

Putting the values of V1’ and V2’ in equation (1), we obtain,

R2 2 R '

V0 = (V1 − V2 ) + (V1 − V2 )

R1 R

R2 2 R '

V0 = 1 + (V1 − V2 ) ----------------->(2)

R1 R

In equation (2), if we choose R2 = R1 = 25K (say) and R’ = 25K; R = 50Ω, then a

gain=1001

The difference gain of this instrumentation amplifier R, however should never

be made zero, as this will make the gain infinity. To avoid such a situation, in a

practical circuit, a fixed resistance in series with a potentiometer is used in place of R.

58

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 3.3 Instrumentation amplifier practical circuit

• Figure 3.3 shows a differential instrumentation amplifier using Transducer

Bridge. The circuit uses a resistive transducer whose resistance changes as a

function of the physical quantity to be measured.

• The bridge is initially balanced by a dc supply voltage Vdc so that V1=V2. As the

physical quantity changes, the resistance RT of the transducer also changes,

causing an unbalance in the bridge (V1≠V2). This differential voltage now gets

amplified by the three op-amp differential instrumentation amplifier.

Applications:

• Temperature indicator

• Temperature controller

• Light intensity meter

2. With a neat circuit diagram, explain the working of Schmitt trigger using

Op-Amp. (May 2015)

Schmitt Trigger:

Fig 3.4 Schmitt trigger circuit

59

Visit & Downloaded from : www.LearnEngineering.in

EE8451 - LIC Visit & Downloaded from : www.LearnEngineering.in

Fig 3.5 Schmitt trigger circuit waveforms

• This circuit converts an irregular shaped waveform to a square wave or pulse.

The circuit is known as Schmitt Trigger or squaring circuit.

• The input voltage Vin triggers (changes the state of) the o/p V0 every time it

exceeds certain voltage levels called the upper threshold Vut and lower

threshold voltage.

• These threshold voltages are obtained by using theh voltage divider R1 – R2,

where the voltage across R1 is feedback to the (+) input.

• The voltage across R1 is variable reference threshold voltage that depends on

the value of the output voltage.