Professional Documents

Culture Documents

Final Term 1

Final Term 1

Uploaded by

Malik Kashif0 ratings0% found this document useful (0 votes)

3 views1 pageOriginal Title

Final Term 1 .docx

Copyright

© © All Rights Reserved

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

3 views1 pageFinal Term 1

Final Term 1

Uploaded by

Malik KashifCopyright:

© All Rights Reserved

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 1

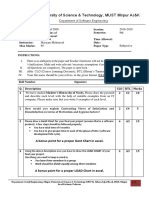

Institute of Southern Punjab Multan

Department of Computer Science & IT

Final Term Examination

Subject: Digital Logic & Design

Class: BSCS Semester: 1st

Instructor: Muhammad Kashif Date: 15-3-2019

Paper Type: Time 180 Min

Allowed:

Instructions: (Read Carefully)

●Read Question Paper carefully . ●Donot Write anything on Question Paper except your Registration

No and Name. ●Make sure your mobile phone is switched off. ●Any unauthorized material found

after examinations starts will be regarded as possible evidence of cheating or attempting to do so. ●

Avoid cutting / Overwriting

ATTEMPT

Q1: Give short answers of given Questions (Compulsory). Objective Marks : 10

1. What is the difference between flip flop and Register ?

2. What is the difference between static RAM and dynamic RAM ?

3. Describe the master slave JK Flip Flop ?

4. Explain Register Types with the help of Diagram ?

5. Explain the difference between high level and low level triggering ?

Briefly Explain given question (Attempt any 4 questions). Subjective Marks : 40

Q2: Define counter and also Design a counter to produce the following sequence. Use J-K flip-flops.

{ 00, 10, 01, 11, 00, …. }

Q3 : Define PLA and also Draw a PLA circuit to implement the functions F1 = A’B + AC + A’BC’ ,

F2 = (AC + AB + BC)’

Q4 : Define ROM and Tabulate the truth table for an 8 * 4 ROM that implements the Boolean

functions . A(x, y, z) = ∑(0, 3, 4, 6) , B(x, y, z) = ∑(0, 1, 4, 7), C(x, y, z) = ∑(1, 5)

D(x, y, z) = ∑(0, 1, 3, 5, 7)

Q5 : Define PAL and also draw the PAL for given SOP. A(x, y, z) = ∑(0, 3, 4, 6),

B(x, y, z) = ∑(0, 1, 4, 7), C(x, y, z) = ∑(1, 5)

Q6: Design Mealy Machine for given Diagram.

Page |1

You might also like

- National Cyber Olympiad - Class 9 (With CD): Theories with examples, MCQs & solutions, Previous questions, Model test papersFrom EverandNational Cyber Olympiad - Class 9 (With CD): Theories with examples, MCQs & solutions, Previous questions, Model test papersRating: 3 out of 5 stars3/5 (1)

- Python Quick Interview Guide: Top Expert-Led Coding Interview Question Bank for Python Aspirants (English Edition)From EverandPython Quick Interview Guide: Top Expert-Led Coding Interview Question Bank for Python Aspirants (English Edition)No ratings yet

- 1st Year Computer Science Chapter WiseDocument11 pages1st Year Computer Science Chapter Wiseasifalimsm100% (2)

- Institute of Southern Punjab Multan: Department of Computer Science & ITDocument1 pageInstitute of Southern Punjab Multan: Department of Computer Science & ITMalik KashifNo ratings yet

- Final Term 2Document1 pageFinal Term 2Malik KashifNo ratings yet

- Institute of Southern Punjab Multan: Department of Computer Science & ITDocument1 pageInstitute of Southern Punjab Multan: Department of Computer Science & ITMalik KashifNo ratings yet

- Final Term 3Document1 pageFinal Term 3Malik KashifNo ratings yet

- Institute of Southern Punjab Multan: Department of Computer Science & ITDocument1 pageInstitute of Southern Punjab Multan: Department of Computer Science & ITMalik KashifNo ratings yet

- Institute of Southern Punjab Multan: Department of Computer Science & ITDocument1 pageInstitute of Southern Punjab Multan: Department of Computer Science & ITMalik KashifNo ratings yet

- Design & Analysis PDFDocument2 pagesDesign & Analysis PDFzia hussainNo ratings yet

- Institute of Southern Punjab Multan Online Examination: Department of Computer ScienceDocument4 pagesInstitute of Southern Punjab Multan Online Examination: Department of Computer ScienceAqeel Asghar pansotaNo ratings yet

- Assignment N0. 01: Instructions (Any) : Submit in The Hardcopy Submission InstructionsDocument1 pageAssignment N0. 01: Instructions (Any) : Submit in The Hardcopy Submission InstructionsUmer SalmanNo ratings yet

- Punjab Technical University: Scheme & Syllabus of B. Tech. Computer Science & Engineering (CSE)Document57 pagesPunjab Technical University: Scheme & Syllabus of B. Tech. Computer Science & Engineering (CSE)tornado2307No ratings yet

- Feedback: Written TestDocument2 pagesFeedback: Written TestSaiGoutham SunkaraNo ratings yet

- ATC 17CS54 Module 5 Assignment QsDocument2 pagesATC 17CS54 Module 5 Assignment QsNitin SinghNo ratings yet

- Oop Lab (Terminal)Document2 pagesOop Lab (Terminal)i am lateNo ratings yet

- 2015 Batch Online Written TestDocument9 pages2015 Batch Online Written TestWINORLOSENo ratings yet

- Oop Lab (Terminal)Document2 pagesOop Lab (Terminal)i am lateNo ratings yet

- GC Women University, Sialkot: ObjectiveDocument1 pageGC Women University, Sialkot: ObjectiveMuzalfa KhanNo ratings yet

- 7388 - GCD1105 - ASM1 - Pham Thi Thanh Thien - GCD210520Document26 pages7388 - GCD1105 - ASM1 - Pham Thi Thanh Thien - GCD210520Thanh Thiên Phạm ThịNo ratings yet

- DLD Final Paper TotalDocument17 pagesDLD Final Paper Totalalihassan009669No ratings yet

- Proposed Syllabus by Zubair Khan Garhmukteshwar Bachelors of Computer Application Semester - Wise Breakup of CourseDocument47 pagesProposed Syllabus by Zubair Khan Garhmukteshwar Bachelors of Computer Application Semester - Wise Breakup of Coursemominkhan7764No ratings yet

- UAT FormDocument75 pagesUAT FormPriyanshu KumarNo ratings yet

- Qual Comm 2016Document15 pagesQual Comm 2016Manoj Kumar Gunturi100% (2)

- I PUC Computer ScienceDocument2 pagesI PUC Computer ScienceMelwin SeraNo ratings yet

- ML Course ProspectusDocument7 pagesML Course ProspectusMustafa AliNo ratings yet

- Elec Bluebook 22-23Document61 pagesElec Bluebook 22-23FfhhgghNo ratings yet

- BCADocument47 pagesBCANitin Kumar VatsNo ratings yet

- R18 B.Tech It Iii YearDocument61 pagesR18 B.Tech It Iii YearheelobgeNo ratings yet

- Gujarat Technological University: Semester - III Subject Name: Digital ElectronicsDocument3 pagesGujarat Technological University: Semester - III Subject Name: Digital ElectronicsBhargavsinh ParmarNo ratings yet

- Assignment No. 1 DSDocument4 pagesAssignment No. 1 DSMuhammad AliNo ratings yet

- Mirpur University of Science & Technology, MUST Mirpur AJ&K: InstructionsDocument2 pagesMirpur University of Science & Technology, MUST Mirpur AJ&K: InstructionsKamran FarooqNo ratings yet

- Mirpur University of Science & Technology, MUST Mirpur AJ&K: InstructionsDocument2 pagesMirpur University of Science & Technology, MUST Mirpur AJ&K: InstructionsKamran FarooqNo ratings yet

- CS501 Final Fall2004Document3 pagesCS501 Final Fall2004asifa amanatNo ratings yet

- CS302 Collection of Old PapersDocument48 pagesCS302 Collection of Old Paperscs619finalproject.comNo ratings yet

- Sem5 EJ5EDocument38 pagesSem5 EJ5EAjit SinghNo ratings yet

- SPA Midsem Paper02Document1 pageSPA Midsem Paper02sibreibtNo ratings yet

- University THE PUNJAB... : SemesterDocument22 pagesUniversity THE PUNJAB... : SemesterUmer KhalilNo ratings yet

- Annual Examination Paper Computer Operator - 015Document1 pageAnnual Examination Paper Computer Operator - 015Rajeev KashyapNo ratings yet

- Assignment No 3-4Document1 pageAssignment No 3-4Ishaq GhaznaviNo ratings yet

- s20 Rdbms F18-Ma & Ea Lq01Document2 pagess20 Rdbms F18-Ma & Ea Lq01Mansoor ShahbazNo ratings yet

- Bca PDFDocument47 pagesBca PDFShruti Mayank GoelNo ratings yet

- IT - Old Papers - 2019 To 2014Document15 pagesIT - Old Papers - 2019 To 2014Ali RangwalaNo ratings yet

- BCA H FinalDocument49 pagesBCA H FinalManpreet KaurNo ratings yet

- Computer Organization 2Document2 pagesComputer Organization 2Jaibharath AdmnNo ratings yet

- 1st, 3rd 5th Sem IA QuestionDocument3 pages1st, 3rd 5th Sem IA QuestionPartha MandalNo ratings yet

- Mid IIIDocument2 pagesMid IIIRabia BasriNo ratings yet

- Punjab Technical University: Scheme & Syllabus of B. Tech. Computer Science & Engineering (CSE)Document57 pagesPunjab Technical University: Scheme & Syllabus of B. Tech. Computer Science & Engineering (CSE)nehachoudhryNo ratings yet

- IGCSE ICT MCQ Mock 2Document5 pagesIGCSE ICT MCQ Mock 2rahimuddinNo ratings yet

- BE IT 5th Semester (Batch 2015)Document25 pagesBE IT 5th Semester (Batch 2015)ANIKET SHARMANo ratings yet

- Be Mba Ece 2014 15Document96 pagesBe Mba Ece 2014 15abcd_123425No ratings yet

- PGDCA SyllabusDocument38 pagesPGDCA SyllabusbharathindarapuNo ratings yet

- Ass 1Document1 pageAss 1Rosy WaliaNo ratings yet

- Birla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionDocument4 pagesBirla Institute of Technology and Science, Pilani Pilani Campus Instruction DivisionTrideeb BhattacharyaNo ratings yet

- MCA PapersDocument769 pagesMCA PapersJayesh WaghNo ratings yet

- cs2 11 Syllabus and Paper PatternDocument1 pagecs2 11 Syllabus and Paper PatternShlok ParekhNo ratings yet

- MCA III Semester IGNOU AssignmentDocument12 pagesMCA III Semester IGNOU AssignmentMayur AsodariyaNo ratings yet

- Krishna: & Kanta Handiqui Open UniversityDocument6 pagesKrishna: & Kanta Handiqui Open UniversityMridupaban DuttaNo ratings yet

- Bca 3 Sem PC Assembly and Troubleshooting 93334 Jan 2023Document2 pagesBca 3 Sem PC Assembly and Troubleshooting 93334 Jan 2023Taha UzairNo ratings yet

- Final Term Seqs Dccn-w2021Document2 pagesFinal Term Seqs Dccn-w2021shoaibakbar516No ratings yet

- Institute of Southern Punjab Multan Online Examination: Read Instructions Carefully Before Attempting Questions PaperDocument2 pagesInstitute of Southern Punjab Multan Online Examination: Read Instructions Carefully Before Attempting Questions PaperMalik KashifNo ratings yet

- City College of Science and Commerce Test No:9 Subject: Computer Science Class: ICS 1 Year Student Name: - Roll NoDocument4 pagesCity College of Science and Commerce Test No:9 Subject: Computer Science Class: ICS 1 Year Student Name: - Roll NoMalik KashifNo ratings yet

- Legal and Ethical Issues in Computing Mid Exam SolutionDocument6 pagesLegal and Ethical Issues in Computing Mid Exam SolutionMalik KashifNo ratings yet

- Department of Computer Science, BZU, Multan: MCS (Evening) Semester - III Session 2019 - 2021Document2 pagesDepartment of Computer Science, BZU, Multan: MCS (Evening) Semester - III Session 2019 - 2021Malik KashifNo ratings yet

- MS4S10 Coursework 1 20202021Document9 pagesMS4S10 Coursework 1 20202021Malik KashifNo ratings yet

- Question No 01: (06) Marks: Institute of Southern Punjab MultanDocument1 pageQuestion No 01: (06) Marks: Institute of Southern Punjab MultanMalik KashifNo ratings yet

- Data Mining and Warehouse (B)Document2 pagesData Mining and Warehouse (B)Malik KashifNo ratings yet

- Department of Computer Science Online Mid Term ExaminationDocument3 pagesDepartment of Computer Science Online Mid Term ExaminationMalik KashifNo ratings yet

- Data Mining Paper SolutionDocument7 pagesData Mining Paper SolutionMalik KashifNo ratings yet

- Course Plan Natural Language ProcessingDocument5 pagesCourse Plan Natural Language ProcessingMalik KashifNo ratings yet

- Data Mining and Warehouse (A)Document2 pagesData Mining and Warehouse (A)Malik KashifNo ratings yet

- Course Plan Software EngineeringDocument6 pagesCourse Plan Software EngineeringMalik KashifNo ratings yet

- MCS (Weekend) Muhammad Kashif 3rd Data Mining and WarehousingDocument2 pagesMCS (Weekend) Muhammad Kashif 3rd Data Mining and WarehousingMalik KashifNo ratings yet

- Legal and Ethical IssuesDocument1 pageLegal and Ethical IssuesMalik KashifNo ratings yet

- Admire College of Science & Commerce Multan B.S - Semester Weekly Subject Plan Subject: Mid-TermsDocument2 pagesAdmire College of Science & Commerce Multan B.S - Semester Weekly Subject Plan Subject: Mid-TermsMalik KashifNo ratings yet

- Department of Computer Science & ITDocument1 pageDepartment of Computer Science & ITMalik KashifNo ratings yet

- Data Warehouse Course OutlineDocument8 pagesData Warehouse Course OutlineMalik KashifNo ratings yet

- Kindly Note: MS Office-365 Credentials & window/OS Activation Procedures Are Being Shared With YouDocument8 pagesKindly Note: MS Office-365 Credentials & window/OS Activation Procedures Are Being Shared With YouMalik KashifNo ratings yet

- Institute of Southern Punjab Multan: Department of Computer Science & ITDocument1 pageInstitute of Southern Punjab Multan: Department of Computer Science & ITMalik KashifNo ratings yet

- (D) Odd: ST STDocument2 pages(D) Odd: ST STMalik KashifNo ratings yet

- Challan Form 21 05 2014Document1 pageChallan Form 21 05 2014Malik KashifNo ratings yet

- Importance of An IdeologyDocument2 pagesImportance of An IdeologyMalik KashifNo ratings yet