Professional Documents

Culture Documents

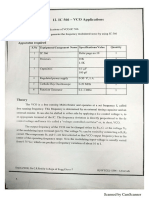

CamScanner 10-13-2020 13.52.57

CamScanner 10-13-2020 13.52.57

Uploaded by

pawan0 ratings0% found this document useful (0 votes)

10 views12 pagesCopyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

10 views12 pagesCamScanner 10-13-2020 13.52.57

CamScanner 10-13-2020 13.52.57

Uploaded by

pawanCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 12

(@) General Purpose Registers

£0386 architecture contains 8 general purpose register,

‘Each register i of 32-bit and can also be used either as 8-bitop

16-bit registers, Figure (1) shows the general purpose register

set of 80386.

3 Lots

ax] BAX

Bx | FBX.

x} Bex

px | EDX

st | §!

pr | £0!

ap | Er

sp_| esp

~ Figure (1): Goneral Purpose Registers

“Basically in 80386 processor a 32-bit

4 tefattaed’ ra 32-bit general purpose

4 ee ed as extended register and is denoted by @

ed Be eee eects 97 be rena

Cepesented by EAX, similarly EBX, BCXs

Fi eae eee AX dence he les

[bee EAX. Al and AL cach represent Bit

‘DX also have their 8-bit,

Scanned with CamScanner

architecture contains a 16-bit Instruction Pointer (IP) which can also be used as 32-bit instruction pointer (EIP).-

shows the format of IP and flag registers,

3 0

©

Flags _|EFLAGS

4 Figure (3): instruction Pointer and Flog Register

{80386 architecture contains a 32-bit flag register. The lower 15 bits i.c., D, - D,, are same as 80286 flag register and also

gforn same operation. The bit ‘D,” is always set at ‘I’ and the bits. D,, Dy D,, and D,, ~ D,, are reserved for future use, In this

‘only two bits are new when compared them with 80286. They are VM{at D,,) and RF (at D, ,) flags. Figure (4) shows

register of 80386.

Dy

DyDiy Dy Dy Dy Dy DD Dy Dy Dy Dy DD, Dy Dy D; Di, Dy

tort

v el,

Mie{-|t eleleleirle F

z

2

|] =

Fras shinee

Resume Flag = of _

Nested Task hag

a

F

Reserved

x] _]x sleletelelel

Wo privilege Level

r Over Flow

Direction Flag

Interrupt Enable

Trap Flag

Sign Flag

Zero Flag

*~ indicates that biti reserved for future we

ioe Fgura (Flog Register of 80306

de (VIM) Flag: When 80386 operates in protected mode then only itis possible to set the VM flag, if VM is set

86 enters virtual 8086 mode within the protected mode. In this mode, an exception 13 i Benerated

instruction, Task switch operations and IRET instruction are used to sct VM flag, 4

‘Scanned with CamScanner

od 9-bit attributes as shown in figure (5).

i a Descriptor registers (loaded automatically)

=

Other segment

13 0 Physical Address Segment Limit Attributes from descriptor

Selector |CS-| base Z

' Selector | SS — ae

Selector DS “=

Selector | ES - =| aps

Selector | FS— =| =e

Selector_| GS — =

Figure (5: 80386 Sogment and the Corresponding Descriptor Ro,

(9) Control Registers

£90386 architecture contains four 32-bit control registers ue. CR,, CR,, CR, and CR, The control registers CR,, CR, and

“GR, are used to keep the global machine status independent of exceuted task. However, the register CR, is reserved for future use,

| These registers can be accessed by the load and store instructions

(vl) System Address Registers and System Segment Registers

'80386 processor has four descriptor tables, They are,

(@) Global Descriptor Table (GDT)

(b) _Inmerrupt Descriptor Table (IDT)

(© Local Descriptor Table (LOT)

(4) Task State Segment (TSS) Descriptor

address registers and system

or] and IDTR [Interrupt Descriptor

ister] and TR [Task Register)

Issistes. Figure (6) shows the sets

¥ fun

of debug and test

ie, DI

ses DR, op Ue four eines

Figure (6): Debug and Test Registers

Scanned with CamScanner

scuss the paging mechanism of 80386 in detail.

| Processor: Paging is a memory management technique that is employed in virtual memory multi

the physical memory is divided into fixed size pages that contains portions of program and data,

‘ofthis technique is the reduction in memory requirement of the task, because it is not necessary that

‘code be in the physical memory but only few pages are to be available in the physical memory, thus

ble memory to the other tasks.

paging in 80386 is accomplished by a paging unit present in it, It derives the physical address of a page from the

sar address in two levels.

The paging unit defines three components for every task

Page directory

2. Page tables

3. Page itself

address of the page segment is store in a register called page descriptor base register.

tory has a maximum size of 4 kbytes and the size of each directory entry four bytes, hence a total of 1024 eatries

the directory. Figure (1) shows a directory entry, the upper 10 bits give the index address that points to a page table

nae ° |p [ale °

aN ledalal Hal» eccnjoe

Scanned with CamScanner

ove two entries ae same; ‘ od, coo Ft

te err can be used in adess anltion oF 9 p= 1incanbe

se et eet te ening of HEF : 7

vr pty smal emilee wri perso be PBN oe

Bee scsi inrenironrn

“under the 4 level protection ‘model as shown below. o

Read/Write

Read/Write

Read/Write _

Read only

__Read- Write =

‘Table: Four Lavol Protection Mode

Figure 3) illasrates the block diagram of «paging unit in 0386 processor.

User

31 2 2 o

Tear Pinson [re | omer

Address

io

Fr °

1 ¢ pt

ce Page able

eR,

cr,

Scanned with CamScanner

c MICROPROCESSORS AND MICROCONTROLLERS [JNTU-KAKINADAI

536 the basic operation of DAC chip with 6051,

a inerfocing of DACO8OS with 8051 is as shown in figure below,

pate wv omy

Ole

FE \-tw iv

caw

-itv

Figure: DACOSDS Interfaced ta 8051

The port P| of 8051 is interfaced with the digital inputs of DAC. The output of the DAC is current which is converted

‘so ollage using an op-amp. This analog output current depends on /,, flowing through V.,¢ and status of DO - D7 bits.

Hence, the current voltage is obtained as,

Tne + BE +S BERRA BBS Beg Dele

Scanned with CamScanner

UNIT-5 (Intel 8051 Microcontroller)

Teil) Name of the instruction: JBC 8-bit address

‘Operation: When the fourth bit of SCON is set to

1 and carry is reset i¢,, C= 0 then program jumps

to specified 8-bit address.

(vill) Name of the instruction: DINZ, Rn 8-bit address

Operation: The program jumps to the specified

8-bit address repeatedly while decrementing the

contents of register Rn tll it reaches 0.

Name of the instruction: DINZ direct 8-bit

address.

(x)

Operation: The program jumps to the specified

Sbit address repeatedly while decrementing the

direct byte until it reaches zero.

Q36. Briefly explain about addressing modes of

8051.

(or)

Discuss the types of addressing modes with

suitable example in 8051.

Ans: pert, (0)

Addressing Modes of 8051: There are various ways of

specifying the operands these are called addressing modes

There are five addressing modes in 8051, which are described

below.

1. Immediate Addressing Mode: In this mode, the source

operand is a constant ie, the operand is given in the

instruction itself. This addressing mode ean be used

to load information into any of the registers including

DPR register,

Opeode } (laa

Example

© MOY Bali sota ‘Load data into B

i) MOV DPTR,#OABCD H ;DPTR=0ABCDH

Example

() ADD ALR, :ContentSoFR ang

(i) MOV R,DPL ;Content ORL anee

Direct Addressing Mode: All 128 byte op "

RAM and the SFRS may be addressed it |

the single byte address assigned to each Ba: %

‘and each special function register, In this Ho

mode, the data is in RAM Memory locatig,

rdres is known and this address is given aa

«

the instruction.

RAM

Address

Example

1, MOV R, 40H

Loading data in address 40 H to R,

2. MOV OASH, 77H

Loading data in 77 H to AB H address...

Register Indirect Addressing Mode: In register indigg

addressing mode, a register is used to hold the adeno

‘an operand located in RAM. In other words, a regis

used as pointer to the data. The registers R, and Ro)

are used whereas R.-R, cannot be used,

Opeode | i

Register R, oF R, in current bank

Example

(9 MOV, @R, ;Moves contents of aes in, 9A

Gi) MOV @R,,B :Moves data in B to addressinR,

Indexed Addressing: It is used in accessing i

lements of look-up table entries located in the prop

ROM space of the 8051,

Scanned with CamScanner

Go. Boia abou Ee Se eee ney,

mm sre 16FH77 PIC microcontroller supports «total of 14 interpt auces. The following ars the types of ikerrops

cise?

paternal

pORTB change interrupt

F Fumer 0 overfiow interrupt and

peripheral antermupts.

se peripheral nterupts are corresponding othe following,

J iterupt RBOANT

parallel slave port

USART

Timer! and Timer2 overflows

AD converter

«Synchronous serial port

ccp!, CCP2, ‘SSP bus collision and

4 EEPROM write operation interrupt,

tntecrupt Coatrot Register (INTCON)

The INTCON register of 16F877 is shown in figure.

Figure: 16F877 INTCON Register

The fags in INTCON register are explained as follows,

- GIE —> Global interrupt enable bit

If, GIE=1, = Enable all

=0= Disable all

2 PEIE— Peripheral interrupt enable bit :

IfPEIE = 1, = Enable oll unmaskable peripheral interrupts

/ = 0, = Disable all the peripheral interrupts

‘TOIE —+ Timer0 - Overflow interrupt enable bit ‘ 2

‘If TOIF = 1 = Enable

70s Disable

Scanned with CamScanner

OIF —> Timer overflow interrupt lag

ICTOIF = 1 => TMRO register overflow

=0= No overflow of TMRO register

2. INTE» RBOANT external interrupt flag

ICINTR = 1 = Occurance of external interrupt

= 0 = Nocextemal interrupt

8 _RBIF -» RB port change interrupt flag bit

IF RBIF = 1 => Atleast one of RB7 to RBS lines changed their state

= = No change in state

Along with INTCON register, 16F877 also supports different types of peripheral interrupts and are)

|. PIE register

2 PIED register

3. PIRY register, and

4. PIR2 register

Here, both PIE and PIE2 have individual interrupt enable bits, but PIRI and PIR2 have individual in

1. PIEL Register

Here,

PSIE = Parallel slave port read/write interrupt enable bit

ADIE = Analog to digital converter interrupt enable bit ~

RCIE => USART receive interrupt enable bit am

‘TXIE => USART transmit interrupt enable bit

SSPIE => ‘Synchronous serial Port interrupt enable bit

CcPuE= ccPl Intra enable bit

‘Scanned with CamScanner

sewn NVUESSURS AND MICROCONTROLLERS

Bit 6 5 % gy \ °

[re [oor [eo [a [se [or |

Heres ,

spiF = Parallel slave port read/write interrupt flag

_apiF = Analog to digital converter interrupt lag

acIF = USART receive interrupt flag

[yxIP—> USART transmit interrupt flag

ssPIF = Synchronous serial port interrupt flag

cru => CCPI interrupt fag

‘TMR2IF = Timer 2 to PR2 mateh interrupt flag

‘TMRIIF = Timer! overflow interrupt flag,

4 PIR2 Register

Bits 7. 6 5 4 3 2 1 o

ee

Here, -

‘The bits 1, 2, 5, 6.and 7 are made ‘0’, i.c., cleared so, called unimplemented bits.

EEIF => EEPROM write operation interrupt flag

[BCLIF = Bus collision interrupt flag,

‘CCP2IF > CCP? interrupt flag.

Scanned with CamScanner

MICROPROCESSORS AND MICROCONTROLLERS

ot Tithe features ‘of PIC microcontroliers. ,

y Model Papers. G7ie)

o pes erie Conta (PIC) sa embeded ontle ha eng othe fully of mitosis designed

oship cal

sore!

the vai

yc microcontrollers are RISC computers and employ Harvard Architecture for their memory organization, The systems

ules separate memories ic, data memory of B-bits and program memory ranging from 12 wo 16-bits,

rpeinstracton st oF PIC involves only 35 instructions of 4-bits each, with execution ime of shout 0.2 ys (for maximum

0 ee fate) These instrctons are highly orthogonal Le, they are non-overlapping or mutually independent.

rhe machine cycle of PIC microcontrollers employ 4-clock pulses. °

features of PIC microcontrollers are,

Any operation in PIC controller is accomplished using any of the available register and addressing modes. This is dve to

| 0c simitar format ofall the instructions handled by PIC.

PIC microcontrollers also provide functions such as,

(a) Analog-to-digital conversion

() Builtin power-on-reset

(c) Built-in brown-out-reset (ie., PIC automatically resets whenever the supply voltage falls below 4'V),

PIC supports « fully static design. The oscillator frequency of PIC in any of the desired frequency range can vary from

‘minimum to maximum and can also be stopped and restored back at any time, The components used for estimating the

caillator frequency of PIC are low-cost RC circuit or Quartz crystal or ceramic resonator. It can also be a selectable

EPROM.

(vil) Italso provides # power saving mode called ‘SLEEP’, In this mode, the clock is freezed by restoring all its data in the

processor memory. The controller remains in the SLEEP mode until the next RESET of PIC.

(vii) The microcontroller supports a watch Dog Timer (WDT) along with on-chip RC oscillator which prevents the

from “endless loop hanging condition”.

(@) The PIC microcontrollers such as 16C6X and 16C7X require an operating voltage of about 30 to 60 V with

‘consumption of power.

fPIC supports a maximum of 12 independent interrupt sources.

(1) The program memory of PIC controllers range fom 1024 « 14 words to 8192 x 14 words.

Scanned with CamScanner

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5807)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (346)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Electronic Res Ervation Slip IRCT C E-T Icketing Service (Agent)Document3 pagesElectronic Res Ervation Slip IRCT C E-T Icketing Service (Agent)pawanNo ratings yet

- (13-11-20) 15 Days Attn 2 3 4 AB-1 Attn Online 2020-21Document16 pages(13-11-20) 15 Days Attn 2 3 4 AB-1 Attn Online 2020-21pawanNo ratings yet

- Subject Name & Code: DSP (R1632044) Date of Exam: 17-10-20: Write Ur Options in Below TableDocument2 pagesSubject Name & Code: DSP (R1632044) Date of Exam: 17-10-20: Write Ur Options in Below TablepawanNo ratings yet

- 60 Objective Type Questions On Vlsi DesignDocument12 pages60 Objective Type Questions On Vlsi Designpawan0% (1)

- Lica 7Document2 pagesLica 7pawanNo ratings yet

- Lica 11Document3 pagesLica 11pawanNo ratings yet

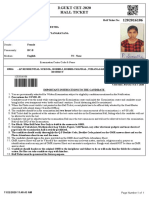

- Hall Ticket: RGUKT CET-2020Document1 pageHall Ticket: RGUKT CET-2020pawanNo ratings yet

- 108 EMPLOYEE DE-WPS OfficeDocument6 pages108 EMPLOYEE DE-WPS OfficepawanNo ratings yet

- Microwave Engineering: III B. Tech II Semester Regular Examinations, April/May-2019Document6 pagesMicrowave Engineering: III B. Tech II Semester Regular Examinations, April/May-2019pawanNo ratings yet

- Vlsi Design: III B. Tech II Semester Regular Examinations, April/May - 2019Document4 pagesVlsi Design: III B. Tech II Semester Regular Examinations, April/May - 2019pawan100% (1)