Professional Documents

Culture Documents

Sda2121 2X

Uploaded by

Ati0 ratings0% found this document useful (0 votes)

18 views16 pagesSda2121-2x

Original Title

SDA2121-2X

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentSda2121-2x

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

18 views16 pagesSda2121 2X

Uploaded by

AtiSda2121-2x

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 16

SIEMENS

PLL with I2C Bus for SDA 2121-2

AM/FM Receivers

Preliminary Data Mos Ic

Features

@ High input sensitivity (650 mVims on FM and 30 mVmson AM)

@ High input frequencies (150 MHz on FM and 25 MHz on AM)

Extremely fast phase detector with very short anti-backlash pulses

°C bus

@ Large divider rations: — 16 Bit N divider

— 16 Bit R divider

— Divider factor without vacancy OSC IN 2.65535

AMIN 2-65535

FMIN /2 2-65535

© Adjustable raster width (<1 kHz for AM, < 12.5 kHz for FM)*

© Two-pin oscillator provides connection of a piezoelectric crystal for reference frequen-

cy generation

Switchable phase detector polarity

© Switchable phase detector current

© One phase detector output each for FM and AM with the corresponding analog phase

detector outputs

© Open drain switching outputs for 10 V

Type Ordering Code Package

SDA 2121-2 Q67100-H5025 P-DIP-20

‘SDARI21eX [Qerio0-H026 20

Raster width = Input frequency / divider factor

[On FMIN input frequency / 2 is to be used due to the prescaler)

74 01.90

vv chips. He sure to visit ChipDocs web sit for nore information

SDA 2121-2

The SDA 2121-2 is an integrated circuit in CMOS technology which has been especially

designed for application in radio equipment.

The SDA 2121-2 is a complex PLL component in CMOS technology for processor

controlled frequency synthesis.

Function and dividing ratios are selected via an I2C bus interface (licensed by Philips) at

pins SCL, SDA and AO. The chip address is set via address input AO. Thus it is possible to

address two components via the 12C bus. The reference frequency can be applied at input

OSC IN or it can be generated internally by a piezoelectric crystal. Its maximum value is

15 MHz, The VCO frequency is applied at input FM or AM respectively. Its maximum val-

ue is 150 MHz at the FM input and 25 MHz at the AM input. The FM input signal is divided

by two by an asynchronous prescaler.

Outputs PDFM and PDAM supply the phase detector signal with especially short anti-

backlash pulses to neutralize even the smallest phase deviations. Polarity and current of

the PD outputs can be switched. The component also has corresponding analog phase

detector outputs and lock-detect output (LD).

Additional outputs are the open-drain switching outputs (SA 1, 2, 3, AM/FM) with a di-

electric strength of 10 V and a port output (PRT).

Pin Configuration

(top view)

P-DIP-20 P-DSO-20

not

osca

osc I

Lo

POAMA

POAM

POFM

POFMA

AMT

Gnoz

seu

SDA

Ao

PRT

sat

saz

SA3

AMEN

PAL

vente

‘Siemens Aktiengeselischaft 75

vv chips. He sure to visit ChipDocs web sit for nore information

vv chips.

SDA 2121-2

Pin Definitions and Functions

Pin No. ‘Symbol Function

4 Voo Supply voltage

2 SCL °C bus clock

3 [SDA °C bus data input and acknowledge output

4 AO ‘Address input

5 PRT Port output

6 SA1 ‘Switch output (open drain output for 10 V)

7 SA2 ‘Switch output (open drain output for 10 V)

8 ‘SA ‘Switch output (open drain output for 10 V)

9 AM/FM ' Switch output (open drain output, 10 V) switching AM/

FM operation

10 FMI FM FM input

4 GND2_ | Ground connection for AM and FM input amplifier

12 “/ AMI ‘AM input

13 PDFMA ‘Analog output corresponding to the phase detector out-

put, in test operation open drain output of FRN and FVN

| signal _

14 PDFM Phase detector output for AM or FM active or tristate de-

pending on operating mode

16 PDAM Phase detector output for AM or FM active or tristate de-

pending on operating mode

16 PDAMA Analog output corresponding to the phase detector out-

put, in test operation open drain output of FRN and FVN

signal

17 wo Lock-detect output -

18 oscil Connection for reference oscillator input and output

19 osca Conneetion for reference oscillator input and output

20 GND1 Ground

Siemens Aktiengesellschaft

76

He sure to visit ChipDocs web sit for nore information

SDA 2121-2

Block Diagram

SA

A

Lt

GNO 2

i i

‘Siemens Aktiengeselischaft 77

vv chips. He sure to visit ChipDocs web sit for nore information

SDA 2121-2

Absolute Maximum Ratings

Parameter ‘Symbol | Limit Values Unit

imin. | typ. | max.

Supply voltage | Voo l-03 6 \Vv

Input voltage vi -03 | Vo+03 |V

Power dissipation per output. |Po M0 mw

Total power dissipation Pex 1300 mw

Storage temperature Tw ([-40 125 °C.

Output voltage ~

switch outputs Vou | 10.5 v

Operating Range

Supply voltage Voo 45/5 55 Vv

Supply current loo 6 10 mA

‘Ambient temperature Ta -2 | 85 °C

Output voltage Vou 10 Vv ”

switch outputs |

Test conditions for supply voltage

= Von =5.5V

-T 25°C outputs not connected

~ No test operation

— Max. permissible operating frequency on AM, FM, OSC IN = 15 MHz

— View, View, Viosom = 100 mVerns

— Minimal divider ratios

= PLLin in-lock condition

Siemens Aktiengesellschaft 78

vv chips. He sure to visit ChipDocs web sit for nore information

SDA 2121-2

Characteristics

Ta= 26 °C; all voltages referenced to GND

Parameter Symbol Limit Values Unit | Test Condition

min. [typ. | max. i

Input Signals SCL, SDA, AO

H-input voltage Vin 10.70 Voo | V

Linput voltage ve fo 15) |v

Input capacitance | Ci | 10 | pF

Input current in }10 [eA | i Vo0

Input Signal OSC IN

Input frequency

if 15 [MHz ]Vco=4.5V

Input voltage lv 400 | mVrms | (sine wave)

Input capacitance a 10 pF

input current h 30 WAV

Input Signal AM

Input frequency f 05 25 |MHz | Voo =4.5V

Input voltage vi 30 mVrms | (sine wave)

Input capacitance | 10 pF

Input current io 30 nA Vie Voo

Input Signal FM

Input frequency f 10 150 |MHz Voo=4.5V

Input voltage ive |50 mVrms | (sine wave)

Input capacitance | C 10 | pF

Input current h 30 vA Vix Voo

Siemens Aktiengeselischaft 79

vv chips. He sure to visit ChipDocs web sit for nore information

SDA 2121-2

Characteristics (cont'd)

Ta=25 C; all voltages referenced to GND

Parameter Symbol] ___Limit Values Unit | Test Condition

min. | typ. | max.

Output signal PDFM (tristate output)

PD current valueA | fa 340 [2570

PD current valueB | Ja a | 145

PD leakage current | Jo + 50

Output Signal PDAM (tristate output)

PDcurrentvalueA | Ja 70. [2115 [160 [uA

PD current valueB | Jo 15 +3045 [yA

PD leakage current | fa + 50 |500 {nA

Output Signal PDAMA, PDFMA (analog output)

H-output current To 1 25 [ma

Loutput current Jaw o1 | 05 mA

om

+ pout, area

nia

‘Siemens Aktiengeselischatt 80

vv chips. He sure to visit ChipDocs web sit for nore information

SDA 2121-2

Characteristics (cont'd)

Ta = 25°C; all voltages referenced to GND

Parameter "| Symbot | Limit Values Unit | Test Condition

min.

Output Signal LD (open drain output)

L-output signal [Va 0.4 v

I

I

}

L-output pulse width | rom 30 ns

Output Signal PRT

H-output voltage Vou |Voo— o.] v

L-output voltage Vor } |o4 v

Vou } ot |v

OutputSsignal SA 1, 2, 3 and FM (open drain switching outputs)

L-output voltage Vou o4 |v Tos mA

Voo=5V

vo o1 |v Fo = 0.1 MA

Output Signal SDA

L-output voltage Vor 04 |v Jou =3mA

Voo=5V

Ci = 400 pF

‘Siemens Aktiengeselischatt 81

vv chips. He sure to visit ChipDocs web sit for nore information

SDA 2121-2

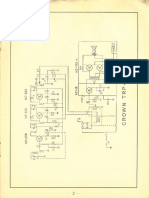

Test Circuit

Von UH-Bulfer

a7Ko

509

vw Tho no ape 1

Yonr == wre xP

[ wwonF

xP Asc. osc of % ote T 1

+ Von

PC Bus ska

SOA osc 1} 18

XP OJ ao to f

xP oO Stop poamal'S—4—o-%y—_ LH Buffer} _e 12

(FRND

o~e —__—o VI

E 1a

xp 9 —___4jsa1 poanp'S 4 __fB,__a xp

~~ ot

2 % poh

xP. saz porn}! 4 xP

oe 0 xe

xP S\saz_— porta f 4omBy__ EH Butter |_oyra

(FvN)

9 2

xP a ne

xP O— — + FMT GND 2] i = aL

1000F T

Sox. 1o0nF

20007 @—-{saB

56130 00aF

son vee

XP= Matrix Pin

Siemens Aktiengeselischatt 82

vv chips. He sure to visit ChipDocs web sit for nore information

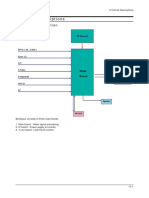

Application Circuit

we

I

2)

Ht ess

oat

SDA 2121-2

wal

sy

SL AD SOR LD Yaa

POAM

lr |} AM Tune]

POAMA veo

osca

TSO

SDA 2121-2 [

POFME—ay FM Toner

veo

POFMA

GNO1 SA AM FM GNDZ u

¥

‘5

Et

Siemens Aktiengesellschaft

vv chips.

83

He sure to visit ChipDocs web sit for nore information

wenn

SDA 2121-2

Diagram

Status Programming Table

Status Bit

Bit 0 1

1 PRT L H

2 SA1 L H

3 SA2 L H

4 SA3 L H

5 AM/FM L (FM operation) H (AM operation)*

6 PD analogitest PD analog test*

7 PO polarity neg. pos.

8 PD current value B value A (AM or FM

operation)

“When the switch output FM is switched from "H" to “!

switched from AM to FM

PDAM is in tristate and vice versa

ia bit 5 (FM), operation is

“In test operation PDFMA and PDAMA outputs are switched as FVN and FRN outputs re-

spectively

‘Siemens Aktiengeselischatt 84

vv chips. He sure to visit ChipDocs web sit for nore information

I°C Bus Transfer Protocol

wamnoo>d

sUB-

womn00>

SDA

oaomnoord

e8cscoss

5

vomnoore

PRT

SAt

SAQ 1

SA3

AMM

TesuPD analog

PO polarity

PD current

(> Status

|

> R divider

isB

tical, the respective chip is selected.

Siemens Aktiengesellschatt 85

vv chips.

He sure to visit ChipDocs web sit for nore information

SDA 2121-2

SDA

> N divider

“Chip select is achieved via bit 7 of the IC address. The contents

are compared with the value set on pin AO. If the values are iden-

SDA 2121-2

Programming Example

soa

ic

‘A

D

D

A

t

8 our

‘SUB- x

uF i

D |

2 ‘i

a

E

$

8

pat

Sai

Sa?

SA8 > Status

ante

‘estPD analog

Po polarity

Po curen

se

10

io

a

GK 1> R divider

v1

cdl

90

ao |

0/0

oo” us6 Inout equency

ACK int]

Stos FMIN 100

] AMIN 1

awsoooe — L— teorm OScIN 4

‘Siemens Aktiengesellschaft 86

vv chips.

He sure to visit ChipDocs web sit for nore information

SDA

Ic

A

o

D

R <

E

s

s

SUB-

A

o

p<

ra |

E

s

s

MsB ~

|

> N divider

oo | isa —

ACK

Stop |

‘AM,10002 —! — .2000,FM

Raster width Divider ratio

[kHz]

25 2000 N divider

1 4000 N divider

251 60/4000 R divider

SDA 2121-2

Transfer Protocol for I?C Bus

GLX + ON 2S y

aqosip 51414! 4ndu yas aut a1g0u3

©) NO s9nod Jayjo ayuantas asing

(wonsade 305 | gous

LUIS | gpoas'sng ),1-19598)

“yy i it mu as

Se a

ssaupnay

anors wos} ine 10} ydu0sd)| | vorpowsjuny pvayhiaysoy wos, 4nejn9=)

abpaynounry| abpaimouy2y| | 24015 wou abpajrouyry| ays /pO9y-4>2I95

——

a _

Hes waun vas anos wou He1Ds weURe. vas|

NOILIGNOS aous| abparnoury| Notuiawo) iavis|

Ps0M 2409

iow o100 «san yndino | |asayanding

[*

— 2100

2s0Y 31)

7 SSBUPY UNO

«S50 ans

87

Siemens Aktiengesellschatt

Inforaion.

He sure to visit ChipDocs web site f

vv chips.

SDA 2121-2

1°C Bus Timing, PRT, SA, AM/FM

Parameter ‘Symbol Limit Values Unit

| min. | max.

Clock frequency - - foc. - 0 | 100 kHz

Hold time data to SCLiow | rmoaar o ss

Inactive time prior tonext transfer | rur «4.7 | us

Hold time during start condition! most 4.0 Hs

(first CLOCK pulse is generated

after this time period)

LOW clock phase how 47 us

HIGH clock phase ton | 40

Set-up time for DATA tsuoar 250 ! ns

Rise time for SDA and SCL signal | in [ 1 us

Fall time for SDA and SCL signal _| i= | 300 [ns

Set-up time for SCL clock during] rsusro 47 | lus

STOP condition _

PRT delay time relative to STOP) 10 500 us

condition |

All values are referenced to specified input levels Vm and Vu.

Siemens Aktiengesellschatt 88

vv chips. He sure to visit ChipDocs web sit for nore information

SDA 2121-2

Pulse Diagram

Phase Detector/Lock Detector

ost f

teem _SL_FL_SL_JIL__

(OSC TR

FM, AM Ar

fy | | |

(FM/AM N),

P-Channe! YN |

Tristate Potorty pos.)

| Status

N-Channel U arr

Po

P-Channel |

Tristate + (Polarity neg.)

| Status

N-Channel Bret

to

=~ ro T=

LJ ven

‘Siemens Aktiengeselischatt 89

vv chips. He sure to visit ChipDocs web sit for nore information

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Dutra D4K Final Part ListDocument12 pagesDutra D4K Final Part ListAtiNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Romet Kadet Hasznalati UtasitasDocument25 pagesRomet Kadet Hasznalati UtasitasAtiNo ratings yet

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Crown+Radio+TRP 6RDocument1 pageCrown+Radio+TRP 6RAtiNo ratings yet

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Philips Radio 1650 SMDocument5 pagesPhilips Radio 1650 SMAtiNo ratings yet

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Philips Radio-Recorder 22ar060 SMDocument7 pagesPhilips Radio-Recorder 22ar060 SMAtiNo ratings yet

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- FM/AM/SW1/SW2 PLL Synthesized Receiver: Owner'S ManualDocument12 pagesFM/AM/SW1/SW2 PLL Synthesized Receiver: Owner'S ManualAtiNo ratings yet

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- RadioShack PRO-2044 UserDocument30 pagesRadioShack PRO-2044 UserAtiNo ratings yet

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Blaupunkt Stockholm RCR 42Document2 pagesBlaupunkt Stockholm RCR 42c_simosNo ratings yet

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Reversible Motor Driver: BA6219B/6219BFP-YDocument8 pagesReversible Motor Driver: BA6219B/6219BFP-YAtiNo ratings yet

- Circuit DescriptionDocument7 pagesCircuit DescriptionAtiNo ratings yet

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- John QDocument1 pageJohn QAtiNo ratings yet

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Circuit DescriptionDocument8 pagesCircuit DescriptionAtiNo ratings yet

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Blaupunkt BCA 46 Operating ManualDocument6 pagesBlaupunkt BCA 46 Operating ManualAtiNo ratings yet

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- M66006P/FPDocument5 pagesM66006P/FPAtiNo ratings yet

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Tgs TGX GBDocument191 pagesTgs TGX GBPaul Marshall100% (14)

- Tgs TGX GBDocument191 pagesTgs TGX GBPaul Marshall100% (14)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)