Professional Documents

Culture Documents

General Description: 3A 27V Synchronous Buck Converter

Uploaded by

Dario David DimaroOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

General Description: 3A 27V Synchronous Buck Converter

Uploaded by

Dario David DimaroCopyright:

Available Formats

LSP5523

3A 27V Synchronous Buck Converter

General Description

The LSP5523 is a monolithic synchronous buck regulator. The device integrates 90 mΩ MOSFETS that

provide 3A continuous load current over a wide operating input voltage of 4.5V to 27V. Current mode control

provides fast transient response and cycle-by-cycle current limit. An adjustable soft-start prevents inrush

current at turn on.

Features

3A Output Current

Wide 4.5V to 27V Operating Input Range

Fixed 340KHZ Frequency

Integrated Power MOSFET Switches

Output Adjustable from 0.925V to 0.8Vin

Up to 93% Efficiency

Programmable Soft-Start

Stable with Low ESR Ceramic Output Capacitors

Cycle by Cycle Over Current Protection

Short Circuit Protection

Input Under Voltage Lockout

Package: ESOP-8L

Applications

Distributed Power Systems

Networking Systems

FPGA, DSP, ASIC Power Supplies

Green Electronics/ Appliances

Notebook Computers

Please be aware that an Important Notice concerning availability, disclaimers, and use in critical

applications of LSC products is at the end of this document.

LSP5523 Rev. 1.1 2014/8/27

1 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

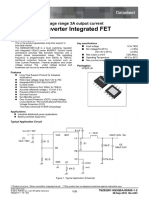

Block Diagram

CURRENT

OVP SENSE 2 VIN

1.1V RAMP AMPLIFIER

5V

OSCILLATOR

FB 5

340/120KHz CLK

1 BS

0.3V

S Q

R Q 3 SW

SS 8 CURRENT

ERROR

0.925V AMPLIFIER COMPARATOR

6uA

COMP 6

4 GND

EN 7 EN OK

1.2V OVP

IN<4.10V

LOCKOUT

2.5V

COMPARATOR

IN

INTERNAL

REGULATORS

1.5V SHUTDOWN

COMPARATOR

Ordering Information

LSP 5523 - XX X X

Packing

Output Voltage

Package

Package Output Voltage Packing

R8 : ESOP-8L Blank : ADJ A : Tape & Reel

LSP5523 Rev. 1.1 2014/8/27

2 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

Pin Assignment

ESOP-8L

(TOP View)

BS 1 8 SS

VIN 2 Exposed 7 EN

Pad on

SW 3 Backside 6 COMP

GND 4 5 FB

Pin Descriptions

Pin Name Name Pin Description

Bootstrap. This pin acts as the positive rail for the high-side switch’s gate driver.

1 BS

Connect a 0.01uF capacitor between BS and SW.

Input Supply. Bypass this pin to GND with a low ESR capacitor. See Input Capacitor

2 VIN

in the Application Information section.

3 SW Switch Output. Connect this pin to the switching end of the inductor.

4 GND Ground.

Feedback Input. The voltage at this pin is regulated to 0.925V. Connect to the

5 FB

resistor divider between output and ground to set output voltage.

Compensation Pin. See Stability Compensation in the Application Information

6 COMP

section.

Enable Input. When higher than 2.7V, this pin turns the IC on. When lower than

1.1V, this pin turns the IC off. Output voltage is discharged when the IC is off. This

7 EN

pin should not be left open. Recommend to put a 150K pull-up resistor to Vin for

startup.

Soft-Start Control Input. SS controls the soft-start period. Connect a capacitor from

8 SS SS to GND to set the soft-start period. A 0.1uF capacitor sets the soft-start period to

13ms. To disable the soft-start feature, leave SS unconnected.

Exposed Pad Exposed Pad. Need to connect to GND pin.

LSP5523 Rev. 1.1 2014/8/27

3 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

Absolute Maximum Ratings(at TA=25°C)

Note: Operate over the “Absolute Maximum Ratings” may cause permanent damage to the device.

Exposure to such conditions for extended time may still affect the reliability of the device.

Characteristics Value Unit

Input Supply Voltage -0.3 to 30 V

SW Voltage -0.3 to VIN + 0.3 V

BS Voltage VSW – 0.3 to VSW + 6 V

EN, FB, COMP Voltage -0.3 to 5 V

Continuous SW Current Internally limited A

Maximum Junction Temperature 150 °C

Storage Temperature Range -65 to 150 °C

ESOP-8L Thermal Resistance (Junction to Case) 19 °C/W

ESOP-8L Thermal Resistance (Junction to Ambient) 84 °C/W

ESOP-8L Power dissipation 1450 mW

Please refer the MSL label on the IC package

Moisture Sensitivity (MSL)

bag/carton for detail

Note1: Ratings apply to ambient temperature at 25°C

Recommended Operating Conditions

Characteristics Min Max Unit

(1)

Input Supply Voltage 4.5 27 V

(2)

Operating Junction Temperature -20 +125 °C

Note (1): Operating the IC over this voltage is very easy to cause over voltage condition to VIN pin, SW pin, BS pin & EN pin)

Note (2): If the IC experienced OTP, then the temperature may need to drop to <125 degree C to let the IC recover.)

LSP5523 Rev. 1.1 2014/8/27

4 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

Electrical Characteristics

(TA=25°C, unless otherwise specified)

Characteristics Symbol Conditions Min Typ Max Unit

Feedback Voltage VFB 4.5V ≤ VIN ≤ 27V 0.900 0.925 0.950 V

Feedback Overvoltage Threshold 1.1 V

High-Side Switch-On Resistance* 90 mΩ

Low-Side Switch-On Resistance* 70 mΩ

High-Side Switch Leakage VEN = 0V, VSW = 0V 0.1 10 uA

Upper Switch Current Limit Minimum Duty Cycle 3.8 4.5 A

Lower Switch Current Limit From Drain to Source 1.2 A

COMP to Current Sense Limit

GCS 5.2 A/V

Transconductance

Error Amplifier Transconductance GEA ΔICOMP = ±10uA 900 uA/V

Error Amplifier DC Gain* AVEA 400 V/V

Switching Frequency fSW 300 340 380 KHz

Short Circuit Switching Frequency VFB = 0 100 KHz

Minimum Duty Cycle* Dmin 7.5 %

Maximum Duty Cycle Dmax 92 %

EN Shutdown Threshold Voltage VEN Rising 1.1 1.4 2 V

EN Shutdown Threshold Voltage

180 mV

Hysteresis

EN Lockout Threshold Voltage 2.2 2.5 2.7 V

EN Lockout Hysteresis 150 mV

Supply Current in Shutdown VEN = 0 0.3 3.0 uA

IC Supply Current in Operation VEN = 3V, VFB = 1.0V 1.3 1.5 mA

Input UVLO Threshold Rising UVLO VEN Rising 3.80 4.0 4.40 V

Input UVLO Threshold Hysteresis 150 mV

Soft-start Current VSS = 0V 6 uA

Soft-start Period CSS = 0.1uF 13 mS

Thermal Shutdown Temperature* Hysteresis =25°C 155 °C

Note : * Guaranteed by design, not tested.

LSP5523 Rev. 1.1 2014/8/27

5 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

Application Circuit

LSP5523 application circuit, 3.3V/3A output.

LSP5523 application circuit, 3.3V/3A output with EN function

Note: C2 is required for separate EN signal.

LSP5523 Rev. 1.1 2014/8/27

6 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

Output Voltage Setting

VOUT

R1

FB

R2

Figure1. Output Voltage Setting

Figure 1 shows the connections for setting the output voltage. Select the proper ratio of the two feedback

resistors R1 and R2 based on the output voltage. Typically, use R2 ≈ 10KΩ and determine R1 from the

following equation:

VOUT R1 R2

1.0V 1.0 KΩ 12 KΩ

1.2V 3.0 KΩ 10 KΩ

1.8V 9.53 KΩ 10 KΩ

2.5V 16.9 KΩ 10 KΩ

3.3V 26.1 KΩ 10 KΩ

5V 44.2 KΩ 10 KΩ

12V 121 KΩ 10 KΩ

Table1- Recommended Resistance Values

(1)

Inductor Selection

The inductor maintains a continuous current to the output load. This inductor current has a ripple that is

dependent on the inductance value: higher inductance reduces the peak-to-peak ripple current. The trade off

for high inductance value is the increase in inductor core size and series resistance, and the reduction in

current handling capability. In general, select an inductance value L based on the ripple current requirement:

VOUT ( VIN VOUT )

L (2)

VIN f SW I OUTMAX K RIPPLE

where VIN is the input voltage, VOUT is the output voltage, fSW is the switching frequency, IOUTMAX is the

maximum output current, and KRIPPLE is the ripple factor. Typically, choose KRIPPLE = ~ 30% to correspond to

the peak-to-peak ripple current being ~30% of the maximum output current.

With this inductor value, the peak inductor current is IOUT • (1 + KRIPPLE / 2). Make sure that this peak inductor

current is less than the upper switch current limit. Finally, select the inductor core size so that it does not

saturate at the current limit. Typical inductor values for various output voltages are shown in Table 2.

VOUT 1.0V 1.2V 1.5V 1.8V 2.5V 3.3V 5V 9V

L 4.7uH 4.7uH 10uH 10uH 10uH 10uH 10uH 22uH

Table 2. Typical Inductor Values

LSP5523 Rev. 1.1 2014/8/27

7 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

Input Capacitor

The input capacitor needs to be carefully selected to maintain sufficiently low ripple at the supply input of the

converter. A low ESR Electrolytic (EC) capacitor is highly recommended. Since large current flows in and

out of this capacitor during switching, its ESR also affects efficiency.

When EC cap is used, the input capacitance needs to be equal to or higher than 100uF.The RMS ripple

current rating needs to be higher than 50% of the output current. The input capacitor should be placed close

to the VIN and GND pins of the IC, with the shortest traces possible. The input capacitor can be placed a

little bit away if a small parallel 0.1uF ceramic capacitor is placed right next to the IC.

When Vin is >15V, pure ceramic Cin (* no EC cap) is not recommended. This is because the ESR of a

ceramic cap is often too small, Pure ceramic Cin will work with the parasite inductance of the input trace and

forms a Vin resonant tank. When Vin is hot plug in/out, this resonant tank will boost the Vin spike to a very

high voltage and damage the IC.

Output Capacitor

The output capacitor also needs to have low ESR to keep low output voltage ripple. In the case of ceramic

output capacitors, RESR is very small and does not contribute to the ripple. Therefore, a lower capacitance

value can be used for ceramic capacitors. In the case of tantalum or electrolytic capacitors, the ripple is

dominated by RESR multiplied by the ripple current. In that case, the output capacitor is chosen to have

sufficiently low ESR.

For ceramic output capacitors, typically choose two capacitors of about 22uF. For tantalum or electrolytic

capacitors, choose a capacitor with less than 50mΩ ESR.

Optional Schottky Diode

During the transition between high-side switch and low-side switch, the body diode of the low side power

MOSFET conducts the inductor current. The forward voltage of this body diode is high. An optional Schottky

diode may be paralleled between the SW pin and GND pin to improve overall efficiency. Table 3 lists

example Schottky diodes and their Manufacturers.

Table 3-Diode Selection Guide

Voltage/Current

Vin max Part Number Vendor

Rating

<20V B130 30V, 1A Lite-on semiconductor corp.

<20V SK13 30V, 1A Lite-on semiconductor corp

>20V B140 40V,1A Lite-on semiconductor corp

>20V SK14 40V, 1A Lite-on semiconductor corp.

Stability Compensation

CCOMP2 is needed only for high ESR output capacitor

Figure 2. Stability Compensation

LSP5523 Rev. 1.1 2014/8/27

8 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

The feedback loop of the IC is stabilized by the components at the COMP pin, as shown in Figure 2. The DC

loop gain of the system is determined by the following equation:

0 . 925 V

AVDC AVEA G COMP (4)

I OUT

The dominant pole P1 is due to CCOMP1:

GEA

f P1 (5)

2AVEACCOMP1

The second pole P2 is the output pole:

I OUT

f P2 (6)

2VOUT COUT

The first zero Z1 is due to RCOMP and CCOMP1:

1

f Z1 (7)

2RCOMPCCOMP1

And finally, the third pole is due to RCOMP and CCOMP2 (if CCOMP2 is used):

1

fP 3 (8)

2πR COMP C COMP 2

The following steps should be used to compensate the IC:

STEP1. Set the crossover frequency at 1/10 of the switching frequency via RCOMP:

2VOUT C OUT f SW

RCOMP (9)

10G EA GCOMP 0.925V

But limit RCOMP to 10KΩ maximum. More than 10 KΩ is easy to cause overshoot at power on.

STEP2. Set the zero fZ1 at 1/4 of the crossover frequency. If RCOMP is less than 10KΩ, the equation for

CCOMP is:

0.637

CCOMP 1 (F ) (10)

RCOMP fc

STEP3. If the output capacitor’s ESR is high enough to cause a zero at lower than 4 times the crossover frequency, an

additional compensation capacitor CCOMP2 is required. The condition for using CCOMP2 is:

RESRCOUT

COUT RESR fs 1 (11)

And the proper value for CCOMP2 is:

LSP5523 Rev. 1.1 2014/8/27

9 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

C OUT R ESRCOUT

C COMP 2 (12)

R COMP

Though CCOMP2 is unnecessary when the output capacitor has sufficiently low ESR, a small value CCOMP2

such as 100pF may improve stability against PCB layout parasitic effects.

Table 4 Component Selection Guide for Stability Compensation

Vin Range Vout, Rcomp, Ccomp, Ccomp2, Inductor,

Cout

(V) (V) (kΩ) (nF) (pF) (uH)

5 – 12 1.0 2.4 6.8 none 4.7

5 – 15 1.2 3 6.2 none 4.7

5 – 15 1.8 22uF x2 6.2 3 none 10

5 – 15 2.5 Ceramic 8 2.2 none 10

5 – 15 3.3 10 2.2 none 10

7 – 15 5 10 2.2 none 10

5 – 12 1.0

5 – 15 1.2 470uF/

5 – 23 1.8 6.3V/

10 10 680 10

120mΩ

5 – 27 2.5

5 – 27 3.3

7 – 27 5

Figure 3. Load Transient Testing VS Compensation Value

LSP5523 Rev. 1.1 2014/8/27

10 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

Typical Characteristics

(Vin=12V, Io=0 mA, Temperature = 25 degree C, unless otherwise specified)

Light Load Operation (No load) Heavy Load Operation (3A Load)

Vin=12V, Iin=8.2 mA, Vout=3,3V Vin=12V, Vout=3,3V

Startup Vin=12V, Vout=3.3V, Iout=1A

through Vin. through Enable.

Short Circuit Protection Vin=12V

LSP5523 Rev. 1.1 2014/8/27

11 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

Typical Characteristics (Continued)

EFFICIENCY vs LOAD CURRENT (Vout=3.3V) OUTPUT VOLTAGE (3.3V) vs LOAD CURRENT

98.0 3.4

94.0 Vin=5

3.375 Vin=23 V

OUTPUT VOLTAGE, (V)

90.0

Vin=12V 3.35

EFFICIENCY (%)

86.0 Vin=12V

3.325

82.0 Vin=23 V

3.3

78.0 Vin=5

3.275

74.0

3.25

70.0

3.225

66.0

3.2

62.0

0 0.5 1 1.5 2 2.5 3 3.5 4

0 0.5 1 1.5 2 2.5 3 3.5

LOAD CURRENT (A) LOAD CURRENT, (A)

OUTPUT VOLTAGE vs SWITCHING FREQUENCY vs

AMBIENT TEMPERATURE AMBIENT TEMPERATURE

3.31 350

3.3075 345

OUTPUT VOLTAGE, (V)

SWITCHING FREQUENCY,

3.305

3.3025 340

3.3

3.2975 335

(kHz)

3.295 330

3.2925

3.29 325

3.2875

3.285 320

3.2825 315

3.28

3.2775 310

-50 -30 -10 10 30 50 70 90 110 130 150 -50 -30 -10 10 30 50 70 90 110 130 150

AMBIENT TEMPERATURE, (C)

AMBIENT TEMPERATURE, (C)

SWITCHES RdsON vs JUNCTION TEMPERATURE vs LOAD CURRENT (Ta=25C)

100

JUNCTION TEMPERATURE (Vin=12V)

0.13 90

JUNCTION TEMPERATURE, C

0.12 80 Vin=23V Vin=12V

SWITCHES RdsON

0.11 70

0.1 60 Vin=5V

0.09 50

0.08 40

0.07 30

0.06 20

10 30 50 70 90 110 130 150 170 0 0.5 1 1.5 2 2.5 3 3.5

JUNCTION TEMPERATURE (C) LOAD CURRENT, A

LSP5523 Rev. 1.1 2014/8/27

12 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

Marking Information

ESOP-8L

V YYWW UZ

Internal Code

Date code

YY:Year(09=2009,10=2010,11=2011,12=2012...)

WW:Week(01~53)

Output Voltage

Blank:ADJ

LSP5523 Rev. 1.1 2014/8/27

13 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

Mechanical Information

(1) Package type: ESOP-8L

Unit:mm

Symbol Min Max

A - 1.70

A1 - 0.15

A2 1.30 1.55

b 0.33 0.51

c 0.17 0.25

D 4.70 5.10

D1 3.10 REF

E 5.80 6.20

E1 3.70 4.10

E2 2.21 REF

e 1.27 BSC

L 0.40 1.27

L1 1.00 1.10

Gauge Plane 0.25 BSC

o

θ 0 8o

LSP5523 Rev. 1.1 2014/8/27

14 of 15

www.liteonsemi.com

LSP5523

3A 27V Synchronous Buck Converter

MSL (Moisture Sensitive Level) Information

IPC/JEDEC J-STD-020D.1 Moisture Sensitivity Levels Table

SOAK REQUIREMENTS

1

Accelerated Equivalent

FLOOR LIFE

Standard eV eV

LEVEL

0.40-0.48 0.30-0.39

CONDITION

TIME TIME TIME

TIME CONDITION CONDITION

(hours) (hours) (hours)

≤30 °C /85% 168 85 °C /85%

1 Unlimited NA NA NA

RH +5/-0 RH

≤30 °C /60% 168 85 °C /60%

2 1 year NA NA NA

RH +5/-0 RH

2

≤30 °C /60% 696 30 °C /60% 120 168

2a 4 weeks 60 °C/ 60% RH

RH +5/-0 RH -1/+0 -1/+0

2

≤30 °C /60% 192 30 °C /60% 40 52

3 168 hours 60 °C/ 60% RH

RH +5/-0 RH -1/+0 -1/+0

2

≤30 °C /60% 96 30 °C /60% 20 24

4 72 hours 60 °C/ 60% RH

RH +2/-0 RH +0.5/-0 +0.5/-0

2

≤30 °C /60% 72 30 °C /60% 15 20

5 48 hours 60 °C/ 60% RH

RH +2/-0 RH +0.5/-0 +0.5/-0

2

≤30 °C /60% 48 30 °C /60% 10 13

a 24 hours 60 °C/ 60% RH

RH +2/-0 RH +0.5/-0 +0.5/-0

Time on Label ≤30 °C /60% 30 °C /60%

6 TOL NA NA NA

(TOL) RH RH

Note 1: CAUTION - To use the ‘‘accelerated equivalent’’ soak conditions, correlation of damage response (including electrical, after

soak and reflow), should be established with the ‘‘standard’’ soak conditions. Alternatively, if the known activation energy for moisture

diffusion of the package materials is in the range of 0.40 - 0.48 eV or 0.30 - 0.39 eV, the ‘‘accelerated equivalent’’ may be used.

Accelerated soak times may vary due to material properties (e.g .mold compound, encapsulant, etc.). JEDEC document JESD22-

A120 provides a method for determining the diffusion coefficient.

Note 2: The standard soak time includes a default value of 24 hours for semiconductor manufacturer’s exposure time (MET) between

bake and bag and includes the maximum time allowed out of the bag at the distributor’s facility. If the actual MET is less than 24 hours

the soak time may be reduced. For soak conditions of 30 °C/60% RH, the soak time is reduced by 1 hour for each hour the MET is

less than 24 hours. For soak conditions of 60 °C/60% RH, the soak time is reduced by 1 hour for each 5 hours the MET is less than

24 hours. If the actual MET is greater than 24 hours the soak time must be increased. If soak conditions are 30 °C/60% RH, the soak

time is increased 1 hour for each hour that the actual MET exceeds 24 hours. If soak conditions are 60 °C/60% RH, the soak time is

increased 1 hour for each 5 hours that the actual MET exceeds 24 hours.

Important Notice and Disclaimer

LSC reserves the right to make changes to this document and its products and specifications at any

time without notice. Customers should obtain and confirm the latest product information and

specifications before final design, purchase or use.

LSC makes no warranty, representation or guarantee regarding the suitability of its products for any

particular purpose, nor does LSC assume any liability for application assistance or customer product

design. LSC does not warrant or accept any liability with products which are purchased or used for any

unintended or unauthorized application.

No license is granted by implication or otherwise under any intellectual property rights of LSC.

LSC products are not authorized for use as critical components in life support devices or systems

without express written approval of LSC.

LSP5523 Rev. 1.1 2014/8/27

15 of 15

www.liteonsemi.com

You might also like

- 2A 23V Synchronous Buck Converter: General DescriptionDocument15 pages2A 23V Synchronous Buck Converter: General DescriptionmoftahNo ratings yet

- LSP5526Document17 pagesLSP5526Hadi Habibi ShahandashtiNo ratings yet

- Bd9g341aefj LBDocument30 pagesBd9g341aefj LBFantazsta White Trash.No ratings yet

- Ame5269 AmeDocument18 pagesAme5269 AmeCharles PNo ratings yet

- AP3502Document11 pagesAP3502nassimNo ratings yet

- AX3161 AXEliteDocument12 pagesAX3161 AXEliteCristian CiocoiuNo ratings yet

- 3A Synchronous Step Down DC/DC Converter: General Description FeaturesDocument12 pages3A Synchronous Step Down DC/DC Converter: General Description FeaturesFélix NicolauNo ratings yet

- XL6003 enDocument10 pagesXL6003 enSelman ÇORANo ratings yet

- XL4301 enDocument10 pagesXL4301 enSelman ÇORANo ratings yet

- XL2596 enDocument16 pagesXL2596 enSelman ÇORANo ratings yet

- LM5030 Application: DC - DC Converter Utilizing The Push-Pull TopologyDocument10 pagesLM5030 Application: DC - DC Converter Utilizing The Push-Pull TopologyEdoardoNo ratings yet

- T2117 Zero-Voltage Switch With Adjustable Ramp PDFDocument16 pagesT2117 Zero-Voltage Switch With Adjustable Ramp PDFnenadNo ratings yet

- LM2727/LM2737 N-Channel FET Synchronous Buck Regulator Controller For Low Output VoltagesDocument26 pagesLM2727/LM2737 N-Channel FET Synchronous Buck Regulator Controller For Low Output Voltagesdavid.gjeorgevskiNo ratings yet

- Description Features: 1.2A 1.5Mhz 7V Synchronous Buck ConverterDocument7 pagesDescription Features: 1.2A 1.5Mhz 7V Synchronous Buck ConverterGeovanny SanJuanNo ratings yet

- XL7005A Datasheet-EnglishDocument10 pagesXL7005A Datasheet-EnglishEder Andrade Da SilvaNo ratings yet

- DM311Document16 pagesDM311Hernan Ortiz EnamoradoNo ratings yet

- AP3211Document11 pagesAP3211miteshNo ratings yet

- Data SheetDocument13 pagesData Sheethukam pariharNo ratings yet

- 1.5Mhz Step-Up DC-DC Converter Ap3012Document11 pages1.5Mhz Step-Up DC-DC Converter Ap3012Anderson gonçalvesNo ratings yet

- SSC9500 Application Note (Ver. 0.1) : Sanken Electric Co., LTDDocument19 pagesSSC9500 Application Note (Ver. 0.1) : Sanken Electric Co., LTDzhlikhonNo ratings yet

- Low Power PWM Controller For Off-Line Adapter Ap3710Document16 pagesLow Power PWM Controller For Off-Line Adapter Ap3710Abdulraouf DefnanyNo ratings yet

- BM1513 EtcDocument7 pagesBM1513 EtcDimas BarretoNo ratings yet

- Lps 5 eDocument8 pagesLps 5 eArifin IpinNo ratings yet

- Driver Backlight PSP 2000Document12 pagesDriver Backlight PSP 2000Jhonny GuillermoNo ratings yet

- Viper12Adip Viper12As: Low Power Off Line Smps Primary SwitcherDocument16 pagesViper12Adip Viper12As: Low Power Off Line Smps Primary Switchermohammed el erianNo ratings yet

- U2043b (Flasher)Document6 pagesU2043b (Flasher)JuanDiegoNo ratings yet

- Renesas R2A20113ASP#W5 DatasheetDocument13 pagesRenesas R2A20113ASP#W5 DatasheetbirricaNo ratings yet

- AX3005 AXEliteDocument11 pagesAX3005 AXElitebibib bibibNo ratings yet

- R2A20133DDocument14 pagesR2A20133DLuiz Augusto Freitas SantosNo ratings yet

- RZC2013 Buck Step DownDocument10 pagesRZC2013 Buck Step DownAgung DuemilanoveNo ratings yet

- Ic Driver LCD HP G5121 5121M PDFDocument9 pagesIc Driver LCD HP G5121 5121M PDFBudi PrayitnoNo ratings yet

- LM5008 High Voltage (100V) Step Down Switching Regulator: General Description FeaturesDocument15 pagesLM5008 High Voltage (100V) Step Down Switching Regulator: General Description FeaturesBrix MatacsilNo ratings yet

- ML4812CPDocument17 pagesML4812CPIntan LianaNo ratings yet

- Usb Boost Optional U5 Lp6252Document8 pagesUsb Boost Optional U5 Lp6252Sergio SeelingNo ratings yet

- A5268 3A, 28V, 340Khz Synchronous Rectified Step-Down ConverterDocument16 pagesA5268 3A, 28V, 340Khz Synchronous Rectified Step-Down ConverterAnderson Galarza CalderonNo ratings yet

- LM34910 High Voltage (40V, 1.25A) Step Down Switching RegulatorDocument12 pagesLM34910 High Voltage (40V, 1.25A) Step Down Switching RegulatorpowerlesssNo ratings yet

- AX2002 AXEliteDocument8 pagesAX2002 AXEliteMata Langit CCTVNo ratings yet

- A7431a PDFDocument15 pagesA7431a PDFDeguchi ChizuruNo ratings yet

- Viper22a PDFDocument20 pagesViper22a PDFMosqueda Notarion Phil JamesNo ratings yet

- Viper12Adip Viper12As: Low Power Off Line Smps Primary SwitcherDocument15 pagesViper12Adip Viper12As: Low Power Off Line Smps Primary SwitcherMakhou SoyoNo ratings yet

- LM2695 High Voltage (30V, 1.25A) Step Down Switching RegulatorDocument14 pagesLM2695 High Voltage (30V, 1.25A) Step Down Switching RegulatorYoyok CahyonoNo ratings yet

- DM0565RDocument20 pagesDM0565RSURESH CHANDRA ROUTNo ratings yet

- Datasheet AP7175Document14 pagesDatasheet AP7175Edwin SorianoNo ratings yet

- Training Msi MS-6+Document15 pagesTraining Msi MS-6+adaofisicoNo ratings yet

- Chipown: Low Standby-Power Quasi-Resonant Primary-Side ConverterDocument10 pagesChipown: Low Standby-Power Quasi-Resonant Primary-Side ConverterJoaquin Andres AlarconNo ratings yet

- Up 11541Document14 pagesUp 11541techgamebr85No ratings yet

- 3506 AfcDocument24 pages3506 AfcChristian ChavezNo ratings yet

- A3921 Datasheet PDFDocument21 pagesA3921 Datasheet PDFprashantbabuNo ratings yet

- KA5M0965Q: Fairchild Power Switch (SPS)Document14 pagesKA5M0965Q: Fairchild Power Switch (SPS)Jose Angel TorrealbaNo ratings yet

- AP1509Document12 pagesAP1509Андрей ОлененкоNo ratings yet

- C90691 - LM2596R 12 - 2016 12 17Document8 pagesC90691 - LM2596R 12 - 2016 12 17Nabla HarryNo ratings yet

- Control Circuit For Switch Mode Power Supplies Using Mos TransistorsDocument7 pagesControl Circuit For Switch Mode Power Supplies Using Mos TransistorsokeinfoNo ratings yet

- LM21305Document24 pagesLM21305Robert PNo ratings yet

- AT2003Document7 pagesAT2003williamsarenas75No ratings yet

- FA5604 3slg6dr2bxDocument30 pagesFA5604 3slg6dr2bxWagner MenezesNo ratings yet

- Lm2611 1.4-Mhz Cuk Converter: 1 Features 3 DescriptionDocument29 pagesLm2611 1.4-Mhz Cuk Converter: 1 Features 3 DescriptionrassyNo ratings yet

- LM5642 High Voltage, Dual Synchronous Buck Converter With Oscillator SynchronizationDocument24 pagesLM5642 High Voltage, Dual Synchronous Buck Converter With Oscillator SynchronizationcsclzNo ratings yet

- TB9000AFGDocument11 pagesTB9000AFGLoengrin MontillaNo ratings yet

- 12V 20ah Vrla Gel Battery 6-DZM-20: Features & BenefitsDocument2 pages12V 20ah Vrla Gel Battery 6-DZM-20: Features & BenefitsRafaelNo ratings yet

- Motorcycle WiringDocument78 pagesMotorcycle Wiringwule_master100% (1)

- Indent JSBayDocument7 pagesIndent JSBayTallapureddy SarweswarareddyNo ratings yet

- Subject: AEE Code: AU410705: UNIT-1 Automobile Electrical Systems and Electronics SystemDocument2 pagesSubject: AEE Code: AU410705: UNIT-1 Automobile Electrical Systems and Electronics SystemAniket PatilNo ratings yet

- Intenz Cb-150 RGB Cob Led Matrix BarDocument11 pagesIntenz Cb-150 RGB Cob Led Matrix BarPelle SchillingNo ratings yet

- P.E.S. College of Engineering, Mandya - 571 401Document2 pagesP.E.S. College of Engineering, Mandya - 571 401manoharaNo ratings yet

- 11-Step Procedure For A Successful Electrical Circuit Design (Low Voltage)Document7 pages11-Step Procedure For A Successful Electrical Circuit Design (Low Voltage)Mohammad Ather SiddiquiNo ratings yet

- Electrician Practical Skills Assessment Candidate GuideDocument8 pagesElectrician Practical Skills Assessment Candidate GuideSaravanan Rasaya100% (1)

- Abb EtuDocument40 pagesAbb Etukamal_khan85100% (1)

- Siemens MM4 - Engineering InformationDocument48 pagesSiemens MM4 - Engineering InformationRahul MohiteNo ratings yet

- Phone K33a42 Schematics L3 RepairDocument35 pagesPhone K33a42 Schematics L3 Repairprashanth handral0% (1)

- ALFOPlus80HDX OO CCDocument29 pagesALFOPlus80HDX OO CCmadoshaban21No ratings yet

- Bus Duct - Al-AhleiaDocument7 pagesBus Duct - Al-AhleiasedianpoNo ratings yet

- 5bb Jap672s01 SC 310 330 1500vDocument2 pages5bb Jap672s01 SC 310 330 1500vAshutosh SharmaNo ratings yet

- ELSSG02DDocument2 pagesELSSG02DJhonny RinconesNo ratings yet

- Baumer EAM580R-B-Analog EN 20230605 DSDocument5 pagesBaumer EAM580R-B-Analog EN 20230605 DSVijeesh T VargheseNo ratings yet

- Press Brake Estun E300 Installation ManualDocument98 pagesPress Brake Estun E300 Installation ManualJuan Carlos Sierra TilleriaNo ratings yet

- Caterpillar GeneratorDocument64 pagesCaterpillar GeneratorDon Freeman100% (3)

- Taser Final Document Print 6-29Document24 pagesTaser Final Document Print 6-29GiyoNo ratings yet

- Power Autotransformer 220//110/30 KV Unit Required Guarantee D Technical PerformancesDocument3 pagesPower Autotransformer 220//110/30 KV Unit Required Guarantee D Technical Performancesamulya00428No ratings yet

- Retrofit Panelboards Pow-R-Line 1RX and 2RX: Design Guide DG014006ENDocument29 pagesRetrofit Panelboards Pow-R-Line 1RX and 2RX: Design Guide DG014006ENdiegoNo ratings yet

- Mk5pfc ArticleDocument24 pagesMk5pfc ArticleenzolnNo ratings yet

- Alarm S at Bts SiteDocument53 pagesAlarm S at Bts Siteboldboy121100% (1)

- Chalmit Industrial Lighting - WellglassDocument3 pagesChalmit Industrial Lighting - WellglassSaswita SaktiNo ratings yet

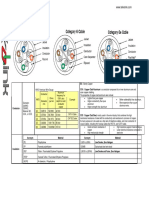

- UTP: Unshielded Twisted PairDocument3 pagesUTP: Unshielded Twisted PairSoumen PaulNo ratings yet

- BMXAMI0810Document20 pagesBMXAMI0810Pramudita Johan IswaraNo ratings yet

- Frequency Response of Instrument Transformers in The KHZ RangeDocument4 pagesFrequency Response of Instrument Transformers in The KHZ RangeburvanovNo ratings yet

- 3WL ManualDocument59 pages3WL ManualJuan MoralesNo ratings yet

- 9 - Electronic Devices PDFDocument28 pages9 - Electronic Devices PDFthinkiitNo ratings yet

- ACTOM Outdoor MV Switchgear - SingleDocument8 pagesACTOM Outdoor MV Switchgear - SingleKhashane Willy MohaleNo ratings yet