Professional Documents

Culture Documents

GW1N-1 Pinout

Uploaded by

June Anthony AsistioOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

GW1N-1 Pinout

Uploaded by

June Anthony AsistioCopyright:

Available Formats

GW1N series FPGA Products

GW1N-1 Pinout

Version History

Date Version Description

6/7/2018 1.04E Initial version published.

MBGA160 and PBGA204 deleted;

12/12/2018 1.05E Power requirements added.

3/12/2019 1.06E Recommended Operating Conditions for UV VCC modified.

© 2019 GOWINSEMI UG107-1.06E 1(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin Definitions

Pins Name Direction Description

User I/O Pins

[End] indicates the pin location, including L(left) R(right) B(bottom), and T(top)

[Row/Column Number] indicates the pin Row/Column number.

IO [End][Row/Column

I/O If [End] is T(top) or B(bottom), the pin indicates the Column number of the corresponding CFU.

Number][A/B]

If [End] is L(left) or R(right), the pin indicates the Row number of the corresponding CFU.

[A/B] indicaties differential signal pair information.

Multi-Function Pins

/MMM represents one or more of the other functions in addition to being general purpose user I/O.

IO [End][Row/Column Number][A/B]/MMM

When not used for the specical functions, these pins can be user I/O.

RECONFIG_N I, Internal Weak Pull Up Start new GowinCONFIG mode when low pulse

When high, device can be programmed and configured

READY I/O

When low, device cannot be programmed and configured

High indicates successful completion of programming and configuration

DONE I/O

Low indicates unfinished or failure of programming and configuration

In MSPI mode, FASTRD_N is used as Flash access speed port. Low indicates high-speed Flash

FASTRD_N/D3 I/O access mode; high indicates regular Flash access mode.

Data port D3 in CPU mode

Clock output MCLK in MSPI mode

MCLK/D4 I/O

Data port D4 in CPU mode

Enable signal MCS_N in MSPI mode, active-low

MCS_N/D5 I/O

Data port D5 in CPU mode

MOSI in MSPI mode:Master data output/Slave data input

MO/D6 I/O

Data port D6 in CPU mode

MISO in MSPI mode:Master data input/Slave data output

MI/D7 I/O

Data port D7 in CPU mode

Enable signal SSPI_CS_N in SSPI mode,active-low

SSPI_CS_N/D0 I/O

Data port D0 in CPU mode

MISO in SSPI mode:Master data input/Slave data output

SO/D1 I/O

Data port D1 in CPU mode

MOSI in SSPI mode:Master data output/Slave data input

SI/D2 I/O

Data port D2 in CPU mode

TMS I Serial mode input in JTAG mode

TCK I Serial clock input in JTAG mode

© 2019 GOWINSEMI UG107-1.06E 2(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin Definitions

Pins Name Direction Description

TDI I Serial data input in JTAG mode

TDO O Serial data output in JTAG mode

JTAGSEL_N I, Internal Weak Pull Up JTAG mode selection, active-low

SCLK I Clock input in SSPI, SERIAL, and CPU modes

DIN I, Internal Weak Pull Up Data input in SERIAL mode

DOUT O Data output in SERIAL mode

High, SCLK will be connected internally in SSPI mode or CPU mode

CLKHOLD_N I, Internal Weak Pull Up

Low, SCLK will be disconnected from SSPI mode or CPU mode

WE_N I Select data input/output of D[7:0] in CPU mode

GCLKT_[x] I Pins in Global clock input, T(True), [x]:global clock number.

GCLKC_[x] Pins in Global clock input, C(Comp), [x]: global clock number.

LPLL_T_fb/RPLL_T_fb I L/R PLL feedback input pins, T(True)

LPLL_C_fb/RPLL_C_fb I L/R PLL feedback input pins, C(Comp)

LPLL_T_in/RPLL_T_in I L/R PLL clock input pins,T(True)

LPLL_C_in/RPLL_C_in I L/R PLL clock input pins, C(Comp)

MODE2 I, Internal Weak Pull Up GowinCONFIG modes selection pin

MODE1 I, Internal Weak Pull Up GowinCONFIG modes selection pin

MODE0 I, Internal Weak Pull Up GowinCONFIG modes selection pin

Other Pins

NC NA Reserved.

VSS NA Ground.

VCC NA Power supply pins for the core voltage.

VCCO# NA Power supply pins for I/O voltage of I/O BANK#.

© 2019 GOWINSEMI UG107-1.06E 3(14)

GW1N series FPGA Products

GW1N-1 Pinout

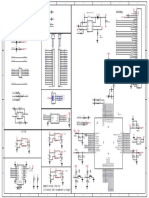

Bank

IO Bank0

IO Bank3 GW1N IO Bank1

IO Bank2

Note!

1.Each Bank has independent reference volatge (VREF);

2.Users can select to use IOB internal VREF(equals to 0.5*VCCO)

or external VREF input (use any IO pins as external VREF input).

© 2019 GOWINSEMI UG107-1.06E 4(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin List

Configuration

Pin Name Function BANK Differential Pair CS30 QN32 QN48 LQ100 LQ144

Function

IOB10A/GCLKT_5 I/O 2 GCLKT_5 True_of_IOB10B 17 39 56

IOB10B/GCLKC_5 I/O 2 GCLKC_5 Comp_of_IOB10A 18 40 57

IOB11A/GCLKT_4 I/O 2 GCLKT_4 True_of_IOB11B D3 4 19 41 58

IOB11B/GCLKC_4 I/O 2 GCLKC_4 Comp_of_IOB11A E3 5 20 42 59

IOB12A I/O 2 True_of_IOB12B 60

IOB12B I/O 2 Comp_of_IOB12A 43 61

IOB13A I/O 2 True_of_IOB13B 62

IOB13B I/O 2 Comp_of_IOB13A 63

IOB14A I/O 2 True_of_IOB14B 21 44 64

IOB14B I/O 2 Comp_of_IOB14A 22 45 65

IOB15A I/O 2 True_of_IOB15B 66

IOB15B I/O 2 Comp_of_IOB15A 67

IOB16A I/O 2 True_of_IOB16B 6 23 46 68

IOB16B I/O 2 Comp_of_IOB16A 24 47 69

IOB17A I/O 2 True_of_IOB17B 48 70

IOB17B I/O 2 Comp_of_IOB17A 49 71

IOB18A I/O 2 True_of_IOB18B

IOB18B I/O 2 Comp_of_IOB18A

IOB19A I/O 2 True_of_IOB19B 50 72

IOB19B I/O 2 Comp_of_IOB19A 75

IOB2A I/O 2 True_of_IOB2B 27 38

IOB2B I/O 2 Comp_of_IOB2A 28 39

IOB3A I/O 2 True_of_IOB3B 13 29 40

IOB3B I/O 2 Comp_of_IOB3A 14 30 41

IOB4A I/O 2 True_of_IOB4B 42

IOB4B I/O 2 Comp_of_IOB4A 43

IOB5A I/O 2 True_of_IOB5B 31 44

© 2019 GOWINSEMI UG107-1.06E 5(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin List

Configuration

Pin Name Function BANK Differential Pair CS30 QN32 QN48 LQ100 LQ144

Function

IOB5B I/O 2 Comp_of_IOB5A 32 45

IOB6A I/O 2 True_of_IOB6B 46

IOB6B I/O 2 Comp_of_IOB6A 15 33 47

IOB7A I/O 2 True_of_IOB7B 16 34 48

IOB7B I/O 2 Comp_of_IOB7A 49

IOB8A I/O 2 True_of_IOB8B 35 50

IOB8B I/O 2 Comp_of_IOB8A 36 51

IOB9A I/O 2 True_of_IOB9B 52

IOB9B I/O 2 Comp_of_IOB9A 54

IOL10A I/O 3 True_of_IOL10B E4 32 22 32

IOL10B I/O 3 Comp_of_IOL10A D4 1 23 34

IOL2A/JTAGSEL_N I/O 3 JTAGSEL_N True_of_IOL2B 3 4

IOL2B I/O 3 Comp_of_IOL2A 5 6

IOL3A I/O 3 True_of_IOL3B 7

IOL3B I/O 3 Comp_of_IOL3A 8

IOL4A I/O 3 True_of_IOL4B 9

IOL4B I/O 3 Comp_of_IOL4A 10

IOL5A/GCLKT_7 I/O 3 GCLKT_7 True_of_IOL5B C6 6 11

IOL5B/GCLKC_7 I/O 3 GCLKC_7 Comp_of_IOL5A C5 7 12

IOL6A/TMS I/O 3 TMS True_of_IOL6B C4 24 3 8 13

IOL6B/TCK I/O 3 TCK Comp_of_IOL6A A5 25 4 9 14

IOL6C/SCLK I/O 3 SCLK True_of_IOL6D C3 26 5 10 15

IOL6D/TDI I/O 3 TDI Comp_of_IOL6C B5 27 6 11 16

IOL6E/TDO I/O 3 TDO True_of_IOL6F B6 28 7 12 18

IOL6F/RECONFIG_N I/O 3 RECONFIG_N Comp_of_IOL6E 8 14 20

IOL6G/DONE I/O 3 DONE True_of_IOL6H 9 15 21

IOL6H/READY I/O 3 READY Comp_of_IOL6G 16 22

© 2019 GOWINSEMI UG107-1.06E 6(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin List

Configuration

Pin Name Function BANK Differential Pair CS30 QN32 QN48 LQ100 LQ144

Function

IOL6I I/O 3 True_of_IOL6J 23

IOL6J I/O 3 Comp_of_IOL6I 24

IOL7A/GCLKT_6 I/O 3 GCLKT_6 True_of_IOL7B D6 29 10 17 25

IOL7B/GCLKC_6 I/O 3 GCLKC_6 Comp_of_IOL7A D5 30 11 18 26

IOL8A I/O 3 True_of_IOL8B 19 27

IOL8B I/O 3 Comp_of_IOL8A 20 28

IOL9A I/O 3 True_of_IOL9B 29

IOL9B I/O 3 Comp_of_IOL9A 30

IOR10A I/O 1 True_of_IOR10B 55 78

IOR10B I/O 1 Comp_of_IOR10A 53 76

IOR2A I/O 1 True_of_IOR2B A3 17 73 106

IOR2B I/O 1 Comp_of_IOR2A B3 16 72 104

IOR3A I/O 1 True_of_IOR3B 102

IOR3B I/O 1 Comp_of_IOR3A 101

IOR4A/RPLL_T_fb I/O 1 RPLL_T_fb True_of_IOR4B A4 15 100

IOR4B/RPLL_C_fb I/O 1 RPLL_C_fb Comp_of_IOR4A 99

IOR5A/GCLKT_2/RPLL_T_in I/O 1 GCLKT_2/RPLL_T_in True_of_IOR5B B1 14 35 70 98

IOR5B/GCLKC_2/RPLL_C_in I/O 1 GCLKC_2/RPLL_C_in Comp_of_IOR5A B2 13 69 97

IOR6A/MI/D7 I/O 1 MI/D7 True_of_IOR6B 34 68 96

IOR6B/MO/D6 I/O 1 MO/D6 Comp_of_IOR6A 33 67 95

IOR6C/MCS_N/D5 I/O 1 MCS_N/D5 True_of_IOR6D 32 66 94

IOR6D/MCLK/D4 I/O 1 MCLK/D4 Comp_of_IOR6C 31 65 93

IOR6E/FASTRD_N/D3 I/O 1 FASTRD_N/D3 True_of_IOR6F 64 92

IOR6F/SI/D2 I/O 1 SI/D2 Comp_of_IOR6E E2 12 30 62 90

IOR6G/SO/D1 I/O 1 SO/D1 True_of_IOR6H D1 11 29 61 88

IOR6H/SSPI_CS_N/D0 I/O 1 SSPI_CS_N/D0 Comp_of_IOR6G D2 10 28 60 87

IOR6I/DIN/CLKHOLD_N I/O 1 DIN/CLKHOLD_N True_of_IOR6J 59 86

© 2019 GOWINSEMI UG107-1.06E 7(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin List

Configuration

Pin Name Function BANK Differential Pair CS30 QN32 QN48 LQ100 LQ144

Function

IOR6J/DOUT/WE_N I/O 1 DOUT/WE_N Comp_of_IOR6I 58 85

IOR7A/GCLKT_3 I/O 1 GCLKT_3 True_of_IOR7B C1 9 27 57 84

IOR7B/GCLKC_3 I/O 1 GCLKC_3 Comp_of_IOR7A C2 8 56 83

IOR8A I/O 1 True_of_IOR8B 82

IOR8B I/O 1 Comp_of_IOR8A 81

IOR9A I/O 1 True_of_IOR9B 80

IOR9B I/O 1 Comp_of_IOR9A 79

IOT10A I/O 0 True_of_IOT10B 22 43 91 130

IOT10B I/O 0 Comp_of_IOT10A 21 42 90 129

IOT11A I/O 0 True_of_IOT11B 20 89 128

IOT11B I/O 0 Comp_of_IOT11A 126

IOT12A I/O 0 True_of_IOT12B 86 124

IOT12B I/O 0 Comp_of_IOT12A 85 123

IOT13A I/O 0 True_of_IOT13B 122

IOT13B I/O 0 Comp_of_IOT13A 121

IOT14A I/O 0 True_of_IOT14B 41 84 120

IOT14B I/O 0 Comp_of_IOT14A 40 83 119

IOT15A I/O 0 True_of_IOT15B 82 118

IOT15B I/O 0 Comp_of_IOT15A 81 117

IOT16A I/O 0 True_of_IOT16B 80 116

IOT16B I/O 0 Comp_of_IOT16A 79 115

IOT17A I/O 0 True_of_IOT17B 39 78 114

IOT17B I/O 0 Comp_of_IOT17A 38 77 113

IOT2A I/O 0 True_of_IOT2B 3

IOT4A I/O 0 True_of_IOT4B 99 142

IOT4B I/O 0 Comp_of_IOT4A 98 141

IOT5A I/O 0 True_of_IOT5B 97 140

© 2019 GOWINSEMI UG107-1.06E 8(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin List

Configuration

Pin Name Function BANK Differential Pair CS30 QN32 QN48 LQ100 LQ144

Function

IOT5B I/O 0 Comp_of_IOT5A 46 96 139

IOT6A I/O 0 True_of_IOT6B 138

IOT6B I/O 0 Comp_of_IOT6A 137

IOT7A I/O 0 True_of_IOT7B 45 95 136

IOT7B I/O 0 Comp_of_IOT7A 44 94 135

IOT8A I/O 0 True_of_IOT8B 134

IOT8B I/O 0 Comp_of_IOT8A 133

IOT9A I/O 0 True_of_IOT9B 93 132

IOT9B I/O 0 Comp_of_IOT9A 92 131

IOT2B/MODE0 I/O 0 MODE0 Comp_of_IOT2A B4 23 48 100 144

IOT3B/MODE1 I/O 0 MODE1 Comp_of_IOT3A 47 143

IOT3A/MODE2 I/O 0 MODE2 True_of_IOT3B

NC N/A N/A 112

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A 110

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A 111

© 2019 GOWINSEMI UG107-1.06E 9(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin List

Configuration

Pin Name Function BANK Differential Pair CS30 QN32 QN48 LQ100 LQ144

Function

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

NC N/A N/A

VCC Power N/A

VCC Power N/A

© 2019 GOWINSEMI UG107-1.06E 10(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin List

Configuration

Pin Name Function BANK Differential Pair CS30 QN32 QN48 LQ100 LQ144

Function

VCC Power N/A

VCC Power N/A

VCC Power N/A

VCC Power N/A

VCC Power N/A

VCC Power N/A

VCC Power N/A 1 1

VCC Power N/A 2 12 25 36

VCC Power N/A 51 73

VCC Power N/A E6 18 37 75 108

VCCO0 Power N/A

VCCO0 Power N/A

VCCO0 Power N/A

VCCO0 Power N/A

VCCO0 Power N/A 19 76 109

VCCO0 Power N/A 88 127

VCCO0/VCCO3 Power N/A A6 1

VCCO1 Power N/A

VCCO1 Power N/A

VCCO1 Power N/A

VCCO1 Power N/A 54 77

VCCO1 Power N/A 63 91

VCCO1 Power N/A 36 71 103

VCCO1/VCCO2 Power N/A A1

VCCO1/VCCO2 Power N/A E1 7

VCCO2 Power N/A

VCCO2 Power N/A

© 2019 GOWINSEMI UG107-1.06E 11(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin List

Configuration

Pin Name Function BANK Differential Pair CS30 QN32 QN48 LQ100 LQ144

Function

VCCO2 Power N/A

VCCO2 Power N/A

VCCO2 Power N/A 26 37

VCCO2 Power N/A 38 55

VCCO2 Power N/A 25

VCCO3 Power N/A

VCCO3 Power N/A

VCCO3 Power N/A

VCCO3 Power N/A 4 5

VCCO3 Power N/A 13 19

VCCO3 Power N/A 31 21 31

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

© 2019 GOWINSEMI UG107-1.06E 12(14)

GW1N series FPGA Products

GW1N-1 Pinout

Pin List

Configuration

Pin Name Function BANK Differential Pair CS30 QN32 QN48 LQ100 LQ144

Function

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A

VSS Ground N/A 2 2 2

VSS Ground N/A 17

VSS Ground N/A 33

VSS Ground N/A E5 3 24 35

VSS Ground N/A 37 53

VSS Ground N/A 26 52 74

VSS Ground N/A 89

VSS Ground N/A 105

VSS Ground N/A A2 74 107

VSS Ground N/A 87 125

© 2019 GOWINSEMI UG107-1.06E 13(14)

GW1N series FPGA Products

GW1N-1 Pinout

Power

Recommended Operating Conditions for GW1N-1

Name Description Min. Max.

LV: Core Power 1.14V 1.26V

VCC

UV:Core Power 1.71V 3.465V

VCCO0、VCCO1 I/O Bank Power for LV 1.14V 3.465V

VCCO2、VCCO3 I/O Bank Power for UV 2.375V 3.465V

VCCX Auxiliary voltage 2.375V 3.465V

© 2019 GOWINSEMI UG107-1.06E 14(14)

You might also like

- Raspberry WiringPiDocument26 pagesRaspberry WiringPiMircea TirziuNo ratings yet

- AGC 150 TrainingDocument71 pagesAGC 150 TrainingVinesh VineshbNo ratings yet

- Lab 1 Introduction To Stm32F103 and Ide: St-Link V2 and Keil Uvision5Document33 pagesLab 1 Introduction To Stm32F103 and Ide: St-Link V2 and Keil Uvision5Kiều NguyễnNo ratings yet

- Oval That Corresponds To Your Answer.: I. OutcomesDocument4 pagesOval That Corresponds To Your Answer.: I. OutcomesClarissa DamayoNo ratings yet

- NodeMCU TutorialDocument49 pagesNodeMCU Tutorialv_ananthuNo ratings yet

- Esp32 PDFDocument5 pagesEsp32 PDFIrfan ZuhriNo ratings yet

- Preliminary: 01/05/2023 1.0E Initial Version Published. Package FPG676A SupportedDocument44 pagesPreliminary: 01/05/2023 1.0E Initial Version Published. Package FPG676A SupportedJOSE FRANÇANo ratings yet

- UG982-1.0E - GW5AT-138 Pinout-PreliminaryDocument44 pagesUG982-1.0E - GW5AT-138 Pinout-PreliminaryJOSE FRANÇANo ratings yet

- PIC16F628Document30 pagesPIC16F628Prince YehyaNo ratings yet

- Virtex™-E 1.8 V Extended Memory Field Programmable Gate ArraysDocument42 pagesVirtex™-E 1.8 V Extended Memory Field Programmable Gate ArraysAlex WongNo ratings yet

- Proc Embarqué - Ch5Document47 pagesProc Embarqué - Ch5test testNo ratings yet

- Boron DatasheetDocument30 pagesBoron DatasheetIsaac FriesenNo ratings yet

- PIC16F87XA: TABLE 1-2: Pic16F873A/876A Pinout Description (Continued)Document5 pagesPIC16F87XA: TABLE 1-2: Pic16F873A/876A Pinout Description (Continued)vitor valeNo ratings yet

- StrataFlash 28F640J3Document37 pagesStrataFlash 28F640J3Alexandre Anderson AlvesNo ratings yet

- Act3 Arduino BurgosDocument4 pagesAct3 Arduino BurgosCharles BurgosNo ratings yet

- 980802b Dio ModDocument4 pages980802b Dio Modsyed jeelani ahmedNo ratings yet

- Programming Embedded Systems (Microcontrolers) : What We Will SeeDocument12 pagesProgramming Embedded Systems (Microcontrolers) : What We Will SeeHadil SadokNo ratings yet

- Data SheetDocument14 pagesData SheetFBC Quality ControlNo ratings yet

- Specification: Product Model NumberDocument10 pagesSpecification: Product Model Numberanggun nurfitrianiNo ratings yet

- MY84SPK02M2: Bluetooth 3.0+EDR Stereo Audio ModuleDocument5 pagesMY84SPK02M2: Bluetooth 3.0+EDR Stereo Audio ModuleTvenson SalmineNo ratings yet

- Lab 2Document7 pagesLab 2Md AssadNo ratings yet

- Lab 5 - Loop: EB006 Options Setting Jumper Settings (EB006) Jumper Settings (HP488)Document4 pagesLab 5 - Loop: EB006 Options Setting Jumper Settings (EB006) Jumper Settings (HP488)John MalgapoNo ratings yet

- 8255 Um CommonDocument55 pages8255 Um CommonChaitanya KommuNo ratings yet

- I/O Multiplexing: Name-Akash Thakur ROLL NO-17BT020403 SEM-6th Branch-EceDocument9 pagesI/O Multiplexing: Name-Akash Thakur ROLL NO-17BT020403 SEM-6th Branch-EceAkash ThakurNo ratings yet

- MY81SPK02M2: Bluetooth 3.0+EDR Stereo Audio ModuleDocument5 pagesMY81SPK02M2: Bluetooth 3.0+EDR Stereo Audio Modulearness22No ratings yet

- Chapter 6 Basic Input and Output InterfaceDocument38 pagesChapter 6 Basic Input and Output InterfacePetra Kalasa100% (1)

- Microcontroller Unit LED Display Unit: OBJECTIVE: To Design A Microcontroller System Using The In-SystemDocument20 pagesMicrocontroller Unit LED Display Unit: OBJECTIVE: To Design A Microcontroller System Using The In-SystemSubhakant RoutNo ratings yet

- 2.13inch E-Paper DatasheetDocument26 pages2.13inch E-Paper Datasheetvjspd hppNo ratings yet

- zsm00123 f5020Document4 pageszsm00123 f5020Team ViemerNo ratings yet

- ForgeFPGA Configuration Guide v2.1Document20 pagesForgeFPGA Configuration Guide v2.1HnnNo ratings yet

- Lab 6Document4 pagesLab 6John MalgapoNo ratings yet

- IV Unit MPI Modified On 4-4-19Document48 pagesIV Unit MPI Modified On 4-4-19Darshan BysaniNo ratings yet

- Unit-Iv Microcontroller Fundamentals For Basic Programming: GpiosDocument21 pagesUnit-Iv Microcontroller Fundamentals For Basic Programming: GpiossrikanthNo ratings yet

- Bakup Dulieu Bang rs232Document9 pagesBakup Dulieu Bang rs232tan duyNo ratings yet

- Section 2 - Port Control On SAMD20: TasksDocument18 pagesSection 2 - Port Control On SAMD20: TasksjmsaakNo ratings yet

- Multiple Choices Huawei HCIADocument16 pagesMultiple Choices Huawei HCIAAugusto LimeraNo ratings yet

- I-7000 m-7000 Quick Start en v1.40Document4 pagesI-7000 m-7000 Quick Start en v1.40phachayoNo ratings yet

- Introduction To ARDUINODocument25 pagesIntroduction To ARDUINOmr.mohamada.mohamadNo ratings yet

- W83758FDocument15 pagesW83758Fguerrero_rjNo ratings yet

- Chapter 4 Programmable Peripheral InterfaceDocument49 pagesChapter 4 Programmable Peripheral InterfacetesfayebbNo ratings yet

- ESD NPTEL SummaryDocument35 pagesESD NPTEL SummaryrahulpikaleNo ratings yet

- Embetronicx Com Tutorials Microcontrollers stm32 stm32 GpioDocument27 pagesEmbetronicx Com Tutorials Microcontrollers stm32 stm32 Gpiovictor sanchezNo ratings yet

- Lecture 5 Communicating With Peripherals 2021Document44 pagesLecture 5 Communicating With Peripherals 2021Pavan DhakeNo ratings yet

- TC78H660FTG Datasheet en 20200714Document26 pagesTC78H660FTG Datasheet en 20200714ehsanNo ratings yet

- Chapter 3 Electronics: Edition: 2-1Document17 pagesChapter 3 Electronics: Edition: 2-1Karla DiazNo ratings yet

- Koyo Plcs 405Document60 pagesKoyo Plcs 405Ysabel Cristina Yaguaracuto TorrealbaNo ratings yet

- Profibus DP Interface User GuideDocument2 pagesProfibus DP Interface User GuidePAUL PIERRE PIMENTEL COBE�ASNo ratings yet

- AC6901A规格书V1 2Document13 pagesAC6901A规格书V1 2ghNo ratings yet

- AC6905A规格书V1 0Document10 pagesAC6905A规格书V1 0gonglun liNo ratings yet

- Pin NameDocument3 pagesPin NameKrishna BandlaNo ratings yet

- AC6905A JieliDocument10 pagesAC6905A JieliDARWYN MAURICIO HERNANDEZ JUAREZNo ratings yet

- Ac6905a DatasheepDocument10 pagesAc6905a DatasheepMUSIC ELECNo ratings yet

- GPIO Option: 92-2427-01 Rev.CDocument14 pagesGPIO Option: 92-2427-01 Rev.CAchraf HouilaNo ratings yet

- 07 Digital IO Interfacing and ProgrammingDocument5 pages07 Digital IO Interfacing and Programming2017ee184No ratings yet

- AC6901A DatasheetDocument13 pagesAC6901A DatasheetIgor LevochkinNo ratings yet

- Arduino Uno & Respbarry Pi & Node Mcu CodesDocument29 pagesArduino Uno & Respbarry Pi & Node Mcu CodesFiza ShakeelNo ratings yet

- Lesson 4 Fpga I/O: TopicsDocument33 pagesLesson 4 Fpga I/O: Topicsdimen100No ratings yet

- AC6900A规格书V1 2Document14 pagesAC6900A规格书V1 2ghNo ratings yet

- Lm128128cby TopwayDocument14 pagesLm128128cby Topwaynb7g8lmel9No ratings yet

- Coding The Arduino: "Embedded Systems"Document21 pagesCoding The Arduino: "Embedded Systems"thap_dinhNo ratings yet

- Implementing A Secure Digital Card With A ZNEO MicrocontrollerDocument39 pagesImplementing A Secure Digital Card With A ZNEO MicrocontrollerJune Anthony AsistioNo ratings yet

- Technological University of The Philippines: Logic Circuits and Switching TheoryDocument2 pagesTechnological University of The Philippines: Logic Circuits and Switching TheoryJune Anthony AsistioNo ratings yet

- Tang NANO 2704 (Schematic)Document1 pageTang NANO 2704 (Schematic)June Anthony Asistio100% (1)

- Temperature Sensor Module On 8-Bit PIC MicrocontrollersDocument7 pagesTemperature Sensor Module On 8-Bit PIC MicrocontrollersJune Anthony AsistioNo ratings yet

- CIP Hybrid Power Starter Kit User's GuideDocument61 pagesCIP Hybrid Power Starter Kit User's GuideJune Anthony AsistioNo ratings yet

- Peripheral Pin Select in 8-Bit Microcontrollers Technical BriefDocument12 pagesPeripheral Pin Select in 8-Bit Microcontrollers Technical BriefJune Anthony AsistioNo ratings yet

- TB3155 Multiphase Interleaved PWM Controller With Diode Emulation DS90003155BDocument14 pagesTB3155 Multiphase Interleaved PWM Controller With Diode Emulation DS90003155BJune Anthony AsistioNo ratings yet

- 2 Demystifying Vias in High-Speed PCB DesignsDocument30 pages2 Demystifying Vias in High-Speed PCB DesignsJune Anthony AsistioNo ratings yet

- Operational Amplifier Pspice Model of 8-Bit Pic MicrocontrollersDocument18 pagesOperational Amplifier Pspice Model of 8-Bit Pic MicrocontrollersJune Anthony AsistioNo ratings yet

- Mpasm Users GuideDocument164 pagesMpasm Users GuideJune Anthony AsistioNo ratings yet

- The Sign of The FourDocument77 pagesThe Sign of The FourJune Anthony AsistioNo ratings yet

- Artificial Intelligence: Frames and ScriptsDocument5 pagesArtificial Intelligence: Frames and ScriptsJune Anthony AsistioNo ratings yet

- Scheme of Valuation - April - 2022: Subject: Computer Science CODE: 41 Version: EnglishDocument13 pagesScheme of Valuation - April - 2022: Subject: Computer Science CODE: 41 Version: EnglishRahil HassanNo ratings yet

- What Are Data Center Tiers - FS CommunityDocument5 pagesWhat Are Data Center Tiers - FS CommunityTritech internationalNo ratings yet

- 7376212AD124Document2 pages7376212AD124AZHARUDEEN SNo ratings yet

- Employee Central 4Document7 pagesEmployee Central 4AxleNo ratings yet

- 21EEL305-ASP-Lab ManualDocument51 pages21EEL305-ASP-Lab ManualShivakumar 2108No ratings yet

- CT026-3-2 Human Computer Interaction Incourse QuestionDocument7 pagesCT026-3-2 Human Computer Interaction Incourse Questionjames smithNo ratings yet

- Packet TracerDocument7 pagesPacket TracerEgi WiratamaNo ratings yet

- CCIE SECv5 LAB1 Configuration Question SetDocument4 pagesCCIE SECv5 LAB1 Configuration Question SetJanek PodwalaNo ratings yet

- Google AiDocument4 pagesGoogle AiMichael SeerNo ratings yet

- LogDocument53 pagesLogAisyahNo ratings yet

- DVP-200 Data SheetDocument2 pagesDVP-200 Data SheetTeddy MatthewNo ratings yet

- 09 - I3A - Algoritma Pemrograman - 41.19.0009 - Hanif ArdyansyahDocument7 pages09 - I3A - Algoritma Pemrograman - 41.19.0009 - Hanif ArdyansyahHanif ArdyansyahNo ratings yet

- Sophos Firewall Competitive OverviewDocument2 pagesSophos Firewall Competitive OverviewfathanNo ratings yet

- Modicon M221 - TM221C24RDocument17 pagesModicon M221 - TM221C24RCristian TruccoNo ratings yet

- BBA-104 Unit-1 Fundamentals-of-Computers NotesDocument24 pagesBBA-104 Unit-1 Fundamentals-of-Computers NotesCoin Seller PrashantNo ratings yet

- Mod 7 - LNDocument114 pagesMod 7 - LNDurai GopalNo ratings yet

- Weighted Graphs and Dijkstra's AlgorithmDocument18 pagesWeighted Graphs and Dijkstra's AlgorithmrakeshjainrulzNo ratings yet

- CAED Project PDFDocument5 pagesCAED Project PDFUsama AameerNo ratings yet

- Resume - Bibilomo Sanni 11-2023Document2 pagesResume - Bibilomo Sanni 11-2023api-708484789No ratings yet

- Aoc 32 SPX322Document4 pagesAoc 32 SPX322Muhammad AinurofikNo ratings yet

- Smart TrolleyDocument55 pagesSmart TrolleySahithiNo ratings yet

- DBA Module 2Document16 pagesDBA Module 2melkamu endaleNo ratings yet

- Teslaaa 1Document20 pagesTeslaaa 1Diwakar DiwakarNo ratings yet

- Alvaro Pinilla Guerrero CVDocument2 pagesAlvaro Pinilla Guerrero CValvaro pinillaNo ratings yet

- Data TypesDocument5 pagesData Typesmandava venkata sudheer kumarNo ratings yet

- Systemmanager PreviousDocument88 pagesSystemmanager PreviouspatrickbreurNo ratings yet

- HCM Mobile ApplicationDocument19 pagesHCM Mobile Applicationzafar.ccna1178No ratings yet

- 6-2 Milestone Husky X2 Specification SheetDocument2 pages6-2 Milestone Husky X2 Specification SheetYasser Al EmadiNo ratings yet

- Sartorius Manual Dcu-Host Interface 1 - 6Document40 pagesSartorius Manual Dcu-Host Interface 1 - 6Carlos Alberto Ramirez GarciaNo ratings yet