Professional Documents

Culture Documents

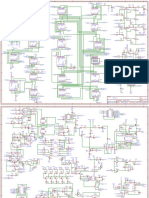

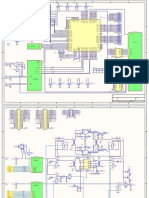

(Rs1) (RD) (Rs2) : U11 Registerfile

Uploaded by

Rajini KasalaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

(Rs1) (RD) (Rs2) : U11 Registerfile

Uploaded by

Rajini KasalaCopyright:

Available Formats

1 2 3 4 5

U11

RegisterFile

rd_clk 1 5 insn[19..15] (rs1)

WR AA

(rd) insn[24..20] 2 6 rs1_val[31..0]

WA AD

rd_val[31..0] 3 7 insn[24..20] (rs2)

A WD BA A

reset 4 8 rs2_val[31..0]

Reset BD

pc_alu_sel

U12

U16 U15

A0

4

I1 U13 U14

Q

rd_sel[1]

A1 A Q

pc_alu[31..0]

rd_sel[0] I0

I1

I0

I0

I1

A0 alu_a_sel alu_b__sel

Q + A0 A0

I3

I2

I1

I0

Q

B

U18

U17 PC

pc_clk

Cp

I0 pc[31..0] U19

Q Din Dout

mem_sx[31..0]

I1 reset ALU

A0

RESET

B

Func

A<UB

pc_next_sel sub/sra

A<B

EQ

imm_x[4..0]

Q

shamt

B B

U20 Sheet: imm_sx

sx

imm_x[31..0]

File: mbr_sx.sch

INSN insn imm_x

Sheet: mbr_sx

insn_clk

Cp File: imm_sx.sch

insn[31..0]

Din Dout

reset

size

mbr

RESET

sx_size[2..0]

alu[31..0]

U21

I1

I0

addr_sel Sheet: control_fsm

A0 sub_sra

sub_sra

alu_func[2..0]

Q

func

addr_sel

addr_sel

rd_sel[1..0]

C A<UB rd_sel[1..0] C

alu_a_sel

mem_out[31..0]

A<B alu_a_sel

U22 alu_b_sel

EQ alu_b_sel

MEM insn[6..0] mem_clk

addr[31..0] opcode mem_clk

insn[14..12] rd_clk

funct3 rd_clk

ReadAddress insn[30] pc_clk

sub_sra_in pc_clk

WriteAddress insn_clk

mem_clk ir_clk

WE pc_alu_sel

pc_alu_sel

Dout Din pc_next_sel

pc_next_sel

rs2_val[31..0] sx_size[2..0]

sx_size[2..0]

CLK reset

reset

File: control.sch

D D

Sheet: /

File: rv32i.sch

Title: RV32I

Size: A Date: 2021-10-04 Rev: 1.1

KiCad E.D.A. kicad 5.1.5+dfsg1-2build2 Id: 1/4

1 2 3 4 5

You might also like

- Sample DrawingDocument1 pageSample DrawingrsubramaniNo ratings yet

- Sblo - Rnav Edpud 1a Rwy 31 - Sid - 20230126Document1 pageSblo - Rnav Edpud 1a Rwy 31 - Sid - 20230126Rodrigo BarretoNo ratings yet

- C6 MB SCH V3.0 20160928 1933 PDFDocument34 pagesC6 MB SCH V3.0 20160928 1933 PDFIdfi IsnandarNo ratings yet

- Pump Body With VatDocument1 pagePump Body With Vatadtijanic-1100% (1)

- 01 670 Series Training Set UpDocument4 pages01 670 Series Training Set UpHope DandaraNo ratings yet

- Demi Winner X Ble: Demi Left Demi RightDocument1 pageDemi Winner X Ble: Demi Left Demi RightTu Do100% (2)

- Panasonic Gd55 SchematicsDocument10 pagesPanasonic Gd55 SchematicsEdgar Jose Aranguibel MorilloNo ratings yet

- G5 MB WSCH V1.0 160701Document31 pagesG5 MB WSCH V1.0 160701setrabporciunculaNo ratings yet

- SBSG - Rnav Vacar 1d Rwy 12 - Star - 20190103Document1 pageSBSG - Rnav Vacar 1d Rwy 12 - Star - 20190103Marcos Jesus RibeiroNo ratings yet

- Math11 6531503157Document3 pagesMath11 6531503157MIN THUTA NAING -No ratings yet

- (Star) Standard Arri VAL Chart I Nstrum Ent: RWY 11 Rnav KI BAP 1A - Vasog 1ADocument2 pages(Star) Standard Arri VAL Chart I Nstrum Ent: RWY 11 Rnav KI BAP 1A - Vasog 1ARafael LinckNo ratings yet

- Lowrance X-55Document20 pagesLowrance X-55Lily Cheng100% (1)

- G ClampDocument3 pagesG ClampFRESKABIO0% (1)

- Schematic T 4 2023-05-04Document2 pagesSchematic T 4 2023-05-04dinh vinh nguyenNo ratings yet

- SBRJ Evsob-1d-Rwy-20l Sid 20210520Document1 pageSBRJ Evsob-1d-Rwy-20l Sid 20210520brunogasperinNo ratings yet

- SBCF Mugra-1a-Rwy-34 Sid 20210225Document1 pageSBCF Mugra-1a-Rwy-34 Sid 20210225Vinicius LinsNo ratings yet

- A5s (CPH1909)Document23 pagesA5s (CPH1909)Ayman EbrahemNo ratings yet

- TimerDocument1 pageTimerВадим МкртчянNo ratings yet

- SBRJ - Evsob 1b Rwy 02r - Sid - 20210520Document1 pageSBRJ - Evsob 1b Rwy 02r - Sid - 20210520Lucas FuterkoNo ratings yet

- Скан 17 июня 17 г.Document1 pageСкан 17 июня 17 г.Никита ВеликоцкийNo ratings yet

- 618a-2047 00.asDocument1 page618a-2047 00.aspradeep kumar DasNo ratings yet

- ControlPCB SchematicDocument1 pageControlPCB Schematicjesus torgarNo ratings yet

- Sbpa - Rnav Dakat 1b Rwy 29 - Star - 20230810Document1 pageSbpa - Rnav Dakat 1b Rwy 29 - Star - 20230810CMDT MatheusNo ratings yet

- Peta Plan Tes Pit KokoeDocument1 pagePeta Plan Tes Pit KokoeAlminNo ratings yet

- Latihan 24Document1 pageLatihan 24septya hanantaNo ratings yet

- Statistics AssignmentDocument4 pagesStatistics AssignmentRushil DuttaNo ratings yet

- Assignment ClassDocument2 pagesAssignment ClassVictoriaNo ratings yet

- nc1 60 200Document19 pagesnc1 60 200thongo trương quangNo ratings yet

- DiseñoDocument1 pageDiseñosantiago carvajalNo ratings yet

- IA3 - BE41 - Signed PDFDocument1 pageIA3 - BE41 - Signed PDFNyoman ParamarthaNo ratings yet

- Potencia E-Sound vx-1500 - SCHDocument1 pagePotencia E-Sound vx-1500 - SCHCarlos Winter100% (2)

- IoiuyDocument4 pagesIoiuyAul FiNo ratings yet

- K - Helical Bevel: K.. AM.. (NEMA Dimensions)Document1 pageK - Helical Bevel: K.. AM.. (NEMA Dimensions)sanatikalaNo ratings yet

- Fig 213Document3 pagesFig 213Academecian groupNo ratings yet

- Cuando Pase El Temblor - BajoDocument4 pagesCuando Pase El Temblor - Bajonicole mNo ratings yet

- PDU24HS General CircuitDocument1 pagePDU24HS General CircuitAndre BagaNo ratings yet

- UterrorDocument1 pageUterrordavNo ratings yet

- View A: 1.1761.1134-2 Allowable Load Lashing Carrier G HMK 6 - 07Document1 pageView A: 1.1761.1134-2 Allowable Load Lashing Carrier G HMK 6 - 07altogarNo ratings yet

- 8259 Programmable Interrupt Controller Application: Experiment #10Document10 pages8259 Programmable Interrupt Controller Application: Experiment #10Asaad HalayqaNo ratings yet

- SBGR - Rnav Edlut 1a Rwy 10r 10l - Sid - 20220908Document1 pageSBGR - Rnav Edlut 1a Rwy 10r 10l - Sid - 20220908Douglas Souza de MatosNo ratings yet

- Sbae - Rnav Lutvi 1a - Nevku 1a - Oprak 1a Rwy 35 - Sid - 20180524Document1 pageSbae - Rnav Lutvi 1a - Nevku 1a - Oprak 1a Rwy 35 - Sid - 20180524Edoardo MarkezNo ratings yet

- 100R R3 K12 100R R2 K11 K5 K2: QuantumopticsDocument1 page100R R3 K12 100R R2 K11 K5 K2: QuantumopticsbaymanNo ratings yet

- GeeBee R1Document7 pagesGeeBee R1Lorenzo Martinez ValenzuelaNo ratings yet

- 原理图 - MB (DIAGRAMAS.COM.BR)Document36 pages原理图 - MB (DIAGRAMAS.COM.BR)Solução MakerNo ratings yet

- O.In/O.522, O-335J: en - Njlo.La V-0-5N-Oe - TVDocument1 pageO.In/O.522, O-335J: en - Njlo.La V-0-5N-Oe - TV林宜伈No ratings yet

- AM 336 2015 - Shelley-ByronDocument1 pageAM 336 2015 - Shelley-ByronsNo ratings yet

- ULTEGRA Front Chainwheel FC-6600Document1 pageULTEGRA Front Chainwheel FC-6600jack87hornistNo ratings yet

- UntitledDocument1 pageUntitledJorge JorgeNo ratings yet

- EduShield SchematicDocument1 pageEduShield SchematicPlaymr 365No ratings yet

- VILLAvicencio PDFDocument154 pagesVILLAvicencio PDFluisNo ratings yet

- Tesya Hasan Roller Bracket PartDocument1 pageTesya Hasan Roller Bracket PartTesya Hasan Zein MahmudNo ratings yet

- Desen SUPORT CAPUITOR ALUMINIUDocument1 pageDesen SUPORT CAPUITOR ALUMINIUISTVÁN GYENGENo ratings yet

- SBCT - Rnav Isnix 1b - Mudat 1b Rwy 33 - Star - 20210520Document1 pageSBCT - Rnav Isnix 1b - Mudat 1b Rwy 33 - Star - 20210520Paulo SilvaNo ratings yet

- Yo SDRDocument9 pagesYo SDRfox7878No ratings yet

- OFF ON: Brayan Andres Gutierres y Gabriel Abella .PDSPRJ 12/06/2020 Brayan Andres Gutierres y Gabriel Abella .PDSPRJDocument1 pageOFF ON: Brayan Andres Gutierres y Gabriel Abella .PDSPRJ 12/06/2020 Brayan Andres Gutierres y Gabriel Abella .PDSPRJBrayan GutierrezNo ratings yet

- O 4 999 Hheg: IaeasDocument17 pagesO 4 999 Hheg: Iaeasxsffg2xbshNo ratings yet

- Ignition Transformer For MS5001Document3 pagesIgnition Transformer For MS5001Chidiebere Samuel OkogwuNo ratings yet

- Programmable Time Delay Relays CX 38 39 PDFDocument4 pagesProgrammable Time Delay Relays CX 38 39 PDFaffanNo ratings yet

- t7 b3 CVR Notes - NTSB FDR - Aa 77 NTSB FDR Analysis 316Document17 pagest7 b3 CVR Notes - NTSB FDR - Aa 77 NTSB FDR Analysis 3169/11 Document ArchiveNo ratings yet