Professional Documents

Culture Documents

2010 AM-FPD - On-Panel Readout Circuit For Capacitive Sensor With LTPS Technology

2010 AM-FPD - On-Panel Readout Circuit For Capacitive Sensor With LTPS Technology

Uploaded by

GiancarloRichardRivadeneyraMiranda0 ratings0% found this document useful (0 votes)

29 views4 pagesOriginal Title

2010 AM-FPD_On-panel readout circuit for capacitive sensor with LTPS technology

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

29 views4 pages2010 AM-FPD - On-Panel Readout Circuit For Capacitive Sensor With LTPS Technology

2010 AM-FPD - On-Panel Readout Circuit For Capacitive Sensor With LTPS Technology

Uploaded by

GiancarloRichardRivadeneyraMirandaCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 4

P-8

On-Panel Readout Circuit for Capacitive Sensor with LTPS Technology

Yu-Ta Lin', Yu-Chieh Lin', Tzu-Ming Wang! , and Ming-Dou Ker'?

"Nanoelectronics and Gigaseale Systems Laboratory

Institute of Electronies, National Chiao-Tung University

1001 Ta-Hsueh Road, Hsinchu, Taiwan 300, R.O.C.

*Dept. of Electronic Engineering, I-Shou University, Kaohsuing, Taiwan.

New configuration of on-panel readout citcuit for eapacitive sensor s

table for low temperature polysilicon (LTPS) thin-

film transistor (TFT) process has been proposed. In this work, switch capacitor (SC) technique is applied to compensate

the impact of threshold voltage (V.,) vari

jon owing to LTPS process variation on readout

ircut, To further identify the

different touch position by conductive object, a 2-bit analog-to-digital converter is used to convert the output of readout

circuit into 2-bit digital codes,

1. Introduction

Low temperature polyerystaline silicon (LTPS)

thin-film ransistors (TFTs) have been widely

investigated as a material for portable systems, such as

digital camera, mobile phone, personal dig

(PDAS), notebook, and so on. Furthermore, LTPS

technology can achieve slim, compact, and high-

resolution display by integrating driving circuits, analog

digital converters (ADO, timing controller ete. on the

peripheral area of display. poly-Si TFT

characteristics, such as high carrier mobility, low

threshold voltage, high stability, and high reliability, are

required to fulfil the SOP application [1], (2)

In last few years, integrating touch panel into glass

substrate has attracted much attention because the

aforesaid advantages. Touch panels used in mobile

applications are mainly resistive or capacitive. Although

resistive touch panel ean achieve low cost and rarely

malfunction, it has some drawbacks including serious

glare, low transmittance and single touch only. On the

other hand, capacitive toueh panel ean realize multi

touch funetionality easily which allows user to operate

information instruments more intuitively [3]

However, because most LTPS TFTs are based on

‘excimer laser crystallized poly-Si, random orientation of

poly-Si grains, grain size variation, and incomplete

termination of grain boundaries lead to a quite large

threshold vollage variation of TFT device which

contributes to serious impact on the accuracy of analog

circuits [4}(5}

assistants

Some

In this work, a new readout circuit for capacitive

sensor on glass in LTPS fabrication process has been,

proposed. The switch capacitance (SC) technique is used to

compensate the threshold voltage variation effect, Different

value of sensed capacitance can be judged by ADC. In this,

‘way, the overall resolution for touch panel can be enhanced.

by interpolation method,

2. Equivalent Model of The Capacitive Sensor Line

Capacitive sensor fine can be modeled as a series of

RC string on the 2.8 inch panel with total R = 150KQ.and C

= 100pF shown in Fig. 1. Fanout is the equivalent parasitic

RC of interconnect line between the sensor line to the

output node Fin, Each node is pre-charged to the supply

voltage (VDDA). When conductive objects such as finger

touch the surface of touch panel, the touch capacitance Ct is,

connected to the equivalent circuit. Because of charge

sharing, this capacitance results in a voltage variance on the

node Fin and the final value of Vr, can be expressed as:

Ctotal

DDAx —Crolat a

ve Ctotal + Ct

where Crotal = L00pF.

ae

GS =}

On wed edad “fore

ion tT ep

Fanout

14 sensor pads

Fig. 1. Equivalent model ofthe capacitive sensor line on 2.8 inch

{ouch panel

121

° \

Fin ng

Volpaave} 2 Vout

[vou

Fig, 2. Block diagram of the new proposed capacitive touch

panel readout circuit with 2-bit ADC

‘The value of Ct (around IpF-2pF) is dependent on the

distance between touch position and sensor tine.

Furthermore, different Ct leads to different Vig. Ifthe

value of Ct can be known, interpolation method can be

applied to calculate the touch position when the

conductive object touches the position between two

sensor lines. The proposed readout circuit with 2-bit

ADC can distinguish the difference between Ct and

further enhances the overall resolution for touch panel

3. New Proposed Readout Circuit for Capacitive

Sensor

In order to reduce the influence of threshold voltage

Variation, @ new readout circuit for capacitive sensor is

proposed. The block diagram [6] of the new proposed

readout circuit is shown in Fig. 2,

In the first stage, the input voltage is amplified by

the transconductance amplifier (Gm amplifier) and

transformed into the current Tint which equals 0 Vr.

Gm, Secondly, the current Lint is converted into voltage

Vo by charging the current integrator. Since Tint is

proportional to Vie, Vo is also proportional to the

integration of current Lint. In addition, with 2-bit ADC,

the proposed circuit can judge the different Vig eaused

by different touch position.

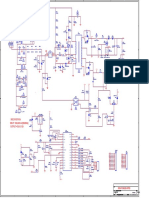

A. Gm Amplifier and Current Integrator

Fig. 3 shows the new proposed capacitive touch

panel readout circuit with its timing chart, The circuit

consists of five pTFT devices, one nTFT device and a

loading capacitance Cout. The transistors MI-MS are

switches and transistor M6 is in the charge of

transconducting voltage into current as a Gm amplifier.

‘The timing chart consists of three periods: (1)

compensation period, (2) reset period, and (3)

amplification period. In the compensation period, M2,

M3, MS, and M6 are turned on. The node Va is charged

by the supply voltage VDDA until M6 is in cut-oft

region. The voltage difference between the source and

gate of M6 equals to the threshold voltage of M6 (Ve).

At meanwhile, the node V¢ is set to the supply voltage

YVDDA. The voltage difference between node Va and Ve is

stored in capacitance C1. In the reset period, M2 and MS

are turned off as well as MI is switched on. Therefore, the

output voltage Vo is discharged to ground by MI and the

node Va maintains the same voltage (VDDA+Vae)). During,

the amplification period, the node Ve is connected to node

Fin, dropping a voltage (AV) which equals to the voltage

difference berween VDDA and Vpn, Because of the charge

conservation at the node Va, the voltage of node Va also

drops AV and becomes equal to (VDDA-Vpr[Via)

‘The basic current formula of TFT device can be

expressed as following equation:

Me uC Veo =| ®

where ois the earier mobility, L denotes te effective

channel length, W isthe effective channel wid, Cui the

gate oxide capacitance per unit area, Vi is the threshold

Volage of TET device. M6 in the amplification pesiod

transeonducts the voltage of node Va into a eurent shown

in equation (2)

w Ver)? 3)

Fi t20 (VODA — Vr ¢

This current is not relevant to the threshold voltage of

‘TFT deviee. Using the compensated current charges the

loading capacitances Cout which can be seen as current

integrator, the impact of threshold voltage variation on the

‘output voltage Vo can be reduced as shown in Fig, 4. When

the fixed Viq and different [Vol values 0.765V, 0.9V and

1,035V are applied, the output voltages Vo for proposed

cireuit with threshold voltage compensation ate almost the

same, Compared to the readout circuit without threshold

voltage compensation, the current lint variation in

amplification period can be reduced from 54.4% t0 10.9%,

vooa

cua WIPO vooa

as

Fini ie

ve

Fig. 3. Schematic of proposed readout circuit with threshold

voltage compensation and timing et for each clock,

122

.

° ao

@

Fig. 4. Simulated reslls of the proposed readout circuit for

capacitive sensor (a) without threshold voltage compensation

and (b) with threshold voltage compensation under different

threshold voltage

Fig. 5, Circuit configuration of A/D converter.

B. Analog-to-Digital Converter

Fig. 5 shows the configuration of A/D converter

suitable for LTPS technology (8), [9]. Switch capacitor

technique is applied to cancel the influence of threshold

voltage variation of TET device. All switches are

controlled by clock signals CLKS or CLK6, The circuit

‘operation has two steps, 1) storing the logic threshold

voltage Vans on capacitor and 2) eliminating Vijop and

comparing Vo with reference voltage. At first, CLK6 is

set to high and the difference between logic threshold

Voltage Vaiss of inverter and Vref is stored on the

capacitor C2, In the comparison period, CLK6 is

switched to low and CLKS is set to high, The input

voltage of inverter becomes (Vo+Viuy-Vref) due to

charge conservation, Two inverter stages as buffer are

added to guarantee full-swing of the output voltage.

Furthermore, this circuit has immunity from

threshold voltage variation since the Via is cancelled

by storing itself on C2. Two bit resolution i

implemented by using two different reference voltages

‘Vrefl and Vref2. The simulation results are shown in

Fig. 6. Depending on the digital bits of Vout, different

touch position between two sensor lines can be judged

and the overall resolution for touch panel can be

enhanced.

a

(b)

©

Fig. 6. Simulation results of the proposed circuit with 2 bit-ADC

‘with (a) panel is non-touched (b) Ct= IpF and (c) Ct= 2pF,

4. Experimental Results

‘The now proposed readout cireuit has been designed and

fabricated in a 3-j0m LTPS technology. The measurement setup is

shown in Fig. 7, where CLK and CLK are given by HP S1I10A

pulse/patent generator, CLK2 to CLKS are assigned by

Keithley4200 dul pulse generator, power supply is GPS 4303 DC

power supply and the output waveforms are observed by.

SDOGOSA oscilloscope. Fig. $ shows the measured results of the

proposed circuit with VDDA = VDDB = 12V, Vrefl = 10.6¥ and

Vrei2 = 9.8V,

‘When CLKG is high, digital output Voutl and Vout2 define

the value of Ct locates in which interval, “00°, “OI” and “11”

stand for 2pF, IpF and non-touched respectively. Different

capacitance value can be distinguished successfully by the

proposed circuit with 2-bit ADC.

123,

He e1s108 PusePaten Generator? P

ox

—

you me

eal

Fig. 7, The fabricated circuits on glass substrate to verify the

readout function of the proposed circuit and its corresponding,

measurement setup,

Fig. 8. Measured results ofthe proposed readout citeuit with -

bit ADC for capacitive sensor with (a) panel is non-touched (b)

(CLs IpF and (c) Ct is 2pF.

Conclusions

‘An analog readout circuit for capacitive sensor on glass

‘substrate for panel application has been successfully designed and

fabricated in a 3-um LTPS technology. By employing switeh

capacitor technique, the influence of threshold voltage variation

successfully. This proposed

architecture ean not only distinguish the panel is touched or no,

but also distinguish different value of touch capacitance and

further know the touch position between sensor line,

can be reduced new iret

Acknowledgments

‘The authors would like 10 thank support of the circuit

fabrication on glass substrate fiom AU Optronies Corporation,

Taiwan,

References

1) T. Nishibe and H. Nakamura, “Value-added integration of

silicon-on-glass (SOG) based on LTPS

technologies.” J. Soe. I Display, vol. 15, no.2, pp. 151-156, Feb,

2007,

2) CoC. Tsai, MoD. Ker, YoFL Li, CoH. Kuo, CoH. Li, Yor

Hsich and CT. Liu, “Design and realization of delt-sigma

analog-to-digital converter in LTPS technology.” S{D Dig. Tech.

2009, pp. 1283-1286.

3) CoH. Li, Mel, Jou and Y.-J. Hsich, “Multitouch panel: tend

and applications,” Proc, IDW, 2009, pp. 2127-2130,

4) MoD. Ker, C-K. Deng, and J-L. Huang, “On-panel output

buffer with offset compensation technique for data driver in LTPS.

technology.” IEEE J. Display Tech., vol. 2, no. 2, pp. 153-159,

dan. 2006.

5) JS. Chen and MD. Ker, "New gate-bias vollage-generating

technique with threshold-voltaze compensation for on-glass analog,

circuits in LTPS process,” IEEE J. Display Tech, ol. 3, 3, pp.

309-314, Sep. 2007.

6) Y-S. Tigo, M-L. Sheu, S.-M. Wu, and HM. Yeon, “A CMOS

readout circuit for LTPS-TFT capacitive fingerprint sensor,” Prac

of IEEE Electron Devices and Solid-State Circuits, Dee. 2005, pp.

631-634.

7) E. Kanda, T. Eguehi, ¥. Hiyoshi, T. Chino, Y. Tsuchiya, T.

Invashita, 7, Ozawa, T. Miyazawa and T.Matsumoto, “Integrated

active matrix capacitive sensors for touch panel LTPS-TFT.

LCDs," SID Dig, Tech., 2008, pp. 834-837,

8) T. Nakamura, H. Hayashi, M. Yoshida, N. Tada, M. Ishikawa,

T. Mota and T, Nishibe, “A touch pane! function integrated LCD.

including LTPS A/D converter,” SID Dig. Tech., 2008, pp. 1054

1055,

9) T. Kumamoto, M, Nakaya, H. Honda, S. Asai, Y. Akasaka and

YY. Horiba, "An S-bit high-speed A/D converter,” IEEE J. Solid-

Siaie Cireuit vol. 21, pp. 976-982, Dee, 1986,

functions for

124

You might also like

- Hollander - HF Oscillation Shunt Vs PearsonDocument19 pagesHollander - HF Oscillation Shunt Vs PearsonGiancarloRichardRivadeneyraMirandaNo ratings yet

- 09 Optimal ZVS Modulation EvertsDocument18 pages09 Optimal ZVS Modulation EvertsGiancarloRichardRivadeneyraMirandaNo ratings yet

- Hoja de Cálculo en Boletin de Servicio MAgic Control Compatible 2013 Al 2017Document1 pageHoja de Cálculo en Boletin de Servicio MAgic Control Compatible 2013 Al 2017GiancarloRichardRivadeneyraMirandaNo ratings yet

- Corriente KalleyDocument13 pagesCorriente KalleyGiancarloRichardRivadeneyraMirandaNo ratings yet

- Guía UART de PS4 - Wiki de ReparaciónDocument9 pagesGuía UART de PS4 - Wiki de ReparaciónGiancarloRichardRivadeneyraMiranda0% (1)

- Abreviaturas en TconDocument6 pagesAbreviaturas en TconGiancarloRichardRivadeneyraMiranda100% (3)

- Lector de Bus de Datos IÂ CDocument4 pagesLector de Bus de Datos IÂ CGiancarloRichardRivadeneyraMiranda100% (1)

- PFC 0812Document75 pagesPFC 0812GiancarloRichardRivadeneyraMirandaNo ratings yet

- Infineon-MOSFET CoolMOS P7 Optimizing Power Supplies For EMI Requirements-ApplicationNotes-V01 00-EnDocument25 pagesInfineon-MOSFET CoolMOS P7 Optimizing Power Supplies For EMI Requirements-ApplicationNotes-V01 00-EnGiancarloRichardRivadeneyraMirandaNo ratings yet

- 5800-P24QB-WP20-C (Electric Diagram) 2012.9.13Document1 page5800-P24QB-WP20-C (Electric Diagram) 2012.9.13GiancarloRichardRivadeneyraMirandaNo ratings yet

- United States Patent: (10) Patent No.: (45) Date of PatentDocument23 pagesUnited States Patent: (10) Patent No.: (45) Date of PatentGiancarloRichardRivadeneyraMirandaNo ratings yet

- SN75LVDS88PFD Texas InstrumentsDocument12 pagesSN75LVDS88PFD Texas InstrumentsGiancarloRichardRivadeneyraMirandaNo ratings yet

- THAN0060 Rev.1.50 EDocument12 pagesTHAN0060 Rev.1.50 EGiancarloRichardRivadeneyraMirandaNo ratings yet

- Rossi Asynchronous Three Phase Brake Motors Catalogue en 09-2009Document160 pagesRossi Asynchronous Three Phase Brake Motors Catalogue en 09-2009GiancarloRichardRivadeneyraMirandaNo ratings yet

- HX8218-A 960CH TFT LCD Source Driver With Built-In TCON: Preliminary Version 01 January 2005Document48 pagesHX8218-A 960CH TFT LCD Source Driver With Built-In TCON: Preliminary Version 01 January 2005GiancarloRichardRivadeneyraMirandaNo ratings yet

- Resistencias de Derivación Resistencias de Derivación de Detección de Corriente - Ele-BásicosDocument4 pagesResistencias de Derivación Resistencias de Derivación de Detección de Corriente - Ele-BásicosGiancarloRichardRivadeneyraMirandaNo ratings yet

- 1200/1152/1080/960-Output TFT LCD Gate Driver: Fitipower Integrated Technology IncDocument26 pages1200/1152/1080/960-Output TFT LCD Gate Driver: Fitipower Integrated Technology IncGiancarloRichardRivadeneyraMirandaNo ratings yet

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5807)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (346)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)