Professional Documents

Culture Documents

Computer Architecture 4 Exam/Comp/It/Csc/3621/May'17 Duration: 3Hrs M. Marks: 75 Section-A Q1 Do As Directed: 1.5X10 15

Uploaded by

bahinkiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Computer Architecture 4 Exam/Comp/It/Csc/3621/May'17 Duration: 3Hrs M. Marks: 75 Section-A Q1 Do As Directed: 1.5X10 15

Uploaded by

bahinkiCopyright:

Available Formats

S.B. Roll No...............................................

COMPUTER ARCHITECTURE

th

4 Exam/COMP/IT/CSc/3621/MAY’17

Duration: 3Hrs M. Marks: 75

SECTION- A

Q1 Do as directed: 1.5x10=15

a. (AF)16 =( )8.

b. 256 in binary is written as _______

c. 2’s complement of 0000 is_______.

d. ________ memory exists between CPU and dynamic RAM.

e. A Stack _____________bit register.

f. _________ register points to next instruction address.

g. CISC stands for _________.

h. During DMA transfer the _______ is idle.

i. 15 is written as (1111) in BCD format. (T/F)

j. BCD is a weighted code.(T/F).

SECTION- B

Q2 Attempt any FIVE questions. 6x5=30

i. Explain general register organization with suitable diagram?

ii. Write a short note on Stack organization.

iii.

iv.

v.

What do you mean by addressing mode? Explain any five.

What is an interrupt? Explain Daisy Chain priority interrupt.

o m

Explain the various instruction formats used in CPU with suitable examples?

.r c

vi. Write in brief about Cache memory.

vii. Give a short note on Memory connection to CPU.

m

viii. Write a short note on memory hierarchy?

ix.

e

What do you mean by FIFO buffer? Explain with the help of neat and clean diagram.

p o

.r c

SECTION- C

Q3 Attempt any three questions.

I.

p a 10x3=30

What is a DMA Controller? Describe along with its working using suitable diagrams.

II.

III.

IV.

r

Explain booth multiplication algorithm with an example?

b

What do you mean by pipelining? Explain with the help of example.

Describe the concept of virtual memory using paging and segmentation?

p e

V. Write a short note on :

a

rp

a) Input-Output Interface

b) Associative Memory

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- TS500Document10 pagesTS500Oğuzcan ŞahinNo ratings yet

- Parallel Port InterfacingDocument34 pagesParallel Port InterfacingKingsprincessNo ratings yet

- GarageBand TutorialDocument8 pagesGarageBand TutorialMilan RadisicNo ratings yet

- From The President's Desk: in This IssueDocument6 pagesFrom The President's Desk: in This IssueJayant ShaligramNo ratings yet

- Hgu56 ManualDocument86 pagesHgu56 ManualRedgy Geryl0% (1)

- Education Course Catalog enDocument8 pagesEducation Course Catalog enlipasot781No ratings yet

- Robotic Surgery: A Seminar Report OnDocument16 pagesRobotic Surgery: A Seminar Report OnWendy CannonNo ratings yet

- Social Computing in The EnterpriseDocument17 pagesSocial Computing in The EnterpriseJustin Souter100% (2)

- Q Cells Data Sheet Q.peak Duo-G8 345-360 Global 2019-05 Rev02 enDocument2 pagesQ Cells Data Sheet Q.peak Duo-G8 345-360 Global 2019-05 Rev02 envijayNo ratings yet

- PD Smart PDFDocument2 pagesPD Smart PDFAriel Leandro Toro MuñozNo ratings yet

- 21.1 Mb-4w8x33vb1-01-I3Document2 pages21.1 Mb-4w8x33vb1-01-I3YarinaNo ratings yet

- PW200-7H PW220-7H: Vebm370100Document890 pagesPW200-7H PW220-7H: Vebm370100خشایار عبدالهیNo ratings yet

- Paquete de Información de Producto: Motor 25 HP 1760 RPM Nema 284TDocument11 pagesPaquete de Información de Producto: Motor 25 HP 1760 RPM Nema 284TCarolina AlexandraNo ratings yet

- Samsung 12k84 Washing Machine - User ManualDocument68 pagesSamsung 12k84 Washing Machine - User ManualFidelis NdanoNo ratings yet

- Checklist AsetDocument8 pagesChecklist AsetcheanhoiNo ratings yet

- TractorsDocument12 pagesTractorsBekalu DanielNo ratings yet

- Expert Office 365 Notes From The FieldDocument289 pagesExpert Office 365 Notes From The FieldYohanna Monsalvez100% (1)

- CV-Agus Nugraha (11.01.2021)Document11 pagesCV-Agus Nugraha (11.01.2021)Agus NugrahaNo ratings yet

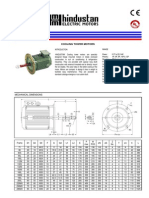

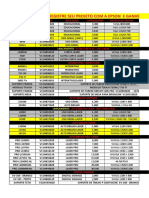

- Cooling Tower MotorDocument2 pagesCooling Tower MotorDipendraTomarNo ratings yet

- Garage Door Control W/keyfob DSC-007: Application NoteDocument2 pagesGarage Door Control W/keyfob DSC-007: Application Noteoreste2008No ratings yet

- Simple Mail Transfer ProtocolDocument29 pagesSimple Mail Transfer ProtocolRahim AbbaNo ratings yet

- Module 5Document80 pagesModule 5Big Brown BeastNo ratings yet

- Chapter 1Document6 pagesChapter 1Bhuvaneswari TSNo ratings yet

- CNC Programming & Application: Federal TVET Institute Manufacturing Technology Department Addis Abeba EthiopiaDocument58 pagesCNC Programming & Application: Federal TVET Institute Manufacturing Technology Department Addis Abeba EthiopiaGezae MebrahtuNo ratings yet

- Soc Fpga Main Memory Performance: Architecture BriefDocument4 pagesSoc Fpga Main Memory Performance: Architecture BriefGiderosNo ratings yet

- Registre Seu Projeto Com A Epson E Ganhe Desconto: Modelo Aplicaçao Luminsidade Resoluçao NativaDocument20 pagesRegistre Seu Projeto Com A Epson E Ganhe Desconto: Modelo Aplicaçao Luminsidade Resoluçao NativaJairo RodriguesNo ratings yet

- CTSA Technical Proposal Template 10-001Document9 pagesCTSA Technical Proposal Template 10-001yasirtanvirNo ratings yet

- Advanced Product Quality Planning (APQP)Document15 pagesAdvanced Product Quality Planning (APQP)José AlcocerNo ratings yet

- 2022 GKS-U University Track 2nd Round Result Successful CandidatesDocument8 pages2022 GKS-U University Track 2nd Round Result Successful Candidatesmatiasbenitez1992No ratings yet

- 11 Maintenance Strategy PDFDocument3 pages11 Maintenance Strategy PDFSaravanan RasayaNo ratings yet