Professional Documents

Culture Documents

12.2.4 Clock Control Sequence Summary: Figure 12-4 Shows The Typical Flow For Entering and Exiting A Low-Power State

Uploaded by

dhaNUSHOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

12.2.4 Clock Control Sequence Summary: Figure 12-4 Shows The Typical Flow For Entering and Exiting A Low-Power State

Uploaded by

dhaNUSHCopyright:

Available Formats

Low-power Interface

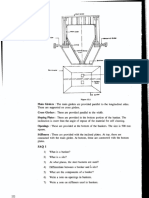

12.2.4 Clock control sequence summary

Figure 12-4 shows the typical flow for entering and exiting a low-power state.

Normal

clocked

operation

System clock controller Low -pow er

drives CSYSREQ low to unclocked

request low -pow er entry operation

Peripheral or system

Peripheral denies or

clock controller initiates

accepts request

low -pow er exit

System clock

Deny A ccept Peripheral controller

System clock controller

Peripheral keeps Peripheral perf orms Peripheral drives

immediately enables

CACTIV E HIGH pow er-dow n CACTIV E HIGH

clocks

Peripheral drives System clock controller

Peripheral drives System clock controller

CSYSACK LOW to immediately enables

CACTIV E LOW drives CSYSREQ HIGH

acknow ledge request clocks

Peripheral drives

System clock controller System clock controller Peripheral drives

CSYSACK LOW to

samples CACTIV E drives CSYSREQ HIGH CACTIV E HIGH

acknow ledge request

Peripheral drives Peripheral drives

System clock controller System clock controller

CSYSACK HIGH to CSYSACK HIGH to

drives CSYSREQ HIGH samples CACTIV E

complete handshake complete handshake

Peripheral drives

System clock controller

CSYSACK HIGH to

disables clocks

complete handshake

Figure 12-4 Low-power clock control sequence

12-6 Copyright © 2003, 2004 ARM Limited. All rights reserved. ARM IHI 0022B

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Chapter 3.c (Centroid by Intergration)Document15 pagesChapter 3.c (Centroid by Intergration)Ariff AziziNo ratings yet

- Native Data Sheet Asme b73.1Document4 pagesNative Data Sheet Asme b73.1Akhmad Faruq Alhikami100% (1)

- Combined Shear and TensionDocument16 pagesCombined Shear and TensionDAN MARK OPONDANo ratings yet

- Lec 4 - 4th WeekDocument40 pagesLec 4 - 4th Weekrajpoot aliNo ratings yet

- Esteem 1999 2000 1.3L 1.6LDocument45 pagesEsteem 1999 2000 1.3L 1.6LArnold Hernández CarvajalNo ratings yet

- Proefschrift T. Steenstra - tcm24-268767Document181 pagesProefschrift T. Steenstra - tcm24-268767SLAMET PAMBUDINo ratings yet

- Lesson Plan in Science 9: I. ObjectivesDocument8 pagesLesson Plan in Science 9: I. ObjectivesmarichuNo ratings yet

- Main Girders: CrossDocument3 pagesMain Girders: Crossmn4webNo ratings yet

- Industrial Artificial Intelligence For Industry 4.0-Based Manufacturing SystemsDocument5 pagesIndustrial Artificial Intelligence For Industry 4.0-Based Manufacturing SystemsMuhammad HaziqNo ratings yet

- PIX4D Simply PowerfulDocument43 pagesPIX4D Simply PowerfulJUAN BAQUERONo ratings yet

- Impact of Retrofitting Existing Combined Heat and Power Plant With Polygeneration of Biomethane PDFDocument16 pagesImpact of Retrofitting Existing Combined Heat and Power Plant With Polygeneration of Biomethane PDFAwais Salman0% (1)

- Fulltext 4 PDFDocument4 pagesFulltext 4 PDFSubhadip Banerjee0% (1)

- Bhil Tribal Mobilisation in AlirajpurDocument14 pagesBhil Tribal Mobilisation in Alirajpurrahul banerjeeNo ratings yet

- MTH100Document3 pagesMTH100Syed Abdul Mussaver ShahNo ratings yet

- Effects of Climate ChangeDocument3 pagesEffects of Climate Changejiofjij100% (1)

- Tuberculosis PowerpointDocument69 pagesTuberculosis PowerpointCeline Villo100% (1)

- Syllabus Unit Iv Unit Commitment and Economic DispatchDocument23 pagesSyllabus Unit Iv Unit Commitment and Economic DispatchBALAKRISHNANNo ratings yet

- 123 09-Printable Menu VORDocument2 pages123 09-Printable Menu VORArmstrong TowerNo ratings yet

- Standard Cost EstimateDocument21 pagesStandard Cost EstimateMOORTHYNo ratings yet

- Lecture 12Document8 pagesLecture 12Mechanical ZombieNo ratings yet

- Biomedical Engineering Handbook Revised 5 2015Document37 pagesBiomedical Engineering Handbook Revised 5 2015Teja GuttiNo ratings yet

- Curing Obesity, WorldwideDocument6 pagesCuring Obesity, WorldwideHernán SanabriaNo ratings yet

- DOC-20161226-WA0009 DiagramaDocument61 pagesDOC-20161226-WA0009 DiagramaPedroNo ratings yet

- Worlds Apart: A Story of Three Possible Warmer WorldsDocument1 pageWorlds Apart: A Story of Three Possible Warmer WorldsJuan Jose SossaNo ratings yet

- Top Ten Myths About The BrainDocument5 pagesTop Ten Myths About The BrainfayazalamaligNo ratings yet

- Cross Talk Details and RoutingDocument29 pagesCross Talk Details and RoutingRohith RajNo ratings yet

- Presentation - Delight Bulb PDFDocument22 pagesPresentation - Delight Bulb PDFShiva KishoreNo ratings yet

- Arduino Oscilloscope ProjectDocument12 pagesArduino Oscilloscope ProjectSathya Narayan100% (1)

- TM-8000 HD Manual PDFDocument37 pagesTM-8000 HD Manual PDFRoxana BirtumNo ratings yet

- Dual Op Amp and Voltage Reference Ap4310/ADocument12 pagesDual Op Amp and Voltage Reference Ap4310/AМихаил ЯненкоNo ratings yet