Professional Documents

Culture Documents

W83312SN

W83312SN

Uploaded by

Job GarciaCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

W83312SN

W83312SN

Uploaded by

Job GarciaCopyright:

Available Formats

Nuvoton

Bus Termination Regulator

W83312SN

W83312SN

-Table of Content-

1. GENERAL DESCRIPTION .............................................................................................................. 1

2. FEATURES ...................................................................................................................................... 1

3. BLOCK DIAGRAM ........................................................................................................................... 2

4. PIN CONFIGURATION AND TYPICAL APPLICATION CIRCUIT .................................................. 2

5. PIN DESCRIPTION .......................................................................................................................... 3

6. FUNCTIONAL DESCRIPTION ........................................................................................................ 4

7. ELECTRICAL CHARACTERISTIC .................................................................................................. 7

8. TYPICAL OPERATING WAVEFORMS ........................................................................................... 9

9. PACKAGE DIMENSION ................................................................................................................ 22

10. ORDERING INFORMATION.......................................................................................................... 23

11. TOP MARKING SPECIFICATION ................................................................................................. 23

12. REVISION HISTORY ..................................................................................................................... 24

Publication Date: Mar., 2010

-I- Revision A5

W83312SN

1. GENERAL DESCRIPTION

The W83312SN is a linear regulator which provides a power achieves peak 3.0Amp bi-

directional sinking and sourcing capability for a high speed bus terminator application. The

chip simply implements a stable power supply which tracks half of input power

dynamically for bus terminator with a single chip. The W83312SN is promoted with small

footprint 8-SOP 150mil power package. With W83312SN design, a high integration, high

performance, and cost-effective solution are promoted.

2. FEATURES

2.1. General

z Memory Termination Regulator for DDR1, DDR2, DDR3 and Low Power DDR3

z Sink and Source 3A Peak Current

z Integrated Power MOSFET

z Adjustable V OUT by External Resistors

z Low External Component Count

z Low Output Voltage Offset

z Current Limit Protection

z Over Temperature Protection

z -40°C to 85°C Ambient Operating Temperature Range

2.2. Package

z SOP-8 150mil with Exposed Pad Package

z Lead Free (ROHS Compliant) and Halogen Free

2.3. Applications

z Desktop PCs, Notebooks, and Workstations

z Graphics Card Memory Termination

z Set Top Boxes, Digital TVs and Printers

z Active Termination Buses

z DDR1, DDR2 and DDR3 Memory Systems

Publication Date: Mar., 2010

-1- Revision A5

W83312SN

3. BLOCK DIAGRAM

VCNTL VIN

Current Limit

Protection

Control

VREF VOUT

Logic

GND

Thermal

Shutdown

4. PIN CONFIGURATION AND TYPICAL APPLICATION CIRCUIT

VIN 1 8 NC

GND 2 7 NC

VREF 3 6 VCNTL

VOUT 4 5 NC

W83312SN

(Top View)

Publication Date: Mar., 2010

-2- Revision A5

W83312SN

VDDQ=2.5V/1.8V/1.5V VCNTL=3.3V/5V

C CNTL

R1 C IN VIN VCNTL

VREF VTT = VDDQ x R2 / (R1+R2)

Enable R2 C SS

VOUT

GND C OUT

Typical Application Circuits

5. PIN DESCRIPTION

SYMBOL PIN I/O FUNCTION

Main power input pin which supplies current to output pin.

For lower power dissipation consideration, using VDDQ

VIN 1 I

(Supply voltage for DRAM) as power source is

recommended.

Internal reference voltage source. Generally, VREF tracks

VDDQ/2 for DDR application.

Using voltage dividing resistors and capacitor as low pass

filter for noise immunity and output voltage soft start is

VREF 3 I

recommended.

If using an N-MOSFET as shutdown function, please make

sure the sinking current capability can pull down VREF under

0.2V.

VOUT 4 O Voltage output pin which is regulated to track VREF voltage.

Power for internal control logic circuitry. A ceramic

VCNTL 6 I

decoupling capacitor with 1uF is required.

GND 2 Ground. Connect to negative terminal of the output capacitor.

NC 5, 7, 8 No connection.

Publication Date: Mar., 2010

-3- Revision A5

W83312SN

6. FUNCTIONAL DESCRIPTION

6.1 VTT Sink/Source Regulator

The W83312SN is a sink/source tracking Double Data Rate (DDR) termination regulator

specifically designed for low input voltage, low cost and low external component count

systems where space is a key application parameter. The W83312SN integrates a high

performance, low dropout linear regulator that is capable of both sinking and sourcing current.

6.2 General Regulator

The W83312SN could also serves as a general linear regulator. The W83312SN accepts an

external reference voltage at VREF pin and provides output voltage regulated to this reference

voltage as shown in Fig.6-1, where

VOUT=VEXT x R2/ (R1+R2)

VIN

VEXT VCNTL=3.3V/5V

C CNTL

R1 C IN VIN VCNTL

VREF VOUT = VEXT x R2 / (R1+R2)

R2 C SS

VOUT

GND C OUT

Fig. 6-1

The W83312SN supports wide VREF voltage input range, making it versatile and idea for

many types of low power LDO applications. The dropout voltage is the input voltage minus

output voltage that produces 2% decrease in output voltage, where

VIN MIN =V DROPOUT + VOUT

The output voltage range depends on VCNTL voltage and output loading which means higher

VCNTL voltage can support higher output voltage and higher output loading.

Fig.6-2 and Table 6-1 show that the relationships among VOUT, V DROPOUT and IOUT when

VCNTL=5V. For example, if VOUT=3.4V, the maximum output loading is 1.5A with 0.25V

dropout voltage and the minimum VIN is 3.65V. The Max column in the table means the

minimum dropout voltage needed in worst conditions. Choose suitable VIN voltage to obtain

better efficiency.

VCNTL=5V

Parameter Conditions Typ. Max Unit

IOUT=1A, 0.6V≦ VOUT ≦3.4V 0.15 0.3

IOUT=1.5A, 0.6V≦ VOUT ≦3.4V 0.25 0.5

Dropout

V

Voltage

IOUT=2A, 0.6V≦ VOUT ≦3.2V 0.35 0.7

IOUT=2.5A, 0,8V≦ VOUT ≦3V 0.5 1

Publication Date: Mar., 2010

-4- Revision A5

W83312SN

VOUT vs. Dropout Voltage, VCNTL=5V

0.6

0.5

IOUT=1A IOUT=1.5A

Dropout Voltage (V)

0.4 IOUT=2A IOUT=2.5A

0.3

0.2

0.1

0

0.6 0.8 1 1.2 1.4 1.6 1.8 2 2.2 2.4 2.6 2.8 3 3.2 3.4

VOUT (V)

Table 6-1

Fig.show

Fig.6-3 and Table 6-2 6-2 that the relationships among VOUT, V DROPOUT and IOUT when

VCNTL=3.3V.

VOUT vs. Dropout Voltage, VCNTL=3.3V

0.6

VCNTL=3.3V

IOUT=1A IOUT=1.5A

0.5

IOUT=2A IOUT=2.5A Parameter Conditions Typ. Max Unit

Dropout Voltage (V)

0.4

IOUT=1A, 0.6V≦ VOUT ≦1.8V 0.35 0.7

0.3

IOUT=1.5A, 0.6V≦ VOUT ≦1.6V 0.35 0.7

0.2 Dropout

V

Voltage

IOUT=2A, 0.6V≦ VOUT≦ 1.6V 0.6 1.2

0.1

IOUT=2.5A, 0.8V≦ VOUT≦ 1.4V 0.45 0.9

0

0.6 0.8 1 1.2 1.4 1.6 1.8

VOUT (V) Table 6-2

Fig. 6-3

6.3 Shutdown Function

When the external reference voltage at VREF pin is under shutdown threshold, the internal

regulator will be turned off and VOUT is at High-Z state.

6.4 Over Current Protection

The W83312SN provides a current limit circuitry, which monitors the output current and

controls NMOS’s gate voltage to limit the output current at 3.5A, typically.

6.5 Over Temperature Protection

The W83312SN monitors its junction temperature. If the device junction temperature exceeds

its threshold value, typically 165°C, the VOUT is shut off. The shutdown is a non-latch

protection.

6.6 Thermal Design

Since the W83312SN is a linear regulator, the VOUT current flows in both source and sink

directions, thereby dissipating power from the device. When the device is sourcing current, the

Publication Date: Mar., 2010

-5- Revision A5

W83312SN

voltage difference between VIN and VOUT times I OUT current becomes the power dissipation

as shown in below equation.

P DISS_SOURCE = (VIN-VOUT) x I OUT_SOURCE

In this case, if VIN is connected to an alternative power supply lower than the VDDQ voltage,

overall power loss can be reduced. For the sink phase, VOUT voltage is applied across the

internal LDO regulator and the power dissipation, P DISS_SINK can be calculated by below

equation.

P DISS_SINK = VOUT x I OUT_SINK

Because the device does not sink and source current at the same time and the I OUT current

may vary rapidly with time, the actual power dissipation should be the time average of the

above dissipations over the thermal relaxation duration of the system. Another source of

power consumption is the current used for the internal current control circuitry form VCNTL

supply and the VIN supply. This can be estimate as 10mW or less during normal operating

conditions. The power must be effectively dissipated from the package.

Maximum power dissipation allowed by the package is calculated by below equation.

P PKG = [ T J(MAX) – T A(MAX) ] / θ JA

, where

z T J(MAX) is +125°C

z T A(MAX) is the maximum ambient temperature in the system

z θ JA is the thermal resistance form junction to ambient

6.7 Input Capacitor

Depending on the trace impedance between the VIN bulk power supply to the device, a

transient increase of source current is supplied mostly by the charge from the VIN input

capacitor. Use a 100uF (or greater) capacitor to supply this transient charge. Provide more

input capacitance as more output capacitance is used at VOUT.

6.8 Output Capacitor

For stable operation, the total capacitance of the VOUT terminal must be greater than 100uF.

Attach two or more capacitors in parallel to minimize the effect of equivalent series resistance

(ESR) and equivalent series inductance (ESL).

6.9 Layout Consideration

Consider the following points before starting the W83312SN layout design. Fig. 6-4 shows the

suggestion of minimum land pattern. Fig. 6-5 shows the recommended PCB layout. Using

“dog bone” copper patterns on the top layer can increase efficiency of heat dissipating.

z The input bypass capacitor for VIN should be placed as close as possible to the pin with

short and wide connections.

z The output capacitor for VOUT should be placed close to the pin with short and wide

connection in order to avoid ESR and/or ESL trace inductance.

z In order to effectively remove heat from the package, properly prepare the thermal land.

Apply solder directly to the package’s thermal pad. The wide traces of component and the

side copper connected to the thermal land pad help to dissipate heat. The thermal land

connected to the ground plane could also be used to help dissipation.

Publication Date: Mar., 2010

-6- Revision A5

W83312SN

75

VCNTL

Ground

C CNTL

For heat

130 dissipatin

219 95

Ground

Unit: mil

(Not to scale)

C IN C OUT

VIN VOUT

50 24

Fig. 6-4 Fig. 6-5

7. ELECTRICAL CHARACTERISTIC

7.1 Absolute Maximum Ratings (Note1)

ITEM SYMBOL RATING UNIT

Input Voltage VIN -0.3 to 7 V

Control Logic Input Voltage VCNTL -0.3 to 7 V

Reference Voltage VREF -0.3 to 5 V

Human Body Mode ±2 kV

(Note2)

Electrostatic discharge protection Machine Mode ±200 V

Latch-Up ±100 mA

Storage Temperature Range -65 to 150 °C

7.2 Thermal Information

ITEM RATING UNIT

Power Dissipation, P D @ T A =25°C Internal Limited W

Package Thermal Resistance, ESOP8, θ JA 75 °C/W

7.3 Recommended Operating Conditions

ITEM SYMBOL MIN MAX UNIT

VIN 1.2 5.5

V

Input Voltage VCNTL 3 5.5

VREF 0.6 3.3 V

Sourcing 0 2.5

Continuous Output Current A

Sinking 0 2.5

Sourcing 0 3.0

Peak Output Current A

Sinking 0 3.0

Publication Date: Mar., 2010

-7- Revision A5

W83312SN

Operating Temperature Range -40 85 °C

(Note3)

Junction Temperature Range -40 125 °C

7.4 Electrical Characteristics

Typicals and limits appearing in normal type apply for Tj = 25°C. Limits appearing in Boldface type apply

over the entire junction temperature range for operation, -40 ° C to 85 ° C (Note4). VCNTL= 3.3V/5V,

VIN=2.5V/1.8V/1.5V, VREF=1.25V/0.9V/0.75V, C OUT =100uF, all voltage outputs unloaded (unless

otherwise noted).

PARAMETER SYMBOL TEST CONDITION MIN TYP MAX UNITS

Input

I OUT =0A, VCNTL=3.3V 0.5 0.7

VCNTL Operating Current I CNTL mA

I OUT =0A, VCNTL=5V 0.7 1

I OUT =0A, VCNTL=3.3V 0.3 0.5

VIN Operating Current I VIN mA

I OUT =0A, VCNTL=5V 0.3 0.5

VCNTL Quiescent Current in VREF < 0.2V, VCNTL=3.3V 60 90

I SD_CNTL uA

Shutdown Mode VREF < 0.2V, VCNTL=5V 60 90

VIN Quiescent Current in

I SD_VIN VREF < 0.2V -1 0 1 uA

Shutdown Mode

I IH VREF=3.3V -1 0 1

VREF Leakage Current uA

I IL VREF=0V -1 0 1

Output (DDR1 / DDR2 / DDR3)

Output Offset Voltage (VREF-

V OS I OUT =0A -5 5 mV

VOUT)

I OUT =0 → +2.5A (Note5) -20 20

Load Regulation (VREF-VOUT) ∆V L mV

I OUT =0 → -2.5A (Note5) -20 20

Protection

Current Limit I LIM In any VIN ±3 ±3.5 ±4.5 A

(Note6)

Thermal Shutdown Temperature T SD 3.3V < VCNTL < 5V 150 165 175 °C

Thermal Shutdown Hysteresis ∆T SD 3.3V < VCNTL < 5V 30 °C

VREF Shutdown Mode

V IH Enable 0.6

Shutdown Threshold V

V IL Disable 0.2

Note1. Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the

device. These are stress ratings only and functional operation of the device at these or any other

conditions beyond those indicated under recommended operating conditions is not implied. Exposure to

absolute maximum rated conditions for extended periods may affect device reliability.

Note2. Devices are ESD sensitive. Handling precaution recommended.

Note3. At elevated temperatures, devices must be de-rated based on thermal resistance. The device in the

ESOP-8 package must be de-rated at θ JA =75˚C/W junction to ambient with minimum PCB footprint.

Publication Date: Mar., 2010

-8- Revision A5

W83312SN

Note4. Limits are 100% production tested at 25˚C. Limits over operating temperature range are guaranteed

through correlation using Statistical Quality Control (SQC) methods. The limits are used to calculate

average outgoing quality level.

Note5. VOUT load regulation is tested by using a 10ms period and 50% duty cycle current pulse.

Note6. The maximum allowable power dissipation is a function of the maximum junction temperature, T J(MAX) ,

the junction to ambient thermal resistance, θ JA , and the ambient temperature, T A . exceeding the

maximum allowable power dissipation will cause excessive die temperature and the regulator will go into

thermal shutdown. Ensured by design, no production tested.

8. TYPICAL OPERATING WAVEFORMS

VIN=2.5V, VCNTL=3.3V, VOUT=1.25V @ 3A Sourcing VIN=2.5V, VCNTL=3.3V, VOUT=1.25V @ 2.5A Sourcing

VIN=2.5V, VCNTL=5V, VOUT=1.25V @ 3A Sourcing VIN=2.5V, VCNTL=5V, VOUT=1.25V @ 2.5A Sourcing

Publication Date: Mar., 2010

-9- Revision A5

W83312SN

VIN=1.8V, VCNTL=3.3V, VOUT=0.9V @ 3A Sourcing VIN=1.8V, VCNTL=3.3V, VOUT=0.9V @ 2.5A Sourcing

VIN=1.8V, VCNTL=5V, VOUT=0.9V @ 3A Sourcing VIN=1.8V, VCNTL=5V, VOUT=0.9V @ 2.5A Sourcing

VIN=1.5V, VCNTL=3.3V, VOUT=0.75V @ 3A Sourcing VIN=1.5V, VCNTL=3.3V, VOUT=0.75V @ 2.5A Sourcing

Publication Date: Mar., 2010

-10- Revision A5

W83312SN

VIN=1.5V, VCNTL=5V, VOUT=0.75V @ 3A Sourcing VIN=1.5V, VCNTL=5V, VOUT=0.75V @ 2.5A Sourcing

VIN=1.2V, VCNTL=3.3V, VOUT=0.6V @ 3A Sourcing VIN=1.2V, VCNTL=3.3V, VOUT=0.6V @ 2.5A Sourcing

Publication Date: Mar., 2010

-11- Revision A5

W83312SN

VIN=1.2V, VCNTL=5V, VOUT=0.6V @ 3A Sourcing VIN=1.2V, VCNTL=5V, VOUT=0.6V @ 2.5A Sourcing

VIN=2.5V, VCNTL=3.3V, VOUT=1.25V @ 3A Sinking VIN=2.5V, VCNTL=3.3V, VOUT=1.25V @ 2.5A Sinking

VIN=2.5V, VCNTL=5V, VOUT=1.25V @ 3A Sinking VIN=2.5V, VCNTL=5V, VOUT=1.25V @ 2.5A Sinking

Publication Date: Mar., 2010

-12- Revision A5

W83312SN

VIN=1.8V, VCNT3O.9V @ 3A Sinking VIN=1.8V, VCNTL=3.3V, VOUT=0.9V @ 2.5A Sinking

VIN=1.8V, VCNTL=5V, VOUT=0.9V @ 3A Sinking VIN=1.8V, VCNTL=5V, VOUT=0.9V @ 2.5A Sinking

VIN=1.5V, VCNTL=3.3V, VOUT=0.75V @ 3A Sinking VIN=1.5V, VCNTL=3.3V, VOUT=0.75V @ 2.5A Sinking

Publication Date: Mar., 2010

-13- Revision A5

W83312SN

VIN=1.5V, VCNTL=5V, VOUT=0.75V @ 3A Sinking VIN=1.5V, VCNTL=5V, VOUT=0.75V @ 2.5A Sinking

VIN=1.2V, VCNTL=3.3V, VOUT=0.6V @ 3A Sinking VIN=1.2V, VCNTL=3.3V, VOUT=0.6V @ 2.5A Sinking

VIN=1.2V, VCNTL=5V, VOUT=0.6V @ 3A Sinking VIN=1.2V, VCNTL=5V, VOUT=0.6V @ 2.5A Sinking

Publication Date: Mar., 2010

-14- Revision A5

W83312SN

VIN=2.5V, VCNTL=3.3V, VOUT=1.25V, VOUT short to GND VIN=2.5V, VCNTL=5V, VOUT=1.25V, VOUT short to GND

VIN=2.5V, VCNTL=3.3V, VOUT=1.25V, VOUT short to VIN VIN=2.5V, VCNTL=5V, VOUT=1.25V, VOUT short to VIN

Publication Date: Mar., 2010

-15- Revision A5

W83312SN

VIN=1.8V, VCNTL=3.3V, VOUT=0.9V, VOUT short to GND VIN=1.8V, VCNTL=5V, VOUT=0.9V, VOUT short to GND

VIN=1.8V, VCNTL=3.3V, VOUT=0.9V, VOUT short to VIN VIN=1.8V, VCNTL=5V, VOUT=0.9V, VOUT short to VIN

VIN=1.5V, VCNTL=3.3V, VOUT=0.75V, VOUT short to GND VIN=1.5V, VCNTL=5V, VOUT=0.75V, VOUT short to GND

Publication Date: Mar., 2010

-16- Revision A5

W83312SN

VIN=1.5V, VCNTL=3.3V, VOUT=0.75V, VOUT short to VIN VIN=1.5V, VCNTL=5V, VOUT=0.75V, VOUT short to VIN

VIN=1.2V, VCNTL=3.3V, VOUT=0.6V, VOUT short to GND VIN=1.2V, VCNTL=5V, VOUT=0.6V, VOUT short to GND

VIN=1.2V, VCNTL=3.3V, VOUT=0.6V, VOUT short to VIN VIN=1.2V, VCNTL=5V, VOUT=0.6V, VOUT short to VIN

Publication Date: Mar., 2010

-17- Revision A5

W83312SN

VCNTL Current vs. Temperature VCNTL Current vs. Temperature

590 590

570 570

550

VCNTL Current (uA)

550

VCNTL Current (uA)

530 530

510 510

490 490

470 470

450 450

DDR1 @ VCNTL=3.3V

430 DDR2 @ VCNTL=3.3V

DDR1 @ VCNTL=5V 430 DDR2 @ VCNTL=5V

410

410

-40 -20 0 20 40 60 80 100 120

-40 -20 0 20 40 60 80 100 120

Temperature (°C)

Temperature (°C)

VCNTL Current vs. Temperature VCNTL Current vs. Temperature

590 590

570 570

550

VCNTL Current (uA)

550

VCNTL Current (uA)

530 530

510 510

490 490

470 470

450 450

DDR3 @ VCNTL=3.3V

430 LP DDR @ VCNTL=3.3V

DDR3 @ VCNTL=5V 430 LP DDR @ VCNTL=5V

410

410

-40 -20 0 20 40 60 80 100 120

-40 -20 0 20 40 60 80 100 120

Temperature (°C) Temperature (°C)

Publication Date: Mar., 2010

-18- Revision A5

W83312SN

VIN Current vs. Temperature VIN Current vs. Temperature

320 220

300 DDR1 @ VCNTL=3.3V 210 DDR2 @ VCNTL=3.3V

DDR2 @ VCNTL=5V

DDR1 @ VCNTL=5V

280 200

VIN Current (uA)

VIN Current (uA)

260 190

240 180

220 170

200 160

180

150

-40 -20 0 20 40 60 80 100 120

-40 -20 0 20 40 60 80 100 120

Temperature (°C) Temperature (°C)

VIN Current vs. Temperature VIN Current vs. Temperature

190 160

DDR3 @ VCNTL=3.3V

180

DDR3 @ VCNTL=5V 150

VIN Current (uA)

VIN Current (uA)

170

140

160

130

150

140 120 LP DDR @ VCNTL=3.3V

LP DDR @ VCNTL=5V

130 110

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature (°C) Temperature (°C)

Turn On/Off Threshold vs. Temperature VCNTL Shutdown Current vs. Temperature

0.5 70

0.45

0.4 65

VCNTL Current (uA)

0.35

Voltage (V)

0.3 60

0.25

0.2 55

0.15 Turn On @ VCNTL=3.3V

Turn On @ VCNTL=5V VCNTL=3.3V

0.1 Turn Off @ VCNTL=3.3V 50

0.05 Turn Off @ VCNTL=5V VCNTL=5V

0 45

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature (°C) Temperature (°C)

Publication Date: Mar., 2010

-19- Revision A5

W83312SN

DDR1 Current Limit vs. Temperature DDR2 Current Limit vs. Temperature

5 5

Source @ VCNTL=3.3V Source @ VCNTL=3.3V

4.5 Source @ VCNTL=5V 4.5 Source @ VCNTL=5V

Sink @ VCNTL=3.3V Sink @ VCNTL=3.3V

4 Sink @ VCNTL=5V 4 Sink @ VCNTL=5V

Current (A)

Current (A)

3.5 3.5

3 3

2.5 2.5

2 2

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature (°C) Temperature (°C)

DDR3 Current Limit vs. Temperature LP DDR Current Limit vs. Temperature

5 5

Source @ VCNTL=3.3V Source @ VCNTL=3.3V

4.5 Source @ VCNTL=5V 4.5 Source @ VCNTL=5V

Sink @ VCNTL=3.3V Sink @ VCNTL=3.3V

4 Sink @ VCNTL=5V 4 Sink @ VCNTL=5V

Current (A)

Current (A)

3.5 3.5

3 3

2.5 2.5

2 2

-40 -20 0 20 40 60 80 100 120 -40 -20 0 20 40 60 80 100 120

Temperature (°C) Temperature (°C)

Publication Date: Mar., 2010

-20- Revision A5

W83312SN

Normalized VOFFSET vs. Temperature Normalized VOFFSET vs. Temperature

5.00 5.00

4.00 4.00

3.00 3.00

VOFFSET (mV)

2.00 2.00

VOFFSET (mV)

1.00 1.00

0.00 0.00

-1.00

-1.00

-2.00

-2.00

-3.00 DDR1 @ VCNTL=3.3V

-3.00 DDR2 @ VCNTL=3.3V

-4.00 DDR1 @ VCNTL=5V

-4.00 DDR2 @ VCNTL=5V

-5.00

-5.00

-40 -20 0 20 40 60 80 100 120

-40 -20 0 20 40 60 80 100 120

Temperature (°C)

Temperature (°C)

Normalized VOFFSET vs. Temperature Normalized VOFFSET vs. Temperature

5.00 5.00

4.00 4.00

3.00 3.00

VOFFSET (mV)

2.00 2.00

VOFFSET (mV)

1.00 1.00

0.00 0.00

-1.00 -1.00

-2.00 -2.00

-3.00 DDR3 @ VCNTL=3.3V -3.00 LP DDR @ VCNTL=3.3V

-4.00 DDR3 @ VCNTL=5V LP DDR @ VCNTL=5V

-4.00

-5.00

-5.00

-40 -20 0 20 40 60 80 100 120

-40 -20 0 20 40 60 80 100 120

Temperature (°C) Temperature (°C)

Publication Date: Mar., 2010

-21- Revision A5

W83312SN

9. PACKAGE DIMENSION

SOP8-EP (150mil)

Publication Date: Mar., 2010

-22- Revision A5

W83312SN

¾ TAPING SPECIFICATION

Note: W83312SN L/F size is D1-3 & E1-3 dimension

SOP8-EP Package

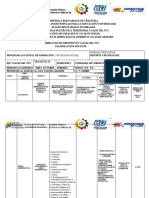

10. ORDERING INFORMATION

Part Number Package Type Supplied as Production Flow

W83312SN 8PIN SOP8-EP (Green Package) T Shape: 2,500 units/T&R Commercial, -40°C to +85°C

11. TOP MARKING SPECIFICATION

W83312SN

752ABBX

1st Line: Nuvoton logo

2nd Line: W83312SN (Part number)

3rd line: Tracking code

z 752: packages assembled in Year 2007, week 52

z A: assembly house ID

z BB: Internal use only

z X: the IC version (A means A; B means B & C means C…etc.)

Publication Date: Mar., 2010

-23- Revision A5

W83312SN

12. REVISION HISTORY

VERSION DATE PAGE DESCRIPTION

A1 11/28/2008 All New Create

Update the linear regulator chart &

A2 12/29/2008 4, 5, 7

VIN Recommended Range

1. Updated operating temperature range

A3 8/1/2009 All 2. Updated 6.2 General Regulator

3. Updated Typical Operating Waveforms

A4 1/29/2010 6 Correct Typo, add PCB Layout Suggestion

1. Add suggestion land pattern

A5 3/31/2010 6,20

2. Update the SOP8-EP package outline

Important Notice

Nuvoton products are not designed, intended, authorized or warranted for use as components

in systems or equipment intended for surgical implantation, atomic energy control

instruments, airplane or spaceship instruments, transportation instruments, traffic signal

instruments, combustion control instruments, or for other applications intended to support or

sustain life. Further more, Nuvoton products are not intended for applications wherein failure

of Nuvoton products could result or lead to a situation wherein personal injury, death or

severe property or environmental damage could occur.

Nuvoton customers using or selling these products for use in such applications do so at their

own risk and agree to fully indemnify Nuvoton for any damages resulting from such improper

use or sales.

Publication Date: Mar., 2010

-24- Revision A5

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- List of ORV Side Stories (외전)Document20 pagesList of ORV Side Stories (외전)sacrificial Squid100% (7)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Predator (5e Class) HomebrewDocument10 pagesPredator (5e Class) HomebrewDick DansleyNo ratings yet

- The Beekeeper and The Bewitched Hare Exercise PDFDocument2 pagesThe Beekeeper and The Bewitched Hare Exercise PDFsobia khan33% (3)

- Pci & Pci-E Sephiroth Kwon Grma 2009-05-26.Document32 pagesPci & Pci-E Sephiroth Kwon Grma 2009-05-26.Flaviano Costa SilvaNo ratings yet

- KQCPET6 V6 WTcard PictorialManual-iDocument59 pagesKQCPET6 V6 WTcard PictorialManual-iFlaviano Costa SilvaNo ratings yet

- GS324-Low Power QUAD Operational AmplifiersDocument9 pagesGS324-Low Power QUAD Operational AmplifiersFlaviano Costa SilvaNo ratings yet

- Power States of Motherboard Good To Note DownDocument3 pagesPower States of Motherboard Good To Note DownFlaviano Costa SilvaNo ratings yet

- ME1117 Microne PDFDocument13 pagesME1117 Microne PDFFlaviano Costa SilvaNo ratings yet

- GS358 GlobaltechDocument9 pagesGS358 GlobaltechFlaviano Costa SilvaNo ratings yet

- G 41 CheckpoinDocument3 pagesG 41 CheckpoinFlaviano Costa SilvaNo ratings yet

- Anpec Electronics Corporation Apm4115pu E9dfa47844Document11 pagesAnpec Electronics Corporation Apm4115pu E9dfa47844Flaviano Costa SilvaNo ratings yet

- Scheme-Hp Pavilion Dv5 - Intel Qt6Document44 pagesScheme-Hp Pavilion Dv5 - Intel Qt6sergeybezrNo ratings yet

- A Grande Tribulação - 1º Trimestre de 2016 (MT 24.21,22 AP 7.13,14)Document2 pagesA Grande Tribulação - 1º Trimestre de 2016 (MT 24.21,22 AP 7.13,14)Flaviano Costa SilvaNo ratings yet

- Modelos de ScriptsDocument10 pagesModelos de ScriptsFlaviano Costa SilvaNo ratings yet

- Script para Deletar Arquivos TemporáriosDocument9 pagesScript para Deletar Arquivos TemporáriosFlaviano Costa SilvaNo ratings yet

- Peças Compatíveis Ford MondeoDocument3 pagesPeças Compatíveis Ford MondeoFlaviano Costa Silva100% (1)

- Código de Barras EAN 13 e EAN 8 - Delphi - CódigoFonteDocument10 pagesCódigo de Barras EAN 13 e EAN 8 - Delphi - CódigoFonteFlaviano Costa SilvaNo ratings yet

- POO - Delphi - Leonardo QuartieriDocument10 pagesPOO - Delphi - Leonardo QuartieriFlaviano Costa SilvaNo ratings yet

- Guia Ibby 2018 Web PDFDocument190 pagesGuia Ibby 2018 Web PDFDavid Ricardo RBNo ratings yet

- 3e - Reseaux - Info - Exos2 - 2016 - CopieDocument9 pages3e - Reseaux - Info - Exos2 - 2016 - CopiehichamlamNo ratings yet

- La TendresseDocument2 pagesLa TendresseAntoine des CourtisNo ratings yet

- First Unit NotesDocument10 pagesFirst Unit NotesShekhar JainNo ratings yet

- Fisica 2Document1 pageFisica 2Juan AceroNo ratings yet

- Fiche Technique LituanieDocument3 pagesFiche Technique LituaniealexNo ratings yet

- Guía Prueb Unidad I El Mundo de Los CuentosDocument12 pagesGuía Prueb Unidad I El Mundo de Los CuentosRossanna SepulvedaNo ratings yet

- Contrato de Aprendizaje de Estadistica Inferial Psicologia SocialDocument4 pagesContrato de Aprendizaje de Estadistica Inferial Psicologia SocialMayibel AponteNo ratings yet

- Guia PapelucoDocument4 pagesGuia PapelucoMORALES BURGOS MARÍA INÉS DEL CARMENNo ratings yet

- Plano de Aula 06 Aprofundando ConhecimentosDocument6 pagesPlano de Aula 06 Aprofundando ConhecimentosLuci RamosNo ratings yet

- Encocado de PescadoDocument7 pagesEncocado de PescadoYibel ChavezNo ratings yet

- Test de BoscoDocument15 pagesTest de BoscoDiomedes GarciaNo ratings yet

- Correlación Entre La Música y El Comportamiento SocioculturalDocument8 pagesCorrelación Entre La Música y El Comportamiento SocioculturalEnrique CabreraNo ratings yet

- Beef Kaldereta RecipeDocument2 pagesBeef Kaldereta RecipeJessie ParagasNo ratings yet

- Test For 6 GradersDocument1 pageTest For 6 GradersByamba Erdene Nyam OsorNo ratings yet

- Team Sports Rules and RegulationsDocument5 pagesTeam Sports Rules and RegulationsFrancess Angel LadananNo ratings yet

- Aristotle and SidneyDocument17 pagesAristotle and SidneyJohnNo ratings yet

- QR PreregDocument1 pageQR PreregZarah Charfuelan JuradoNo ratings yet

- Clasificación de Los Organismos de Agua DulceDocument16 pagesClasificación de Los Organismos de Agua DulceCecilia VazquezNo ratings yet

- Memoria DescriptivaDocument8 pagesMemoria DescriptivaRonald Chauca HuamanNo ratings yet

- The Ultimate Bro Split: 12 Weeks To Mass: The Tools You Need To Build The Body You WantDocument1 pageThe Ultimate Bro Split: 12 Weeks To Mass: The Tools You Need To Build The Body You WantVeerpal Singh PanesarNo ratings yet

- Personajes ExtrovertidosDocument5 pagesPersonajes ExtrovertidosJohnny DumancelaNo ratings yet

- Document D'appel La Tranche Sur MerDocument36 pagesDocument D'appel La Tranche Sur MerpromotionlatrancheNo ratings yet

- VV Direccionales ModularesDocument11 pagesVV Direccionales ModularesGerardo MolinaNo ratings yet

- Proficiencies-Snare DrumDocument3 pagesProficiencies-Snare DrumDominic NorringtonNo ratings yet

- Maya Camera ProjectionDocument12 pagesMaya Camera Projectionmaacpie8353No ratings yet

- Pending Cannabis Licence ApplicationsDocument5 pagesPending Cannabis Licence ApplicationsAnonymous NbMQ9Ymq100% (1)