Professional Documents

Culture Documents

A New Aproach To Fast Gate Design

A New Aproach To Fast Gate Design

Uploaded by

ed2510 ratings0% found this document useful (0 votes)

7 views2 pagesOriginal Title

a new aproach to fast gate design

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

7 views2 pagesA New Aproach To Fast Gate Design

A New Aproach To Fast Gate Design

Uploaded by

ed251Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 2

A New Approach to Fast Gate Design

A unique sampii

1g gate

offers the highes

George Frye

Project Engineer, Sampling

Fig 1 shows a section of delay line with switches inserted

at point A and point C. A nonloading voltmeter placed

at point B, measures the average of the voltage between

the switches when the switch section is opened. When a

fast step is applied to the line and the switches then

opened, the following observations may be made,

IE the step propagating down the line is at point A when

the switch opens, 0 volts are observed. If the switches

are reclosed and a second observation made at a later

time, when the wavefront has reached point C, the

voltage is 1. When the step is just entering the switch

at point A, we observe 0; if it i just leaving the switeh

at point C, we observe 1. Thus, we may state that the

system 0-100S¢ risetime is determined by the length of

the switch scetion or C-A. Since we know the line has

capacitance and voltage, we have effectively “trapped”

a quantity of charge (Q=CE). If we now apply this

concept 10 the model shown in fig 2, we can note some

very important observations

‘The model in fig 2 illustrates a simplified form of the

tes risetime dependency upon strobe width. This new development

‘speed sampling system to date and offers promise for even faster gates.

new sampling gate used in the Tektronix Type Set

Sampling Head. Diodes replace the switches and instead

of opening the switches simultaneously, we tur the

diodes off one after another. Although it is a balanced

system, only one half of the system will be deseribed,

‘The leading edge of the strobe pulse turns the diodes

fon and the signal propagates into the conducting diodes

and transmission line. The diodes remain on for the

duration of the strobe pulse, being turned off by the

tailing edge of the wave shape. The strobe pulse is

designed to be longer than the transit time between the

diodes.

Gate action begins when the strobe trailing edge turns

D2 off. At the same time, suppose a signal front enters

through conducting diode DI. When the front reaches

D2, it is off since the strobe arrived there prior to the

front, The signal front reflects and reaches D1 which

is now off since the strobe tailing edge has preceded

the front. Thus, the signal front has been effectively

tapped in the transmission line between the two diodes,

Note, howover, that the gate characteristics are deter-

mined by the strobe tailing edge (only one transition)

TIMeE—> |.

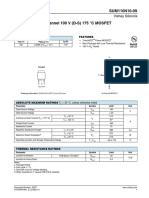

DIODE JUNCTION

sl 50ps Le —

|

a VOLTAGE DROP

5

g ----

tn

S DIODE BACK

Fa BIAS

a

g

a

IDENTICAL -Gt

CONVENTIONAL NEW TYPE $-4

STROBE STROBE

‘The conventionst sampling gate must take the diode from 2 fully off condition, turn fully-on, and return it 08 fully. off condition. The ine

between the two {uly-off conetione, ys the sooo wlth an determines the reste Of the aystam, In the Type S-4 got, the diodes

{ullvon as te ection egies, and oniy ane transition is mended. Risetime is determined by the length ofthe transmsion lin a8 pointes ou

the text. The conventional strobe for 3 fest sampling gate te very narrow since the robe width determines the system resting. The Type

{sess wide stab and minimizes the probleme inherent in narrow strobe generators

‘Only one transition is required for the gate action (gate my

In this system, the 0-100%6 risetime is determined by [——~ 1

tosice the propagation time between D1 and D2, since |

both the front and the strobe must traverse the distance. |

‘The important points to note are the following: (1) | =r _stoe

a —————: 4

Gif condition). Using one aration offers aubwantal

seis reduetion possibile, (2) "The setine of the

Sten ih not dependent spon the abe wdkh (3)

The propacedon tne eevee des sm thie ate

(15 pt fe much lest than the noe pod of appre

rraly 200 pr. (4) Beease the dies currently ed

may be turned. in B10 po they do not pov a

Fig 2, Simplified mode of sampling gate for Type 8-4

| Fi

|

Non-Loaoine vit @)

8

Fig 2. 25-08 hybrid gate, 6 Tektronix-manutactured diode chips are

Pisces ona ceramic substrate The substrate Is focmed with slots

{010301 which remove high dielectric constant material ear the

tie to fede shun captions, The dade chip are et 0 Be,

fxtending over the slot, to minimize lead Inductencs. Dp ts in the

iret to correc for signals capactvely caupled through the gate

‘odes when they are not conducting Tolonby!

Fig 1. Delaytine ection

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5813)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Doroga W Rosiju 1Document343 pagesDoroga W Rosiju 1marinusj074732100% (1)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Schottky Diode Integrated Circuits MmwaveDocument231 pagesSchottky Diode Integrated Circuits Mmwaveed251No ratings yet

- Ted Yapo Supercon 20191Document104 pagesTed Yapo Supercon 20191ed251No ratings yet

- Info-R12s0000.015f VisDocument4 pagesInfo-R12s0000.015f Vised251No ratings yet

- Sampling Head 101Document61 pagesSampling Head 101ed251No ratings yet

- LLC Design by Using Scaling Laws Rev12 1Document57 pagesLLC Design by Using Scaling Laws Rev12 1ed251No ratings yet

- LLC Resonant Converter Topologies and Industrial Applications A ReviewDocument12 pagesLLC Resonant Converter Topologies and Industrial Applications A Reviewed251No ratings yet

- Sum 110 N 1Document8 pagesSum 110 N 1ed251No ratings yet

- MCP1824Document35 pagesMCP1824ed251No ratings yet

- pm12645s pm13666s Series-778050Document5 pagespm12645s pm13666s Series-778050ed251No ratings yet

- Buck Converter 101Document55 pagesBuck Converter 101ed251No ratings yet

- LM 5010Document32 pagesLM 5010ed251No ratings yet

- 74 LCX125 FairchildDocument13 pages74 LCX125 Fairchilded251No ratings yet

- LM358DRDocument20 pagesLM358DRed251No ratings yet

- LM4041Document7 pagesLM4041ed251No ratings yet

- LM8261Document35 pagesLM8261ed251No ratings yet

- 74LCX125Document13 pages74LCX125ed251No ratings yet