Professional Documents

Culture Documents

ALD810026

Uploaded by

Juan GaleanoCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ALD810026

Uploaded by

Juan GaleanoCopyright:

Available Formats

ADVANCED

LINEAR

DEVICES, INC.

ALD810026/ALD910026

e

EPAD

EN

®

AB

TM

LE

D

QUAD/DUAL SUPERCAPACITOR AUTO BALANCING (SAB™) MOSFET ARRAY

GENERAL DESCRIPTION FEATURES & BENEFITS

The ALD810026/ALD910026 are members of the ALD8100xx • Simple and economical to use

(quad) and ALD9100xx (dual) family of Supercapacitor Auto Bal- • Precision factory trimmed

ancing MOSFETs, or SAB™ MOSFETs. SAB MOSFETs are built • Automatically regulates and balances leakage currents

with production proven EPAD® technology and are designed to ad- • Effective for supercapacitor charge-balancing

dress voltage and leakage-current balancing of supercapacitors • Balances up to 4 supercaps with a single IC package

connected in series. Supercapacitors, also known as ultracapacitors • Balances 2-cell, 3-cell, 4-cell series-connected supercaps

• Scalable to larger supercap stacks and arrays

or supercaps, connected in series can be leakage-current balanced • Near zero additional leakage currents

by using a combination of one or more devices connected across • Zero leakage at 0.3V below rated voltages

each supercapacitor stack to prevent over-voltages. • Balances series and/or parallel-connected supercaps

• Leakage currents are exponential function of cell voltages

The ALD810026 offers a set of unique, precise operating voltage • Active current ranges from <0.3nA to >1000µA

and current characteristics for each of four SAB MOSFET devices, • Always active, always fast response time

as shown in its Operating Electrical Characteristics table. It can be • Minimizes leakage currents and power dissipation

used to balance up to four supercapacitors connected in series.

The ALD910026 has its own set of unique precision Operating Elec-

trical Characteristics for each of its two SAB MOSFET devices, APPLICATIONS

suitable for up to two series-connected supercapacitors.

• Series-connected supercapacitor cell leakage balancing

• Energy harvesting

Each SAB MOSFET features a precision gate threshold voltage in • Long term backup battery with supercapacitor outputs

the Vt mode, which is 2.60V when the gate-drain source terminals • Zero-power voltage divider at selected voltages

(VGS = VDS) are connected together at a drain-source current of • Matched current mirrors and current sources

IDS(ON) = 1µA. In this mode, input voltage VIN = VGS = VDS. Dif- • Zero-power mode maximum voltage limiter

ferent VIN produces an Output Current IOUT = IDS(ON) character- • Scaled supercapacitor stacks and arrays

istic and results in an effective variable resistor that varies in value

exponentially with VIN. This VIN, when connected across each PIN CONFIGURATIONS

supercapacitor in a series, balances each supercapacitor to within

its voltage and current limits. ALD810026

When VIN = 2.60V is applied to an ALD810026/ALD910026, its 16

IC* 1 IC*

IOUT is 1µA. For a 100mV increase in VIN, to 2.70V, IOUT increases

by about tenfold. For an additional increase in VIN to 2.82V for the M1 M2

ALD910026 (2.84V for the ALD810026), IOUT increases one hun- DN1 2 15 DN2

dredfold, to 100µA. Conversely, for a 100mV decrease in VIN to

2.50V, IOUT decreases to one tenth of its previous value, to 0.1µA. GN1 3 14 GN2

Another 100mV decrease in input voltage would reduce IOUT to

0.01µA. Hence, when an ALD810026/ALD910026 SAB MOSFET SN1 4 V- V- 13 SN2

is connected across a supercapacitor that charges to less than

2.40V, it would dissipate essentially no power.

(Continued on next page) V- 5 12 V+

M4 M3

DN4 6 11 DN3

PRODUCT FAMILY SPECIFICATIONS

GN4 7 10 GN3

For more information on supercapacitor balancing, how SAB

MOSFETs achieve automatic supercapacitor balancing, the device V- V-

characteristics of the SAB MOSFET family, product family product SN4 8 9 SN3

selection guide, applications, configurations, and package infor-

mation, please download from www.aldinc.com the document: SCL PACKAGE

“ALD8100xx/ALD9100xx Family of Supercapacitor Auto Balanc-

ALD910026

ing (SAB™) MOSFET ARRAYs”

IC* 1 V- 8 V+

GN1 2 7 GN2

ORDERING INFORMATION (“L” suffix denotes lead-free (RoHS))

Operating Temperature Range DN1 3 6 DN2

Package 0°C to +70°C -40°C to +85°C

SN1 4 5 SN2, V-

(Commercial) (Industrial)

16-Pin SOIC ALD810026SCL ALD810026SCLI SAL PACKAGE

8-Pin SOIC ALD910026SAL ALD910026SALI *IC pins are internally connected, connect to V-

©2014 Advanced Linear Devices, Inc., Vers. 2.0 www.aldinc.com 1 of 6

GENERAL DESCRIPTION (CONT.) APPLYING THE ALD810026/ALD910026:

The voltage dependent characteristic of the ALD810026/ 1) Select a maximum supercapacitor leakage current limit for any

ALD910026 on-resistance is effective in controlling excessive volt- supercapacitor used in the stack. This is the same as output cur-

age rise across a supercapacitor when connected across it. In se- rent, IOUT = IDS(ON), of the ALD810026/ALD910026. Test that each

ries-connected supercapacitor stacks, when one supercapacitor supercapacitor leakage current meets this maximum current limit

voltage rises, the voltage of the other supercapacitors drops, with before use in the stack.

the ones that have the highest leakage currents having the lowest

supercapacitor voltages. The SAB MOSFETs connected across 2) Determine whether the input voltage VIN (VGS = VDS) at that

these supercapacitors would exhibit complementary opposing cur- IOUT is acceptable for the intended application. This voltage is the

rent levels, resulting in little additional leakage currents other than same voltage as the maximum desired operating voltage of the

those caused by the supercapacitors themselves. supercapacitor. For example, with the ALD810026, IOUT = 10µA

corresponds to VIN = 2.70V.

For technical assistance, please contact ALD technical support at

techsupport@aldinc.com. 3) Determine that the operating voltage margin, due to various

tolerances and/or temperature effects, is adequate for the intended

operating environment of the supercapacitor.

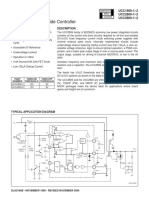

SCHEMATIC DIAGRAM OF A TYPICAL

CONNECTION FOR A FOUR-SUPERCAP STACK

V+ ≤ +15.0V

ALD8100XX

IDS(ON) ≤ 80mA

2, 12 SCHEMATIC DIAGRAM OF A TYPICAL

+ CONNECTION FOR A TWO-SUPERCAP STACK

3

M1 C1

4 V+ ≤ +15.0V

V1 ALD9100XX

15 IDS(ON) ≤ 80mA

14 +

M2 C2

13 3, 8

2 +

V2 C1

11 M1

10 + 4

M3 C3

V1

9 6

7 +

V3

6 M2 C2

7 +

M4 C4

1, 5

1, 5, 8, 16

1-16 DENOTES PACKAGE PIN NUMBERS 1-8 DENOTES PACKAGE PIN NUMBERS

C1-C4 DENOTES SUPERCAPACITORS C1-C2 DENOTES SUPERCAPACITORS

ALD810026/ALD910026 Advanced Linear Devices, Inc. 2 of 6

ABSOLUTE MAXIMUM RATINGS

V+ to V- voltage 15.0V

Drain-Source voltage, VDS 10.6V

Gate-Source voltage, VGS 10.6V

Operating Current 80mA

Power dissipation 500mW

Operating temperature range SCL 0°C to +70°C

Operating temperature range SCLI -40°C to +85°C

Storage temperature range -65°C to +150°C

Lead temperature, 10 seconds +260°C

CAUTION: ESD Sensitive Device. Use static control procedures in ESD controlled environment.

OPERATING ELECTRICAL CHARACTERISTICS

V+ = +5V, V- = GND, TA = 25°C, VIN = VGS =VDS, IOUT = IDS(ON) unless otherwise specified

ALD810026

Parameter Symbol Min Typ Max Unit Test Conditions

Gate Threshold Voltage Vt 2.58 2.60 2.62 V VGS = VDS; IDS(ON) = 1µA

Offset Voltage VOS 5 20 mV Vt1 - Vt2 or Vt3 - Vt4

Offset Voltage Tempco TCVOS 5 µV/C Vt1 - Vt2 or Vt3 - Vt4

Gate Threshold Voltage Tempco TCVt -2.2 mV/C VGS = VDS; IDS(ON) = 1µA

Output Current IOUT 0.0001 µA VIN = 2.20V

Drain Source On Resistance RDS(ON) 22000 MΩ

Output Current IOUT 0.001 µA VIN = 2.30V

Drain Source On Resistance RDS(ON) 2300 MΩ

Output Current IOUT 0.01 µA VIN = 2.40V

Drain Source On Resistance RDS(ON) 240 MΩ

Output Current IOUT 0.1 µA VIN = 2.50V

Drain Source On Resistance RDS(ON) 25 MΩ

Output Current IOUT 1 µA VIN = 2.60V

Drain Source On Resistance RDS(ON) 2.6 MΩ

Output Current IOUT 10 µA VIN = 2.70V

Drain Source On Resistance RDS(ON) 0.27 MΩ

Output Current IOUT 100 µA VIN = 2.84V

Drain Source On Resistance RDS(ON) 0.028 MΩ

Output Current IOUT 300 µA VIN = 2.94V

Drain Source On Resistance RDS(ON) 0.01 MΩ

Output Current IOUT 1000 µA VIN = 3.12V

Drain Source On Resistance RDS(ON) 0.003 MΩ

Output Current IOUT 3000 µA VIN = 3.42V

Drain Source On Resistance RDS(ON) 0.001 MΩ

Output Current IOUT 10000 µA VIN = 4.02V

Drain Source On Resistance RDS(ON) 0.0004 MΩ

Drain Source Breakdown Voltage BVDSX 10.6 V

Drain Source Leakage Current1 IDS(OFF) 10 400 pA VIN = VGS = VDS = Vt - 1.0

VIN = VGS = VDS = Vt - 1.0,

4 nA TA = +125°C

Gate Leakage Current1 IGSS 5 200 pA VGS = 5.0V, VDS = 0V

VGS = 5.0V, VDS = 0V,

1 nA TA = +125°C

Input Capacitance CISS 15 pF VGS = 0V, VDS = 5.0V

Turn-on Delay Time ton 10 ns

Turn-off Delay Time toff 10 ns

Crosstalk 60 dB f = 100KHz

ALD810026/ALD910026 Advanced Linear Devices, Inc. 3 of 6

ABSOLUTE MAXIMUM RATINGS

V+ to V- voltage 15.0V

Drain-Source voltage, VDS 10.6V

Gate-Source voltage, VGS 10.6V

Operating Current 80mA

Power dissipation 500mW

Operating temperature range SAL 0°C to +70°C

Operating temperature range SALI -40°C to +85°C

Storage temperature range -65°C to +150°C

Lead temperature, 10 seconds +260°C

CAUTION: ESD Sensitive Device. Use static control procedures in ESD controlled environment.

OPERATING ELECTRICAL CHARACTERISTICS

V+ = +5V, V- = GND, TA = 25°C, VIN = VGS =VDS, IOUT = IDS(ON) unless otherwise specified

ALD910026

Parameter Symbol Min Typ Max Unit Test Conditions

Gate Threshold Voltage Vt 2.58 2.60 2.62 V VGS = VDS; IDS(ON) = 1µA

Offset Voltage VOS 5 20 mV Vt1 - Vt2

Offset Voltage Tempco TCVOS 5 µV/C Vt1 - Vt2

Gate Threshold Voltage Tempco TCVt -2.2 mV/C VGS = VDS; IDS(ON) = 1µA

Output Current IOUT 0.0001 µA VIN = 2.20V

Drain Source On Resistance RDS(ON) 22000 MΩ

Output Current IOUT 0.001 µA VIN = 2.30V

Drain Source On Resistance RDS(ON) 2300 MΩ

Output Current IOUT 0.01 µA VIN = 2.40V

Drain Source On Resistance RDS(ON) 240 MΩ

Output Current IOUT 0.1 µA VIN = 2.50V

Drain Source On Resistance RDS(ON) 25 MΩ

Output Current IOUT 1 µA VIN = 2.60V

Drain Source On Resistance RDS(ON) 2.6 MΩ

Output Current IOUT 10 µA VIN = 2.70V

Drain Source On Resistance RDS(ON) 0.27 MΩ

Output Current IOUT 100 µA VIN = 2.82V

Drain Source On Resistance RDS(ON) 0.028 MΩ

Output Current IOUT 300 µA VIN = 2.90V

Drain Source On Resistance RDS(ON) 0.01 MΩ

Output Current IOUT 1000 µA VIN = 3.04V

Drain Source On Resistance RDS(ON) 0.003 MΩ

Output Current IOUT 3000 µA VIN = 3.10V

Drain Source On Resistance RDS(ON) 0.001 MΩ

Output Current IOUT 10000 µA VIN = 3.60V

Drain Source On Resistance RDS(ON) 0.0004 MΩ

Drain Source Breakdown Voltage BVDSX 10.6 V

Drain Source Leakage Current1 IDS(OFF) 10 400 pA VIN = VGS = VDS = Vt - 1.0

VIN = VGS = VDS = Vt - 1.0,

4 nA TA = +125°C

Gate Leakage Current1 IGSS 5 200 pA VGS = 5.0V, VDS = 0V

VGS = 5.0V, VDS = 0V,

1 nA TA = +125°C

Input Capacitance CISS 30 pF VGS = 0V, VDS = 5.0V

Turn-on Delay Time ton 10 ns

Turn-off Delay Time toff 10 ns

Crosstalk 60 dB f = 100KHz

ALD810026/ALD910026 Advanced Linear Devices, Inc. 4 of 6

SOIC-16 PACKAGE DRAWING

16 Pin Plastic SOIC Package

E

Millimeters Inches

Dim Min Max Min Max

A 1.35 1.75 0.053 0.069

S (45°)

A1 0.10 0.25 0.004 0.010

b 0.35 0.45 0.014 0.018

C 0.18 0.25 0.007 0.010

D-16 9.80 10.00 0.385 0.394

E 3.50 4.05 0.140 0.160

D

e 1.27 BSC 0.050 BSC

H 5.70 6.30 0.224 0.248

L 0.60 0.937 0.024 0.037

A ø 0° 8° 0° 8°

S 0.25 0.50 0.010 0.020

e A1

b

S (45°)

H C

L

ø

ALD810026/ALD910026 Advanced Linear Devices, Inc. 5 of 6

SOIC-8 PACKAGE DRAWING

8 Pin Plastic SOIC Package

E

Millimeters Inches

Dim Min Max Min Max

A 1.35 1.75 0.053 0.069

S (45°) A1 0.10 0.25 0.004 0.010

b 0.35 0.45 0.014 0.018

C 0.18 0.25 0.007 0.010

D-8 4.69 5.00 0.185 0.196

D

E 3.50 4.05 0.140 0.160

e 1.27 BSC 0.050 BSC

H 5.70 6.30 0.224 0.248

A L 0.60 0.937 0.024 0.037

ø 0° 8° 0° 8°

e A1

S 0.25 0.50 0.010 0.020

b

S (45°)

H C

L

ø

ALD810026/ALD910026 Advanced Linear Devices, Inc. 6 of 6

You might also like

- Shield of Archangel Michael Manual PDFDocument6 pagesShield of Archangel Michael Manual PDFKrishnaraj Rao100% (1)

- Stihl ms-210 ms-230 Ms-250.iplDocument17 pagesStihl ms-210 ms-230 Ms-250.iplRosario SimbariNo ratings yet

- Fishing Lecture NotesDocument47 pagesFishing Lecture Notes1234jj100% (1)

- Hydac Plastic Injection Molding MachinesDocument12 pagesHydac Plastic Injection Molding MachinespeterNo ratings yet

- Detroit Motor Katalog Rez DelovaDocument544 pagesDetroit Motor Katalog Rez DelovaStefan BabicNo ratings yet

- 62 Low Voltage TransformersDocument36 pages62 Low Voltage TransformersBob Mitzel NavarreteNo ratings yet

- Water Vapor Transmission Through Building Materials and SystemsDocument172 pagesWater Vapor Transmission Through Building Materials and SystemsWeb dev100% (1)

- Revista ABB 4-2015 - 72dpiDocument108 pagesRevista ABB 4-2015 - 72dpiCarlos Arturo BediaNo ratings yet

- Design and Engineering Manual - DEM2Document13 pagesDesign and Engineering Manual - DEM2Vicks BTBNo ratings yet

- Wartsila O E RT Flex82T MIM Part 1.Document397 pagesWartsila O E RT Flex82T MIM Part 1.Uhrin ImreNo ratings yet

- FRC Hellas 8014Document10 pagesFRC Hellas 8014Tulia TapiaNo ratings yet

- Vs-Vskt320Pbf Series: Vishay SemiconductorsDocument7 pagesVs-Vskt320Pbf Series: Vishay SemiconductorsRyu DanNo ratings yet

- Max2606 DatasheetDocument15 pagesMax2606 DatasheetAddy JayaNo ratings yet

- 2.4Ghz Monolithic Voltage-Controlled Oscillators: General Description FeaturesDocument6 pages2.4Ghz Monolithic Voltage-Controlled Oscillators: General Description FeaturesGerard PabloNo ratings yet

- 8900 DsDocument14 pages8900 DsSergei OssifNo ratings yet

- 1A, 76V, High-Efficiency Maxpower Step-Down DC-DC Converter: General Description FeaturesDocument17 pages1A, 76V, High-Efficiency Maxpower Step-Down DC-DC Converter: General Description FeaturesPanait MihaiNo ratings yet

- Yamaha Rx-A1040 Rx-V1077 SMDocument200 pagesYamaha Rx-A1040 Rx-V1077 SMJunius du PlessisNo ratings yet

- CN0303Document6 pagesCN0303FabioDangerNo ratings yet

- Yamaha Rx-V685 Receiver SMDocument132 pagesYamaha Rx-V685 Receiver SMfabio menezesNo ratings yet

- DP-R7090 DP-R6090: Instruction ManualDocument24 pagesDP-R7090 DP-R6090: Instruction ManualdddNo ratings yet

- LM6361Document11 pagesLM6361api-3825669No ratings yet

- N-Channel 650 V, 0.43 Ω Typ., 9 A Mdmesh™ M5 Power Mosfets In A Dpak, D²Pak, To-220Fp And To-220 PackagesDocument30 pagesN-Channel 650 V, 0.43 Ω Typ., 9 A Mdmesh™ M5 Power Mosfets In A Dpak, D²Pak, To-220Fp And To-220 Packagesmcantraks17No ratings yet

- VS-VSKD56.., VS-VSKE56.., VS-VSKJ56.., VS-VSKC56.. Series: Vishay SemiconductorsDocument9 pagesVS-VSKD56.., VS-VSKE56.., VS-VSKJ56.., VS-VSKC56.. Series: Vishay SemiconductorsDjimiNo ratings yet

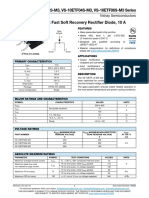

- VS-10ETF02S-M3, VS-10ETF04S-M3, VS-10ETF06S-M3 Series: Vishay SemiconductorsDocument8 pagesVS-10ETF02S-M3, VS-10ETF04S-M3, VS-10ETF06S-M3 Series: Vishay SemiconductorsjorgeNo ratings yet

- Str-A6251 Str-A6252 PDFDocument7 pagesStr-A6251 Str-A6252 PDFrafalero1No ratings yet

- Vs-Vsk.230..Pbf Series: Vishay SemiconductorsDocument9 pagesVs-Vsk.230..Pbf Series: Vishay SemiconductorsrenidwilNo ratings yet

- Max8901 Max8901bDocument14 pagesMax8901 Max8901bPM AlejandroNo ratings yet

- VSKT106 16S90P VishayDocument9 pagesVSKT106 16S90P VishayjoseNo ratings yet

- VS-20ETS08S-M3, VS-20ETS12S-M3 Series: Vishay SemiconductorsDocument7 pagesVS-20ETS08S-M3, VS-20ETS12S-M3 Series: Vishay SemiconductorsSediq AlkharashiNo ratings yet

- CN0193 PDFDocument3 pagesCN0193 PDFSanthosh Kumar H ONo ratings yet

- 1.5A Low Drop Fixed and Adjustable Positive Voltage RegulatorsDocument18 pages1.5A Low Drop Fixed and Adjustable Positive Voltage RegulatorsteknoalexNo ratings yet

- TLE2061 PrecisionDocument82 pagesTLE2061 PrecisionvelizarkoNo ratings yet

- 400Mhz, Ultra-Low-Distortion Op Amps: - General Description - FeaturesDocument12 pages400Mhz, Ultra-Low-Distortion Op Amps: - General Description - FeaturesRobNo ratings yet

- MAX2753Document6 pagesMAX2753Moha'dNo ratings yet

- AN-1581 Application Note: High Speed Instrumentation Amplifier Using The Difference Amplifier and The JFET Input Op AmpDocument4 pagesAN-1581 Application Note: High Speed Instrumentation Amplifier Using The Difference Amplifier and The JFET Input Op AmpAbolfazl Yousef ZamanianNo ratings yet

- DV 610av S PDFDocument74 pagesDV 610av S PDFkumbrovNo ratings yet

- Datenblatt Ecsc Eng 1Document2 pagesDatenblatt Ecsc Eng 1Владимир ЗагородинNo ratings yet

- Am Modulator ProjectDocument14 pagesAm Modulator ProjectMariz-Elaine Noceja RodriguezNo ratings yet

- Programmable Gain Precision Difference Amplifier AD8271: Features Functional Block DiagramDocument20 pagesProgrammable Gain Precision Difference Amplifier AD8271: Features Functional Block DiagramAbolfazl Yousef ZamanianNo ratings yet

- IRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesDocument7 pagesIRF9630, RF1S9630SM: 6.5A, 200V, 0.800 Ohm, P-Channel Power Mosfets FeaturesAbel RodriguezNo ratings yet

- SCR 25 A 1795519Document7 pagesSCR 25 A 1795519dodifirmanNo ratings yet

- AMS1117Document8 pagesAMS1117307956387No ratings yet

- Ap64350 2Document26 pagesAp64350 2Nishanth MNo ratings yet

- IRF9640, RF1S9640SM: 11A, 200V, 0.500 Ohm, P-Channel Power Mosfets FeaturesDocument7 pagesIRF9640, RF1S9640SM: 11A, 200V, 0.500 Ohm, P-Channel Power Mosfets Featuresabduallah muhammadNo ratings yet

- Srs z1Document8 pagesSrs z1TrentungcaysoBombodealopNo ratings yet

- RECOM_11022017_RAC10-K_277Document6 pagesRECOM_11022017_RAC10-K_277A ANo ratings yet

- 8600 Rocker Switches - Miniature: 10A 250vac Single & Double PoleDocument2 pages8600 Rocker Switches - Miniature: 10A 250vac Single & Double PolemasizkaNo ratings yet

- Bav99 r1.1.0 FairchildDocument7 pagesBav99 r1.1.0 FairchildSsr ShaNo ratings yet

- Applications Features: 1985 Burr-Brown Corporation PDS-600B Printed in U.S.A. December, 1993Document6 pagesApplications Features: 1985 Burr-Brown Corporation PDS-600B Printed in U.S.A. December, 1993Ramiro Alonso Bruz SilvaNo ratings yet

- Max20050-Max20053 2A Synchronous-Buck Led Drivers With Integrated MosfetsDocument23 pagesMax20050-Max20053 2A Synchronous-Buck Led Drivers With Integrated MosfetsAdrian WongNo ratings yet

- Service Note Direct Replacemente Megamax F1 F2 OpenDoor - Novomax G2 Vs NewEmaxDocument6 pagesService Note Direct Replacemente Megamax F1 F2 OpenDoor - Novomax G2 Vs NewEmaxJatupol PongsirisartNo ratings yet

- To 247ac Anexa Tiristor BunaDocument8 pagesTo 247ac Anexa Tiristor BunanumaionelNo ratings yet

- TEA1795T: 1. General DescriptionDocument14 pagesTEA1795T: 1. General DescriptionEsau DiazNo ratings yet

- AD8611 Instrumentational AmplifierDocument12 pagesAD8611 Instrumentational AmplifierChAmirShokatGujjarNo ratings yet

- Hfe Sony Sa-Wmsp2 Wmsp4 Service enDocument12 pagesHfe Sony Sa-Wmsp2 Wmsp4 Service enAdielE.AriasNo ratings yet

- Ucc3809 1 PDFDocument23 pagesUcc3809 1 PDFAleksandar RakicNo ratings yet

- VFD-E Extension En, Manual Plc. DeltaDocument2 pagesVFD-E Extension En, Manual Plc. DeltaLuis MedinaNo ratings yet

- 320W Single Output With PFC Function: SeriesDocument3 pages320W Single Output With PFC Function: SeriesTrường NguyenNo ratings yet

- Advanced Monolithic Systems: Rohs CompliantDocument8 pagesAdvanced Monolithic Systems: Rohs CompliantQasimNo ratings yet

- 6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999Document8 pages6A, 100V, 0.600 Ohm, P-Channel Power Mosfet Features: File Number 2281.3 Data Sheet July 1999rex999No ratings yet

- IRF9520Document7 pagesIRF9520Emilio QuijanoNo ratings yet

- Descriptio Features: LT1270A/LT1270 8A and 10A High Efficiency Switching RegulatorsDocument4 pagesDescriptio Features: LT1270A/LT1270 8A and 10A High Efficiency Switching RegulatorsPedro MarcosNo ratings yet

- IRF7809A/IRF7811A IRF7809A/IRF7811A: Provisional DatasheetDocument4 pagesIRF7809A/IRF7811A IRF7809A/IRF7811A: Provisional DatasheetZak zsNo ratings yet

- Max 4639Document16 pagesMax 4639امجد عبد المحسن سعدون مهديNo ratings yet

- LM2 670 PDFDocument23 pagesLM2 670 PDFMain UddinNo ratings yet

- Ele Tro IDocument25 pagesEle Tro IArmando GodoyNo ratings yet

- STB26NM60N, STF26NM60, Sti26nm60n, STP26NM60N, STW26NM60NDocument23 pagesSTB26NM60N, STF26NM60, Sti26nm60n, STP26NM60N, STW26NM60NjjoaquimmartinsNo ratings yet

- PDFDocument4 pagesPDFIVC PUI-SKONo ratings yet

- FQP10N60C DatasheetzDocument10 pagesFQP10N60C DatasheetzagesoporteNo ratings yet

- How To Use PTC Thermistors As Current Protection - TDKDocument4 pagesHow To Use PTC Thermistors As Current Protection - TDKJuan GaleanoNo ratings yet

- Tps 61200Document35 pagesTps 61200Juan GaleanoNo ratings yet

- (Bounchaleun) AN ELEMENTARY INTRODUCTION TO FAST FOURIERDocument12 pages(Bounchaleun) AN ELEMENTARY INTRODUCTION TO FAST FOURIERJuan GaleanoNo ratings yet

- An5030 PDFDocument20 pagesAn5030 PDFCanh LuongtienNo ratings yet

- Synchronous Buck Converter For Charger of Electric Easy BikesDocument5 pagesSynchronous Buck Converter For Charger of Electric Easy BikesJuan GaleanoNo ratings yet

- Battery Supplied Arc WelderDocument5 pagesBattery Supplied Arc WelderJuan Galeano100% (1)

- Pepperl Fuchs KFU8 USC 1DDocument2 pagesPepperl Fuchs KFU8 USC 1DAlejandro AlegriaNo ratings yet

- 1.1 Introduction To KennametalDocument40 pages1.1 Introduction To KennametalVig PankajNo ratings yet

- NEO - NEET - 12 - P1 - PHY - E - Current Electricity - 09 - 211Document92 pagesNEO - NEET - 12 - P1 - PHY - E - Current Electricity - 09 - 211thenmozhishri13007No ratings yet

- Question Bank FOR Je-Ii SelectionDocument59 pagesQuestion Bank FOR Je-Ii SelectionPankaj DhandeNo ratings yet

- Unconventional Machining Processes OverviewDocument92 pagesUnconventional Machining Processes OverviewTIRUPATHI KARTIKEYANo ratings yet

- Aegis Plus Brochure (AGPBR004EN) - WDocument8 pagesAegis Plus Brochure (AGPBR004EN) - WLai Yoong LeiNo ratings yet

- Aice Unit 1 MCQDocument7 pagesAice Unit 1 MCQPoyyamozhi Nadesan RanjithNo ratings yet

- EE103 Lecture11 BGF 09 Dec 2022 Mod1 JJC 1Document16 pagesEE103 Lecture11 BGF 09 Dec 2022 Mod1 JJC 1Raunak MukherjeeNo ratings yet

- DG401 451Document2 pagesDG401 451Mauricio SaulNo ratings yet

- FR2165 Installation ManualDocument92 pagesFR2165 Installation ManualEdwin NyangeNo ratings yet

- 2019 - Vietnam Smart Grid - by Nguyen The HuuDocument27 pages2019 - Vietnam Smart Grid - by Nguyen The HuuLuong Thu HaNo ratings yet

- Technical Specification Turbine - JabalpurDocument111 pagesTechnical Specification Turbine - Jabalpursusmita.sivasankaranNo ratings yet

- Alfonso V. Ramallo PDFDocument64 pagesAlfonso V. Ramallo PDFanirbanNo ratings yet

- MAVJ Catalogue (En - 0898)Document8 pagesMAVJ Catalogue (En - 0898)renjithas2005No ratings yet

- PC2000-8 Spec SheetDocument20 pagesPC2000-8 Spec SheetNeeraj ChauhanNo ratings yet

- QualifyingExamProblemSolutionsUnivOfILLionisNotesStatisticalMechanics PDFDocument216 pagesQualifyingExamProblemSolutionsUnivOfILLionisNotesStatisticalMechanics PDFHarikrishnan GurusamyNo ratings yet

- List DRM 16-18 Jan 2019Document7 pagesList DRM 16-18 Jan 2019fuad najibullahNo ratings yet

- Stabilized Earth Fault Current Relay Settings GuideDocument20 pagesStabilized Earth Fault Current Relay Settings GuideRaj KrishNo ratings yet

- IAL-Physics Unit 3 (WPH13-01) (2020-01-10) Q+ADocument32 pagesIAL-Physics Unit 3 (WPH13-01) (2020-01-10) Q+AUClan Plant & MaintenanceNo ratings yet

- GR15 PDFDocument41 pagesGR15 PDFomkar maitreeNo ratings yet