Professional Documents

Culture Documents

Poster SOFT2018 BSantos Linux Device Driver

Uploaded by

Nuno CruzOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Poster SOFT2018 BSantos Linux Device Driver

Uploaded by

Nuno CruzCopyright:

Available Formats

Linux device driver for Radial Neutron Camera

in view of ITER long pulses with variable data throughput

B. Santos1, N. Cruz1, P.F. Carvalho1, A. Fernandes1, J. Sousa1, B. Gonçalves1, M. Riva2, F. Pollastrone2, C. Centioli2, D. Marocco2,

†,3

B. Esposito , C.M.B. Correia , J.M.R. Cardoso3 and R.C. Pereira1

2

1 Instituto de Plasmas e Fusão Nuclear, Instituto Superior Técnico, Universidade de Lisboa, Av. Rovisco Pais 1, 1049-001 Lisboa, Portugal

2 ENEA C. R. Frascati, Dipartimento FSN, via E. Fermi 45, 00044 Frascati (Roma), Italy.

3 LIBPhys-UC, Department of Physics, University of Coimbra, P-3004 516 Coimbra, Portugal

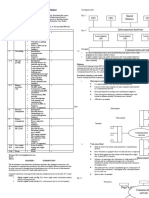

Introduction Device Driver Implementation

The ITER Radial Neutron Camera (RNC) Data Acquisition (DAQ) prototype is based on the The Device Driver implements a kernel thread to

PCIe protocol as the interface to be used between the I/O unit and the host PC, enabling for the retrieve the data from the kernel space to the user

scalability of the final RNC DAQ system and allowing a sustainable 2 MHz peak event to cope space (accessible to high-level applications).

with the long plasma discharges, up to half an hour.

The thread runs in an isolated core and polls the

The prototype architecture comprises two digitizer modules with two channels in each, installed in status DMA. Based on its value, retrieves the last

the host PC. The maximum produced data throughput is up to 0.5 GB/s per channel in event available data DMAs.

mode (1 GB/s per digitizer) and up to 1.6 GB/s in continuous mode (for test purposes). The thread transfers to the user space all written

The host PC, a high performance computer, receives the acquired data through the Direct DMAs from last status change. Typically, the number

Memory Access (DMA) channels. The Linux Device Driver provides the interface between the of DMAs to transfer is one (all transitions are

hardware and the host applications. triggered) but if some status change is missing, the

thread automatically transfers all missing data

Previous preliminary tests showed that a traditional implementation of the Linux Device Driver blocks up to the length of the kernel circular buffer.

based on interrupt handling is not suitable for demanding data throughput. The Linux kernel

Based on the prototype specification, the device

miss several interrupts and receives Transaction Layer Packets (TLP) errors, reflecting a poor

driver provides individual device nodes (and

stability of the system.

memory buffers), to retrieve the data from the pair

The directly usage of the polling mechanisms to retrieve the data is not suitable as the DMA#n, ADC #n.

variable event rate over the same discharge does not allow to define an optimum fixed time to

retrieve data and identify missing data packages.

This contribution presents the architecture, implementation and test of a different device driver

approach using the polling mechanism which improves the performance and reliability.

System Architecture Each built data DMA block have multiple channel packets which can be from different ADCs.

The kernel thread separates the data from different ADCs into independent memory buffers,

The Host Computer runs Scientific Linux 7 as using the channel packet tag, which identifies the source ADC.

Operating System with kernel 3.10-rt

The DMA #n buffers stores the

Intel® Core TM i7-5930K@3.50 GHz

non-separated data that is

256 GB SSD and 64 GB of RAM available for test purposes (only)

The FPGA sent event data through two data paths [1]: during the prototype phase.

DMA#0 - Event base raw data path The high-level applications,

reads the data from the driver

DMA#1 - Processed data path

memory buffers, based on the

Each data DMA has 8 KB. In case of the raw data path, write and read pointers.

the driver transfers data in blocks of 32 KB (4 DMAs). Error counters were implemented

The DMA#2 is a special DMA containing 32 bits with to provide real-time information

the FPGA status information about data transmission. about data packages losses.

Some validation bits and also a counter flag are added to improve the reliability of the DMA

status information Results & Conclusions

The COUNT_DMA#n and DMA#n CYCLE on the status information gives the number of sent The tests show a stable solution during 60 minutes acquisitions with data acquisition rates up

DMAs for each data path and the last memory address written by the FPGA in the kernel space. to 1.5 GB/s.

The DMA#0 has 16 memory addresses and DMA#1 has 4, and each memory address has 8 KB of Using the interrupt approach

memory space. (implemented and tested in a previous

phase of the prototype), there are

missing packets above 512 MB/s for

single DMA #0 acquisitions, and above

64 MB/s for acquisitions from two DMAs

at same time.

The packets recovered is a relevant issue to guarantee the data integrity, despite small impact.

The usage of data transmission information can be a valuable contribution to solve problems when

a traditional implementation of a Linux device driver based on interrupt handling or polling

mechanisms cannot be used.

The presented architecture is scalable and adjustable. Also, is data-agnostic because only

the status information is considered to trigger the data to transfer.

The presented solution implements an internal data transmission recovery algorithm, enabling

the device driver to automatically check and recover missing data blocks in a transparent way

for the host applications. Using a traditional approach, in which a block is transferred in each status

changed, if some transition was missed the data would be lost.

Main References:

[1] A. Fernandes et al., FPGA code for the data acquisition and real-time processing prototype of the ITER Radial Neutron Camera, 21st IEEE Real Time Conference, 2018

[2] N. Cruz et al., The design and performance of the real time software architecture for the ITER Radial Neutron Camera, 21st IEEE Real Time Conference, 2018

[3] B. Santos et al., Real-time data compression for data acquisition systems applied to the ITER Radial Neutron Camera, 21st IEEE Real Time Conference, 2018

[4] R.C. Pereira et al., Real-Time data acquisition Prototype proposal of the ITER radial neutron camera and gamma-ray spectrometer , Fusion Eng. Des. 123 (2017) 901-905

† Deceased 30 March 2018. Corresponding author: bsantos@ipfn.tecnico.ulisboa.pt

The work leading to this publication has been funded partially by Fusion for Energy under the Contract

F4E-FPA-327. IST activities also received financial support from “Fundação para a Ciência e

Tecnologia” through project UID/FIS/50010/2013. This publication reflects the views only of the author,

and Fusion for Energy cannot be held responsible for any use which may be made of the information

contained therein.

P3.060, September 19th 2018 | Related Contribution: P3.068 30th Symposium on Fusion Technology, 16-21 September 2018, Giardini Naxos, Sicily, Italy

You might also like

- Gain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipFrom EverandGain-Cell Embedded DRAMs for Low-Power VLSI Systems-on-ChipNo ratings yet

- Design of Tele Command SOC-IP by AES Cryptographic Method Using VHDLDocument4 pagesDesign of Tele Command SOC-IP by AES Cryptographic Method Using VHDLdbpublicationsNo ratings yet

- Raid Soft V HardDocument6 pagesRaid Soft V HardSang Tran MinhNo ratings yet

- Clement 1987Document4 pagesClement 1987SaharKhaneshiNo ratings yet

- Communication: The SAMPEX Data Processing Unit J. JDocument3 pagesCommunication: The SAMPEX Data Processing Unit J. Jgithin1990No ratings yet

- ITCE 720A Autonomic Wireless Networking (Fall, 2009)Document24 pagesITCE 720A Autonomic Wireless Networking (Fall, 2009)Souhila SelmaNo ratings yet

- Radio IdentificationDocument7 pagesRadio IdentificationSavindu NanayakkaraNo ratings yet

- A Summary On "Characterizing Processor Architectures For Programmable Network Interfaces"Document6 pagesA Summary On "Characterizing Processor Architectures For Programmable Network Interfaces"svasanth007No ratings yet

- NetworkingDocument55 pagesNetworkingRey Allen TenosoNo ratings yet

- Knowledge OrganiserDocument17 pagesKnowledge OrganiserTrevor ChadNo ratings yet

- The OSI Model: Understanding The Seven Layers of Computer NetworksDocument22 pagesThe OSI Model: Understanding The Seven Layers of Computer NetworksMona AliNo ratings yet

- PLUG Flexible Lookup Modules For Rapid Deployment ofDocument12 pagesPLUG Flexible Lookup Modules For Rapid Deployment ofznabugrmay20adiNo ratings yet

- Case Study: How DCE Builds a Distributed Computing EnvironmentDocument124 pagesCase Study: How DCE Builds a Distributed Computing EnvironmentSweta KamatNo ratings yet

- Performances Analysis On Video Transmission in A Wireless Sensor NetworkDocument4 pagesPerformances Analysis On Video Transmission in A Wireless Sensor Networkmukesh_asn57731No ratings yet

- The Network+ Cram Sheet: Networking ConceptsDocument4 pagesThe Network+ Cram Sheet: Networking ConceptsISTAKHAR UDDIN AHAMED100% (1)

- Performance of DSR Protocol Over Sensor Networks: 2. Related WorkDocument3 pagesPerformance of DSR Protocol Over Sensor Networks: 2. Related Workvol2no5No ratings yet

- Design Routing Protocols For Mobile Ad Hoc NetworksDocument6 pagesDesign Routing Protocols For Mobile Ad Hoc NetworksSreeni ChampNo ratings yet

- Networking Performance MicrokernelsDocument6 pagesNetworking Performance MicrokernelsBruno FissNo ratings yet

- High-Speed I/O: The Operating System As A Signalling MechanismDocument8 pagesHigh-Speed I/O: The Operating System As A Signalling MechanismiferiantoNo ratings yet

- A Reconfigurable Digital Signal Processing SystemDocument6 pagesA Reconfigurable Digital Signal Processing Systempym1506gmail.comNo ratings yet

- High Performance ComputingDocument61 pagesHigh Performance ComputingShrey Thakur100% (1)

- ITL331 Operating System and Network Programming Lab by Vinish AlikkalDocument37 pagesITL331 Operating System and Network Programming Lab by Vinish AlikkalVinish A100% (1)

- Octopus: An RDMA-enabled Distributed Persistent Memory File SystemDocument15 pagesOctopus: An RDMA-enabled Distributed Persistent Memory File SystemPrince RajNo ratings yet

- AtcDocument12 pagesAtcTodd HoffNo ratings yet

- Chapter 4-6 Review - Set 2: Divine Word UniversityDocument9 pagesChapter 4-6 Review - Set 2: Divine Word UniversityIshmael FaruNo ratings yet

- Trellis CodedDocument8 pagesTrellis CodedMiltonThitswaloNo ratings yet

- Implementation of SCTP in An Open Source Real-Time Operating SystemDocument7 pagesImplementation of SCTP in An Open Source Real-Time Operating SystemdjicccNo ratings yet

- Handbook of Multisensor Data FusionDocument4 pagesHandbook of Multisensor Data Fusionvasuhi srinivasanNo ratings yet

- An SDR Architecture For OFDM Transmission Over USRP2 BoardsDocument5 pagesAn SDR Architecture For OFDM Transmission Over USRP2 BoardsÖzkan SezerNo ratings yet

- A Scalable Hardware Accelerator For Mobile DNA SequencingDocument14 pagesA Scalable Hardware Accelerator For Mobile DNA Sequencingroopa_kothapalliNo ratings yet

- A Datacenter Network Architecture For Low Latency Automation and VirtualizationDocument3 pagesA Datacenter Network Architecture For Low Latency Automation and VirtualizationstevencuiNo ratings yet

- Ccna 1 Mind MapDocument1 pageCcna 1 Mind MapHp Slate100% (1)

- SemSim CCNA Cram SheetsDocument9 pagesSemSim CCNA Cram SheetsMohan KumarNo ratings yet

- OSI Model Reference TableDocument4 pagesOSI Model Reference Tablem_karthikeyan1118264No ratings yet

- OSI Model Reference TableDocument4 pagesOSI Model Reference Tablem_karthikeyan1118264No ratings yet

- Ex No: 6 Raw Sockets (Packet Capturing & Filtering)Document6 pagesEx No: 6 Raw Sockets (Packet Capturing & Filtering)Pitchairaj BhuvaneswariNo ratings yet

- IO Systems Streams: Subject: Operating System Ibrar Afzal Lecturer IT DepartmentDocument25 pagesIO Systems Streams: Subject: Operating System Ibrar Afzal Lecturer IT DepartmentRimshaNo ratings yet

- Go Mac PapDocument5 pagesGo Mac Papsyedsalman1984No ratings yet

- Memory Performance and Scalability of Intel's and AMD's Dual-Core Processors - A Case StudyDocument10 pagesMemory Performance and Scalability of Intel's and AMD's Dual-Core Processors - A Case StudyAnonymous Wu14iV9dqNo ratings yet

- Secure Remote Protocol For Fpga ReconfigurationDocument5 pagesSecure Remote Protocol For Fpga ReconfigurationesatjournalsNo ratings yet

- The Demikernel Datapath OS Architecture For Microsecond-Scale Datacenter SystemsDocument17 pagesThe Demikernel Datapath OS Architecture For Microsecond-Scale Datacenter Systemsrose jackNo ratings yet

- Ics 2208 Os Ii NotesDocument14 pagesIcs 2208 Os Ii NotesakdauatemNo ratings yet

- Cern-Cms-Cr-2009-323Document6 pagesCern-Cms-Cr-2009-323SebastianNo ratings yet

- Toaz - Info Project On Honeywell Tdc3000 Dcs PRDocument77 pagesToaz - Info Project On Honeywell Tdc3000 Dcs PRMorad MouradNo ratings yet

- Glossary: Cisco CRS-1 Series Carrier Routing System Getting Started Guide OL-6142-01Document20 pagesGlossary: Cisco CRS-1 Series Carrier Routing System Getting Started Guide OL-6142-01Muhammad Rizwan KhanNo ratings yet

- A Distributed Database Architecture For Global Roaming in Next-Generation Mobile NetworksDocument2 pagesA Distributed Database Architecture For Global Roaming in Next-Generation Mobile Networksapi-3838337100% (1)

- 15 - 4 - 21trans. IEEE 2012 - Software-Defined Sphere Decoding For FPGA-Based MIMO DetectionDocument10 pages15 - 4 - 21trans. IEEE 2012 - Software-Defined Sphere Decoding For FPGA-Based MIMO DetectionTiến Anh VũNo ratings yet

- Cognitive Radio Implemenation IeeeDocument6 pagesCognitive Radio Implemenation Ieeeradhakodirekka8732No ratings yet

- Coincidence DetectionDocument4 pagesCoincidence Detectionjayamala adsulNo ratings yet

- Cisco Certified Network Associate (CCNA) : Ethernet LAN Switching by Odoch Herbert Hyper SolutionsDocument12 pagesCisco Certified Network Associate (CCNA) : Ethernet LAN Switching by Odoch Herbert Hyper SolutionsOdoch HerbertNo ratings yet

- Implenting A Base StationUsing The SDRPlatforDocument4 pagesImplenting A Base StationUsing The SDRPlatforaidawei001No ratings yet

- A Demonstration of The Meshtest Wireless TestbedDocument1 pageA Demonstration of The Meshtest Wireless TestbedjamesNo ratings yet

- Software Defined NetworkingDocument13 pagesSoftware Defined NetworkingJorge Armando Soto GarcíaNo ratings yet

- 1 2 PDFDocument5 pages1 2 PDFRohit KumarNo ratings yet

- Joint Task Migration and PowerDocument3 pagesJoint Task Migration and PowerkdeepanrajNo ratings yet

- Pap IeeeDocument13 pagesPap Ieeeapi-3845765No ratings yet

- ALevel Computer Science KODocument24 pagesALevel Computer Science KOTadiambaNo ratings yet

- Improving Memory Utilization in Convolutional Neural Network AcceleratorsDocument4 pagesImproving Memory Utilization in Convolutional Neural Network AcceleratorsdaveNo ratings yet

- Various Communication Protocol A Comparative StudyDocument47 pagesVarious Communication Protocol A Comparative StudykailasamvvNo ratings yet

- Oral - Presentation - RT2018 - NCruz - RNC - Software - ArchitectureDocument14 pagesOral - Presentation - RT2018 - NCruz - RNC - Software - ArchitectureNuno CruzNo ratings yet

- NunoCruz-Abstract-IEEE-NPSS-23rd-Real-Time ConferenceDocument2 pagesNunoCruz-Abstract-IEEE-NPSS-23rd-Real-Time ConferenceNuno CruzNo ratings yet

- Presentation The SPIDER Plant Configuration EnvironmentDocument19 pagesPresentation The SPIDER Plant Configuration EnvironmentNuno CruzNo ratings yet

- IEEE TRANSACTIONS ON NUCLEAR SCIENCE - SPIDER Pulse Plant Configuration EnvironmentDocument10 pagesIEEE TRANSACTIONS ON NUCLEAR SCIENCE - SPIDER Pulse Plant Configuration EnvironmentNuno CruzNo ratings yet

- Chapter 3 - A Top Level View of Computer Function and InterconnectionDocument38 pagesChapter 3 - A Top Level View of Computer Function and InterconnectionKhang NguyenNo ratings yet

- Assignment 2 Data Defination Language: VVP Engineering CollegeDocument12 pagesAssignment 2 Data Defination Language: VVP Engineering CollegeFake 1No ratings yet

- AWS Code CatalogDocument9,862 pagesAWS Code CatalogHandigeni Digital InnovationsNo ratings yet

- DBMS Interview Questions and Answers: Sindhuja HariDocument71 pagesDBMS Interview Questions and Answers: Sindhuja HariDeepak SinghNo ratings yet

- What Impact Will Have On Your Business?: NDC in A NutshellDocument4 pagesWhat Impact Will Have On Your Business?: NDC in A NutshellAbdullahiNo ratings yet

- Security in Office 365 WhitepaperDocument26 pagesSecurity in Office 365 WhitepaperJSNo ratings yet

- Page FBDocument168 pagesPage FBLouie BelloNo ratings yet

- Sushil Chaudhary ResumeDocument4 pagesSushil Chaudhary ResumeSushil ChaudharyNo ratings yet

- Cissp-Cib-Blueprint From ISC PDFDocument46 pagesCissp-Cib-Blueprint From ISC PDFAsadMalikNo ratings yet

- Facebook's PlatformDocument6 pagesFacebook's Platformtech2click100% (2)

- Software Development Process Models GuideDocument12 pagesSoftware Development Process Models GuideJackyHongNo ratings yet

- CSC GateDocument20 pagesCSC Gatejeravi84100% (2)

- 70-744: Securing Windows Server 2016 Chapter 9 - Securing The Network InfrastructureDocument48 pages70-744: Securing Windows Server 2016 Chapter 9 - Securing The Network InfrastructureTester MaheNo ratings yet

- Introducing To Network SecurityDocument10 pagesIntroducing To Network SecuritycursantcataNo ratings yet

- 5 6071176108164776105Document29 pages5 6071176108164776105Tuyul9 TamvaanNo ratings yet

- Google AnalyticsDocument13 pagesGoogle AnalyticsPaul S100% (1)

- Introduction to Cloud Computing GuideDocument17 pagesIntroduction to Cloud Computing GuideMiftahNo ratings yet

- Affirmed Networks Network Slicing WhitepaperDocument12 pagesAffirmed Networks Network Slicing WhitepaperALEXANDRE JOSE FIGUEIREDO LOUREIRONo ratings yet

- Corporate Email Usage Policy TemplateDocument3 pagesCorporate Email Usage Policy Templateadnansensitive5057No ratings yet

- Snow Itsm OvervDocument5 pagesSnow Itsm OvervmanedeepNo ratings yet

- Data Sheet Ultrastar DC hc550Document2 pagesData Sheet Ultrastar DC hc550vlade naumovskiNo ratings yet

- Introduction To BlockchainsDocument45 pagesIntroduction To BlockchainsAdri JovinNo ratings yet

- Data Governance:: The Pragmatic WayDocument25 pagesData Governance:: The Pragmatic WayrammandoNo ratings yet

- Functional Specification Document TemplateDocument10 pagesFunctional Specification Document TemplateSRKNo ratings yet

- Learn What is SAP ALV and How to Create Simple ALV ReportsDocument2 pagesLearn What is SAP ALV and How to Create Simple ALV ReportsTAMIRE SANTOSH MOHANNo ratings yet

- COMP40451 Cyber Security Lecture 1 IntroductionDocument19 pagesCOMP40451 Cyber Security Lecture 1 IntroductionSampath Darshana100% (1)

- Assignment 3Document5 pagesAssignment 3samwel100% (1)

- SQL Record Questions Part1Document9 pagesSQL Record Questions Part1mishrapratham169No ratings yet

- Request To ResolveDocument8 pagesRequest To ResolveShrouk GamalNo ratings yet