Professional Documents

Culture Documents

System Verilog Quick 23

Uploaded by

Mani KumarCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

System Verilog Quick 23

Uploaded by

Mani KumarCopyright:

Available Formats

SYSTEM VERILOG

Statements within a program block (scheduled in the Reactive region) that are sensitive to changes in design signals declared in

modules (scheduled in the active region), as active region is scheduled before the reactive region this avoids the race condition

between testbench and design.

The syntax for the program block is,

program test (input clk, input [7:0] addr, output [7:0] wdata);

...

endprogram

Program block,

can be instantiated and ports can be connected same as module.

can contain one or more initial blocks.

cannot contain always blocks, modules, interfaces, or other programs.

In program variables can only be assigned using blocking assignments. Using non-blocking assignments with in the program

shall be an error.

5. INTERFACE:

Interface construct are used to connect the design and testbench.

An interface is a named bundle of wires, aim of the interfaces is to encapsulate communication.

Also specifies the,

directional information, i.e. modports

timing information, i.e. clocking blocks

An interface can have parameters, constants, variables, functions and tasks.

modports and clocking blocks are explained in later chapters.

A simple interface declaration is,

interface interface_name;

...

interface_items

...

endinterface

An interface can be instantiated hierarchically like a module, with or without ports.

interface_name inst_name;

Interface can have parameters, constants, variables, functions and tasks.

Advantages of interface over the traditional connection,

allows number of signals to be grouped together and represented as a single port, single port handle is passed instead of

multiple signal/ports.

interface declaration is made once and the handle is passed across the modules/components.

addition and deletion of signals is easy.

6. Virtual interface:

A virtual interface is a variable that represents an interface instance.

Syntax:

virtual interface_name instance_name;

example:

virtual mem_intf intf;

Virtual interface must be initialized before using it. i.e., Virtual interface must be connected/pointed to the actual interface.

accessing the uninitialized virtual interface result in a run-time fatal error.

Virtual interfaces can be declared as class properties, which can be initialized procedural or by an argument to new().

Virtual interface variables can be passed as arguments to the tasks, functions, or methods.

All the interface variables/Methods can be accessed via virtual interface handle. i.e virtual_interface.variable

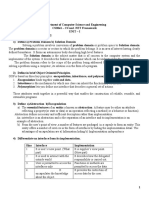

7. mod ports:

Modport groups and specifies the port directions to the wires/signals declared within in the interface.

By specifying the port directions, modport provides access restrictions.

The keyword modport indicates that the directions are declared as inside the module.

22

You might also like

- TCP/IP Sockets in Java: Practical Guide for ProgrammersFrom EverandTCP/IP Sockets in Java: Practical Guide for ProgrammersRating: 4 out of 5 stars4/5 (5)

- SystemVerilog InterfaceDocument62 pagesSystemVerilog InterfaceRanadheer Reddy100% (1)

- Sys Verilog InterfacesDocument27 pagesSys Verilog InterfacesLakshmisree SajitNo ratings yet

- Doulos SysVlog Interface Modports PaperDocument8 pagesDoulos SysVlog Interface Modports PaperkrishnaavNo ratings yet

- VHDL MaterialDocument33 pagesVHDL MaterialChutiyaNo ratings yet

- Introduction To Vlsi: 1.1 VerilogDocument3 pagesIntroduction To Vlsi: 1.1 VeriloghfytdyjNo ratings yet

- UVM Harness WhitepaperDocument12 pagesUVM Harness WhitepaperSujith Paul VargheseNo ratings yet

- Digital Design Through Verilog1Document65 pagesDigital Design Through Verilog1sruchakradarNo ratings yet

- Prelim Module5 - BDocument7 pagesPrelim Module5 - BCelimen, John Renz C.No ratings yet

- Missing Link: Testbench To DUT Connection by David RichDocument9 pagesMissing Link: Testbench To DUT Connection by David RichapninexNo ratings yet

- VHDL LabDocument50 pagesVHDL LabAnuNo ratings yet

- Unit - V: Principles of HDLDocument74 pagesUnit - V: Principles of HDLvlsijpNo ratings yet

- DP - Unit-2 - BCAIAI507 - (Elective-IV) Embedded SystemsDocument9 pagesDP - Unit-2 - BCAIAI507 - (Elective-IV) Embedded SystemsDeepak PathakNo ratings yet

- UVM Harness Whitepaper: The Missing Link in Interface ConnectivityDocument10 pagesUVM Harness Whitepaper: The Missing Link in Interface Connectivitysharath h sNo ratings yet

- LAB#4Document3 pagesLAB#4Unsa Jan Abdul QayyumNo ratings yet

- What Are Network Devices?Document7 pagesWhat Are Network Devices?Joshua SantillanaNo ratings yet

- Dica Unit-1Document18 pagesDica Unit-1PrasannaKumar KaraNamNo ratings yet

- Digital Design Lab Manual: Introduction To VerilogDocument48 pagesDigital Design Lab Manual: Introduction To VerilogKeith FernandesNo ratings yet

- U-1 Overview of HDLDocument14 pagesU-1 Overview of HDLDEEPA KUNWARNo ratings yet

- Component Technology Notes 2 PDFDocument26 pagesComponent Technology Notes 2 PDFharsh vardhanNo ratings yet

- Jaypee University of Engineering & Technology, Guna Deparment of Computer Science & EngineeringDocument7 pagesJaypee University of Engineering & Technology, Guna Deparment of Computer Science & EngineeringAmit SharmaNo ratings yet

- Verilog Lecture 1 - NoopurDocument41 pagesVerilog Lecture 1 - NoopurMonis KhanNo ratings yet

- Verilog - Excellent ExplanationDocument18 pagesVerilog - Excellent ExplanationRida AmjadNo ratings yet

- DSD Unit 1-4 PDFDocument95 pagesDSD Unit 1-4 PDFVAISHAKA N RAJNo ratings yet

- Brian Evans - Arduino Programming NotebookDocument36 pagesBrian Evans - Arduino Programming NotebookFelipeZ64100% (1)

- Arduino Fungsi SyntaxDocument36 pagesArduino Fungsi Syntaxmul21No ratings yet

- Chapter 6 - Verilog Tasks and FunctionsDocument36 pagesChapter 6 - Verilog Tasks and Functionstuananhpro972No ratings yet

- Manual SelfDocument133 pagesManual Selfchiranjeevee02No ratings yet

- 4-8 MarchDocument15 pages4-8 Marchadyadesai7No ratings yet

- Verilog TutorialDocument16 pagesVerilog Tutorialeditography.studiosNo ratings yet

- Lab - Manual LP V (2019PATERN)Document39 pagesLab - Manual LP V (2019PATERN)Vaishnavi DhimateNo ratings yet

- Basic Elements of VHDL: VHSIC Hardware Description Language (VHDL)Document3 pagesBasic Elements of VHDL: VHSIC Hardware Description Language (VHDL)Jyoti SahooNo ratings yet

- CS2041 UNIT I Question BankDocument61 pagesCS2041 UNIT I Question BankabishekNo ratings yet

- What Is Callback?: Systemverilog&Uvm Interview QuestionsDocument53 pagesWhat Is Callback?: Systemverilog&Uvm Interview QuestionsAshwini Patil100% (1)

- 1-Microcontroller Based System Design - CompleteDocument58 pages1-Microcontroller Based System Design - Completerizwan9000% (1)

- Ans Key ND20Document17 pagesAns Key ND20jgjeslinNo ratings yet

- Vlsi IV and V Units PptsDocument119 pagesVlsi IV and V Units PptsHarsha VardhanNo ratings yet

- Verilog HDL Part IIDocument61 pagesVerilog HDL Part IIdbanbumani_501791840No ratings yet

- Omnet Tutorial PDFDocument63 pagesOmnet Tutorial PDFSatya VeniNo ratings yet

- Unit IV Verilog NotesDocument69 pagesUnit IV Verilog NotesR R DeshmukhNo ratings yet

- Systemverilog Interview QuestionsDocument39 pagesSystemverilog Interview Questionsduck2No ratings yet

- Midterm Report Format PDFDocument25 pagesMidterm Report Format PDFLucy HeartfilliaNo ratings yet

- System Design Through Verilog: Rakesh DasariDocument92 pagesSystem Design Through Verilog: Rakesh DasariRakeshNo ratings yet

- Name: Hilal Rauf Subject Code: BSIT - 61 Part: TBDocument13 pagesName: Hilal Rauf Subject Code: BSIT - 61 Part: TBAm_Ehsaas0% (1)

- VHDL MiniDocument23 pagesVHDL Miniqnu07No ratings yet

- (Redhat) Linux Important StuffDocument14 pages(Redhat) Linux Important StuffJagmohan JagguNo ratings yet

- Eee 3210Document79 pagesEee 3210alihossenvoltaNo ratings yet

- DSD Unit 1Document39 pagesDSD Unit 1Kanushi BawejaNo ratings yet

- Assignment For BC0047Document7 pagesAssignment For BC0047Padam ThapaNo ratings yet

- Java / J2EE Interview Questions You'll Most Likely Be AskedFrom EverandJava / J2EE Interview Questions You'll Most Likely Be AskedNo ratings yet

- SRS - How to build a Pen Test and Hacking PlatformFrom EverandSRS - How to build a Pen Test and Hacking PlatformRating: 2 out of 5 stars2/5 (1)

- ORACLE PL/SQL Interview Questions You'll Most Likely Be AskedFrom EverandORACLE PL/SQL Interview Questions You'll Most Likely Be AskedRating: 5 out of 5 stars5/5 (1)

- Serial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded SystemsFrom EverandSerial Port Complete: COM Ports, USB Virtual COM Ports, and Ports for Embedded SystemsRating: 3.5 out of 5 stars3.5/5 (9)

- Operating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesFrom EverandOperating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesNo ratings yet

- Hacks To Crush Plc Program Fast & Efficiently Everytime... : Coding, Simulating & Testing Programmable Logic Controller With ExamplesFrom EverandHacks To Crush Plc Program Fast & Efficiently Everytime... : Coding, Simulating & Testing Programmable Logic Controller With ExamplesRating: 5 out of 5 stars5/5 (1)

- Beginning Jakarta EE: Enterprise Edition for Java: From Novice to ProfessionalFrom EverandBeginning Jakarta EE: Enterprise Edition for Java: From Novice to ProfessionalNo ratings yet

- Lecture 1 Introduction To Control SystemsDocument22 pagesLecture 1 Introduction To Control SystemsDr. Haider Zaman Lecturer Electronics ABTNo ratings yet

- Manual Programador TSX T317 PDFDocument64 pagesManual Programador TSX T317 PDFJhon Florez100% (1)

- Kovic 4Document16 pagesKovic 4Francis BurerosNo ratings yet

- Vessel, Jacketed Vessel, Reactor Atmospheric Tank, Storage: 7.8 Documentation ExamplesDocument7 pagesVessel, Jacketed Vessel, Reactor Atmospheric Tank, Storage: 7.8 Documentation ExamplesnmulyonoNo ratings yet

- Tubesheet LayoutDocument5 pagesTubesheet LayoutMehta MehulNo ratings yet

- SQLServerGeeks Magazine June 2021Document45 pagesSQLServerGeeks Magazine June 2021rexpanNo ratings yet

- AMS Webminar July 7, 2021Document73 pagesAMS Webminar July 7, 2021ignaciomacipe9968No ratings yet

- In Group14 AssignmentDocument40 pagesIn Group14 AssignmentJimmy ChengNo ratings yet

- Business Analytics - The Science of Data Driven Decision MakingDocument55 pagesBusiness Analytics - The Science of Data Driven Decision Makingmathewsujith31No ratings yet

- Saf 7113 HTDocument80 pagesSaf 7113 HTgheo23No ratings yet

- Eva Karera - Google SearchDocument1 pageEva Karera - Google SearchSachin AnandNo ratings yet

- Casa L4 - A1-03Document1 pageCasa L4 - A1-03Benjamin CarrionNo ratings yet

- Ops MGT SaumuDocument8 pagesOps MGT SaumuSaumu SuleimanNo ratings yet

- A Survey On The Use of ICT in Teaching Learning Practices in College Level MathematicsDocument5 pagesA Survey On The Use of ICT in Teaching Learning Practices in College Level MathematicsAndrea Espino Kipad ReidNo ratings yet

- ISO55000 Series Overview Slides NowDocument8 pagesISO55000 Series Overview Slides Nownasrulsalman9883No ratings yet

- 6 1 Reducing Rational Expressions To Lowest TermsDocument21 pages6 1 Reducing Rational Expressions To Lowest Termsapi-233527181No ratings yet

- ECA Particles in Parenterals KombiDocument6 pagesECA Particles in Parenterals KombiBLUEPRINT Integrated Engineering ServicesNo ratings yet

- Global Data Center Newsletter - 2023.06.15Document22 pagesGlobal Data Center Newsletter - 2023.06.15indr4m4 7u5ufNo ratings yet

- Series N Hydro Pneumatic Press Cylinder PDFDocument11 pagesSeries N Hydro Pneumatic Press Cylinder PDFranjith sanNo ratings yet

- DownloadDocument2 pagesDownloadvinayNo ratings yet

- SPD Compatible Pedals: SM-SH51 SM-SH55Document1 pageSPD Compatible Pedals: SM-SH51 SM-SH55Bernardo LizardiNo ratings yet

- Troubleshooting&Best Practices For ReadUnread MarksDocument34 pagesTroubleshooting&Best Practices For ReadUnread Marksnet2raviNo ratings yet

- Gas Measuring and Alarm Systems: Exdetector Hc-100Document7 pagesGas Measuring and Alarm Systems: Exdetector Hc-100joseNo ratings yet

- EdScratch Student Lesson ActivitiesDocument242 pagesEdScratch Student Lesson Activitiesلينا ابو عمرNo ratings yet

- 1 s2.0 S1877050922018336 MainDocument8 pages1 s2.0 S1877050922018336 MainIdvano IdboyNo ratings yet

- Machine-Level Programming IV: x86-64 Procedures, DataDocument44 pagesMachine-Level Programming IV: x86-64 Procedures, Datadarwinvargas2011No ratings yet

- 4 Levels of Training KPIsDocument8 pages4 Levels of Training KPIsSonal ChaturvediNo ratings yet

- BUSI - 502 Information Systems For Management: On-Line Course Syllabus Course DescriptionDocument13 pagesBUSI - 502 Information Systems For Management: On-Line Course Syllabus Course DescriptionAdrian BrownNo ratings yet

- COMPRO PT Elning Heksa Karya - 2021 UpdatedDocument24 pagesCOMPRO PT Elning Heksa Karya - 2021 UpdatedEngineering AstonNo ratings yet

- Game Programming-Cse3029 Lab Assignment-5: Working With Collision SystemsDocument7 pagesGame Programming-Cse3029 Lab Assignment-5: Working With Collision SystemsPenchal DoggalaNo ratings yet