Professional Documents

Culture Documents

ADADC80

ADADC80

Uploaded by

alexander0 ratings0% found this document useful (0 votes)

15 views6 pagesADC de 12 bit

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentADC de 12 bit

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

15 views6 pagesADADC80

ADADC80

Uploaded by

alexanderADC de 12 bit

Copyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 6

ANALOG

DEVICES

12-Bit Successive Approximation

Integrated Circuit A/D Converter

AD ADC80

FEATURES

‘True 12-Bit Operation: Max Nonlinearity +0.012%

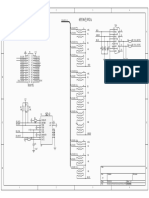

FUNCTIONAL BLOCK DIAGRAM

Low Gain T.C.: 430ppm/C max

‘Low Power: 800mW am

Fast Conversion Time: 25s ors are

Precision 6.3V Reference for External Application

Short Cycle Capability a ae

Serial of Parallel Data Outputs eS oD

Monolithic DAC with Scaling Resistors for Sabi

Low Chip Count—High Reliability on orn

\eriustry Standard Pinout rss wr aise

"2" Models for +12V Supplies sovnmos

arr sevon av

See ae

aw aout ‘AD Apce0 ssvorsny

PRODUCT DESCRIPTION

‘The AD ADC80 is a complete 12-bit successive approximation

analog-to-digital converter that includes an internal clock, refer-

tence and comparator. Its hybrid IC design utilizes MSI digital

and linear monolithie chips in conjunction with a 12-bit mono-

lithie DAC to provide modular performance and versatility with

IC size, price and reliability

Important performance characteristics of the AD ADCBO in

clude a maximum linearity error at +25°C of 10.012%, max

{tin T.C. of 30ppm/*C, typical power dissipation of 800mW

and max conversion time of 25s, Monotonic operation of the

feedback D/A converter guarantees no missing codes over the

‘temperature range of -25°C to +85°C.

‘The design of the AD ADC80 includes sealing resistors that

provide analog signal ranges of #2.5, +5.0, +10, 0to #5 or 0

to +10 volts. The 6,3V precision reference may be used for ex-

ternal applications. All digital signals are fully DTL and TTL.

compatible; ourput data may be read in both serial and par

allel form.

The AD ADC8O is available in two performance grades, the

[AD ADC80-12 (0.012% of FSR max) and the AD ADC80-10

(0.048% of FSR max). Both grades are specified for use over

the -25°C to +85°C temperature range and both are available

ina 32-pin ceramic DIP.

REV.A

Information furnished by Analog Davos is boleved tobe accurate and

‘liable, Howaver, no responsibilty assumed by Analog Devices forts

a, nor for any infingamants of patots or other sights of third

‘which may reaut from ts vee. No lesneo granted by implication oF

‘thenwise under any patent or patent rights of Ansiog Daviess

PRODUCT HIGHLIGHTS

1. The AD ADC80 is a complete 12-bit A/D converter. No

external components are required to perform a conversion.

2. A monolithic 12-bit feedback DAC is used for reduced

chip count and higher reliability,

3. The internal buried zener reference is laser trimmed to 6.3,

volts. The reference voltage is available externally and can

supply up to 1.5mA beyond that required for the reference

and bipolar offset curzent.

4. The sealing resistors are included on the monolithic DAC.

for exceptional thermal tracking.

5. The AD ADC80 directly replaces other devices of this type

‘with significant increases in performance,

6, The fast conversion rate of the AD ADC8O makes it an

excellent choice for applications requiring high system.

‘throughput rates.

17. The short eycle and external clock options are provided for

applications requiring faster conversion speeds or lower

resolutions

(One Technology Way, P.0. Box 3106, Norwood, MA 02062-9106, U.S.A.

Tel: 617/329-4700 Fax: 617/926-6703 Twx: 710/984-6577

Telex: 924491 Cable: ANALOG NORWOODMASS

AD ADC8O—SPECIFICATIONS isto +250, =v ant +8¥ ues oer sess

Loge Loting titted

Linen Eon a Eoraclesk oon ofF5R

Irn arn Sor Bis :

Spcficion Temperate Range -2s°C10 45°C

Soon Boonie

‘ioe spy of SRE

tar ss) pom esc

Savension see au p.25ama yma

spor os

our srr tna

sue ape Bang cameron

renpesl Dal opp ey 2209p" ma

FowER REQUIREMENTS a

Sporting (Dome Spee) fe

Seat ats Beiter

SSR es FATE Raat egg oo rg a 20

+200 minor gop,

Tee Coe camper) ome a

xe, > Goer) foe Colne

‘tor pttnge tone formancn we Fcage efron ston

‘usta hs

‘tees tt eng ont

DIFFERENTIAL

so T T

ser| |\ser\ gen

vase]

‘vaisa|

O24 es a 0 7 ww 2 a 2 2s

‘CONVERSION TIME —

Figure 1. Linearity Error vs. Conversion

Time (Normalized)

=

3

&

vaso}

oa ae eo ee ee me ee ee 8

Figure 2. Differential Linearity Error vs.

Conversion Time (Normalized)

B 0a T

3 oa :

E os —

35s a8

Tenvenatune —

Figure 3. Moximum Gain Dit Error=% of

FSA vs. Temperature

* oe

& ons

a

5 cna

8 om

3 oo

E 008

3 ove

oe eB 700

‘TEMPERATURE —"C

Figure 4, Reference Drift—% Error

vs. Temperature

REV. A

Applying the AD ADC8O

‘THEORY OF OPERATION

(On receipt of a CONVERT START command, the AD ADC80

converts the voltage at its analog input into an equivalent 12-

bit binary number. This conversion is accomplished as follows:

the 12-bit suecessive-approximation register (SAR) has its

12-bit outputs connected both to the device bit output pins

and to the corresponding bit inputs of the feedback DAC.

‘The analog input is successively compared to the feedback

DAC output, one bit ata time (MSB first, LSB last). The

decision to keep or reject each bit is then made at the com-

pletion of each bit comparison period, depending on the state

of the comparator at that time,

TIMING

‘The timing diagram is shown in Figure 5. Receipt of a CON.

VERT START signal sets the STATUS flag, indicating conver-

sion in progress. This, in turn, removes the inhibit applied to

the gated clock, permitting it to run through 13 cycles, All

SAR parallel bit and STATUS flip-flops are initialized on the

leading edge, and the gated clock inhibit signal is removed on

the traling edge of the CONVERT START signal. At time to,

By is reset and Bz ~Byz ate set unconditionally. At ty the Bit 1

decision is made (keep) and Bit 2 is unconditionally reset. At

tg, the Bit 2 decision is made (keep) and Bit 3 is reset uncon

ditionally. This sequence continues until the Bit 12 (LSB) de-

cision (keep) is made at ¢y2. After a 40ns delay period, the

STATUS flag is reset, indicating that the conversion is com-

plete and that the parallel output data is valid. Resetting the

STATUS flag restores the gated clock inhibie signal, forcing the

clock output to the Logic “0” state.

Corresponding serial and parallel data bits become valid on

the same positive going clock edge. Serial data does not change

and is guaranteed valid on negative going clock edges, however;

serial data can be transferred quite simply by clocking it into a

receiving shift register on these edges (see Figure $)

Incorporation of this 4Ons delay guarantees that the parallel

(and serial) data are valid at the Logie ‘1” to “0” transition

ff the STATUS flag, permicting parallel data transfer to be

initiated by the trailing edge of the STATUS signal.

[____waximum tunoucheur rime ———»

convert! :

START CONVERSION TIME (2) ———_——=t

INTERNAL

eLock,

STATUS

MsB

Bir2

airs

Bra

airs

sir.

Bir7

aire

aro

BIT 10

Biri

tse

SERIAL

Daa

our

Notes:

4. THE CONVERT START PULSE WIDTH IS 100ns MIN AND MUST REMAIN LOW DURING

ACONVERSION. THE CONVERSION IS INITIATED BY THE

CONVERT COMMAND.

ISING EDGE” OF THE

2. 254s FOR 12 BITS AND 21s FOR 10 BITS (MAX).

nN

5. MsB DEC!

(0

4. [SB DECISION 40ns PRIOR TO THE STATUS GOING LOW

*BIT DECISIONS

Figure §. Timing Diagram (Binary Code 011001110110)

REV. A

AD ADC8O

DIGITAL OUTPUT DATA

Both parallel and serial data from TTL storage registers are in

negative true form, Parallel data output coding is complemen:

tary binary for unipolar ranges and either complementary off-

set binary or complementary two's complement binary, de-

pending on whether BIT 1 (pin 6) or its logical inverse BIT 1

(pin 8) is used as the MSB, Parallel data becomes valid approx:

imately 40ns before the STATUS flag returns to Logic “0”,

permitting parallel data transfer to be clocked on the “1” to

transition of the STATUS flag.

Serial data coding is complementary binary for unipolar input

ranges and complementary offset binary for bipolar input

ranges. Serial output is by bit (MSB first, LSB last) in NRZ.

(non-etuen-to-zero) format. Serial and parallel data outputs

‘change state on positive going clock edges, Serial data is guaran-

teed valid 200ns after the rising clock edges, permitting serial

data to be clocked directly into a receiving register on these

edges as shown in Figure 5, There are 13 negative going clock

edges in the complete 12-bit conversion cycle, as shown in Fig:

luce 5. The first edge shifts an invalid bit into the register,

which is shifted out on the 13th negative going clock edge. All

serial data bits will have been correctly transferred and be in

the receiving shift register locations shown at the completion

‘of the conversion period.

Short Cycle Input: A Short Cycle Input, pin 21, permits the

‘timing cycle shown in Figure 5 to be terminated after any

number of desited bits has been converted, permitting some

‘what shorter conversion times in applications not requiring full

12-bit resolution, When 10-bit resolution is desired, pin 21 is,

‘connected to Bit 11 output pin 28. The conversion cycle then

‘terminates, and the STATUS flag resets after the Bit 10 de-

cision (ty9 +40ns in timing diagram of Figure 5). Short

Cyele pin connections and associated maximum 12-, 10- and,

‘bit conversion times are summarized in Table 1, When 12-

bit resolution is required, pin 21 is connected to +5V (pin 9).

Connect Short Maximum Status Flag

Cycle Fin 24 t0 Resolution Conversion Reset

Pin: Bits (GFSR) Time (us)

9 12 0.024 25 ty +40ns

28 10 0.100 21 typ *40ns

30 & 0390 17 ty +40ns

Table J. Short Cycle Connections

INPUT SCALING

‘The AD ADCBO input should be scaled as close to the maxi-

mum input signal range as possible in order to utilize the

maximum signal resolution of the A/D converter. Connect the

input signal as shown in Table Il. See Figure 6 for circuit

details.

tov RANGE 12

owenitn a

COREE 2 OA Vues

ANALOG

Set 8

Figure 6 AD ADC8O Input Scaling Circuit

Connect

Inpue Connect Connect Input

Signal Ouput Pint? Pin 14 ‘Signal

Range Code ToPin = To To

s10v COBorCTC 11 Imput Signal 14

sv COBorCTC 11 Open B

225V coBorcTc 11 Pin 11 B

oVio+5V CSB 18 Pint B

OVto+10V CSB 15 Open B

Table Il. AD ADC8O Input Scaling Connections

ae oe INPUT VOLTAGE RANGE AND LSB VALUES

Anaog tpt

Votege Range Defined As: 10V av sasv ovwsov ovat

Code cos con cos

Designation Sere orerc* weer cs esses

One test BR ov oy, ¥ wy wy

Senifcane = " 8 ” e

Bess) : aasmy 39.05mv Dassmv 39.0607 essay

1353mv 370m aan oat aa

aan Dam anv Peavy aan

Transition Values

BSB tse

oo. 000"t** sfullScue —HOV-32LSB5V-372LSB2SV-3RLSB sLOV-3ALSB SV 372LsB

tttcin Mase ° ° ° “sv “asv

Mio MunStle tov ‘uatse-sveiatss —-2svelnisn ovimise ——ovi58

Team = complementary Ofte Binary

Sct = Complementary Ts

ot

mor agian ie (HSB). MSE salle pln 8

Sh = Complementary Sigh Binay

Voltages ven ar the nomial ale fr eanson tothe code pec

mplspeat-obtaied by as the complement

Table IH. Input Voltages and Code Definitions

REV. A

AD ADC80

OFFSET ADJUSTMENT

‘The zero adjust cizcuit consists ofa potentiometer connected

across 2Vg with its sider connected through a 1.8M&92 resistor

{© Comparator Input pin 11 forall ranges. As shown in Figure

7 the tolerance of this fixed resistor isnot critical, and cat-

bon composition type is generally adequate. Using a catbon

composition resistor having «-1200ppm/*C tempco contributes

a worst-case offset tempco of 8X 244X 10° X 1200ppm/*C =

2.3ppm/°C of FSR, if the OFFSET AD) potentiometer is set

at either end of its adjustment range. Since the maximum off

set adjustment requited is typically no more than *4LSB, use

of «carbon composition offser summing resistor typically com-

tributes no more than Ippm/C of FSR offset tempeo.

Figure 7. Offset Adjustment Circuit

‘An alternate offset adjust circuit, which contributes negli-

gible offset tempco if metal film resistors (tempeo <100

ppm/°C) are used, is shown in Figure 8.

Figure 8 Low Tempco Zero Adjustment Circuit

In either zero adjust circuit, the fixed resistor connected to

pin 11 should be located clase to this pin to keep the pin 11

connection runs short (Comparator Input pin 11 is quite

sensitive to external noise pick-up).

GAIN ADJUSTMENT

‘The gain adjust circuit consists of a potentiometer connected

across #Vs with it slider connected through 2 10M® resistor

to the gain adjust pin 16 as shown in Figure 9.

Figure 9. Gain Adjustment Circuit

‘An alternate gain adjust circuit which contributes negligible

sin tempco if metal film resistors (Tempco <100ppm/"C) are

‘used is shown in Figure 10.

Figure 10. Low Tempco Gain Adjustment Circuit

REV. A

CALIBRATION

External ZERO ADJ and GAIN AD] potentiometers, com:

nected as shown in Figures 11 and 12, are used for device

calibration. To prevent interaction of these two adjustments,

Zero is always adjusted first and then Gain. Zero is adjusted

“with the analog input near the most negative end of the analog

range (0 for unipolar and -FS for bipolar input ranges). Gain

is adjusted with the analog input near the most positive end of

‘the analog range

0 to +10V Range: Set analog input to +1LSB = +0.0024V.

‘Adjust Zero for digital output = 111111111110. Zero is now

calibrated. Set analog input to +FSR -2LSB = +9.9952V.

‘Adjust Gain for 000000000001 digital output code; full-

scale (Gain) is now calibrated. Halfscale calibration check:

set analog input to +5.0000V ; digital output code should be

ounnaniait

-10V co +10V Range: Set analog input to -9.9951V; adjust

‘Zero for 111111111110 digital output (complementary offset

binary) code. Set analog input to +9.9902V; adjust Gain for

(000000000001 digital output (complementary offset binary)

code. Halfscale calibration check: set analog input to 0.0000V;,

digital output (complementary offset binary) code should be

onmnannt11

Other Ranges: Representative digital coding for 0 to +10V and

=1OV to #10V ranges is given above. Coding celationships and

calibration points for 0 to +5V, -2.5V to +2.5V and -SV to

+5V ranges can be found by halving the corresponding code

‘equivalents listed for the 0 to +10V and ~1OV to +10V ranges,

respectively,

Zero and full-scale calibration can be accomplished to a pre-

cision of approximately #1/4LSB using the static adjustment

procedure described above. By summing a small sine or tri-

angular-wave voltage with the signal applied to the analog in-

put, the output can be cycled through each of the calibration,

‘codes of interest to more accurately determine the center (or

end points) of each discrete quantization level. A detailed

description of this dynamic calibration technique is presented

in “A/D Conversion Notes,” D. Sheingold, Analog Devices,

Inc., 1977, Part Il, Chapter 3.

‘ni

>

Figure 11

Unipolar 0-10V Input Range

Analog and Power Connections for

AD ADC80

Figure 12, Analog and Power Connections for Bipolar

2 70V Input Range

GRouNDING

Many data-acqusition component have two ot more ground

which are not connected together within the device. These

junds” are usally referred to asthe Logic Power Return,

‘Analog Gommon (Analog Power Return), and Analog Signal

Ground. These grounds must be tied together atone point

Usually atthe system powersupply ground. Ideally single

solid ground would be desirable, However, since current flows

through the ground wires and etch strips of the circuit eards,

and since these paths have resistance and inductance, hundreds

‘of millivolts can be generated between the system ground point

andthe ground pin ofthe AD ADCEO, Therefore, separate

ground rem should be provided to minimize the current

Flow inthe path from sensitive points tothe system ground

point and te two device grounts shouldbe ted together. In

this way supply currents and logie-gae rerum currents are not

summed into the same ream path as analog signals where

they would cause measurement error.

Each of the AD ADC80's supply terminals should be capaci

tively decoupled a close to the AD ADCEO as possible. A

Inne value capacitor such as 14 in parallel with a 0.140

capacitor i usualy safficint. Analog supplies are bypassed

to the Analog Power Return pin and the logic supply is by-

passed tothe Logic Power Revurn pin

(eins so aoceo E

Figure 13, Basic Grounding Practice

CONTROL MODES

‘The timing sequence of the AD ADC80 allows the device to

be easily operated in a variety of systems with different con

tol modes. The most common control modes are illustrated in

Figures 14-16,

Dade oe ae,

exer lent Bnon

Figure 14. Internal Clock Normal Operating Mode.

‘Conversion Initiated by the Rising Edge of the Convert

‘Command. The Internal Clock Runs Only During

Conversion.

‘Ap ADce0

Figure 15, Continuous Conversion with External Clock.

Conversion is Initiated by 14th Clock Pulse. Clack Runs

Continuousiy.

OE 1 /

a

Figure 16. Continuous External Clock. Conversion Initiated

by Rising Edge of Convert Command. The Convert Command

‘must be Synchronized with Clock.

OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

Lees

REV.A

You might also like

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5813)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (844)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- PW 2004 08Document80 pagesPW 2004 08alexanderNo ratings yet

- MICRORDDocument9 pagesMICRORDalexanderNo ratings yet

- MICRORAMDocument8 pagesMICRORAMalexanderNo ratings yet

- MICROJDocument12 pagesMICROJalexanderNo ratings yet

- Uvtron: Flame SensorDocument4 pagesUvtron: Flame SensoralexanderNo ratings yet

- LSM330DLDocument54 pagesLSM330DLalexanderNo ratings yet

- Ambion: Wearnes CambionDocument2 pagesAmbion: Wearnes CambionalexanderNo ratings yet

- MICROASMD005FDocument2 pagesMICROASMD005FalexanderNo ratings yet

- ADC 10bit 4 CanalesDocument16 pagesADC 10bit 4 CanalesalexanderNo ratings yet

- QL85H6S AbcDocument5 pagesQL85H6S AbcalexanderNo ratings yet

- Roku 4 Streaming Player 4400R User ManualDocument15 pagesRoku 4 Streaming Player 4400R User ManualalexanderNo ratings yet

- Avera Digital TV 50AER10 - User ManualDocument32 pagesAvera Digital TV 50AER10 - User ManualalexanderNo ratings yet

- Sceptre TV E243BV-FHD - User ManualDocument52 pagesSceptre TV E243BV-FHD - User ManualalexanderNo ratings yet

- 851 Datasheet-16963Document2 pages851 Datasheet-16963alexanderNo ratings yet

- Filtro 500khzDocument2 pagesFiltro 500khzalexanderNo ratings yet

- Elenberg 1402,2108,21F08,29F08 Service ManualDocument85 pagesElenberg 1402,2108,21F08,29F08 Service ManualalexanderNo ratings yet

- VGA SchematicDocument1 pageVGA SchematicalexanderNo ratings yet

- LM60 2.7V, SOT-23 or TO-92 Temperature Sensor: Features ApplicationsDocument17 pagesLM60 2.7V, SOT-23 or TO-92 Temperature Sensor: Features ApplicationsalexanderNo ratings yet

- 234 Series,: 5×20 MM Medium-Acting 234 SeriesDocument3 pages234 Series,: 5×20 MM Medium-Acting 234 SeriesalexanderNo ratings yet

- DS EPU BlackbirdDocument3 pagesDS EPU BlackbirdalexanderNo ratings yet