Professional Documents

Culture Documents

Pulse Width Modulation

Uploaded by

Smruti Pore0 ratings0% found this document useful (0 votes)

8 views16 pagesOriginal Title

PWM

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

8 views16 pagesPulse Width Modulation

Uploaded by

Smruti PoreCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 16

PULSE WIDTH MODULATION

6 single edge controlled PWM outputs

or 3 double edge controlled PWM outputs

or a mix of both types

The match registers also allow:

Continuous operation with optional interrupt

generation on match.

Stop timer on match with optional interrupt

generation.

Reset timer on match with optional interrupt

generation

Single edge controlled PWM outputs all go high

at the beginning of each cycle.

Double edge controlled PWM outputs can have

either edge occur at any position within a cycle.

This allows for both positive going and negative

going pulses.

Pulse period and width can be any number of

timer counts. This allows complete flexibility in

the trade-off between resolution and repetition

rate

Two match registers can be used to provide a

single edge controlled PWM output.

One match register (PWMMR0) controls the PWM

cycle rate, by resetting the count upon match.

The other match register controls the PWM edge

position

Additional single edge controlled PWM outputs

require only one match register each

PWM1 - Output from PWM channel 1.

PWM2 - Output from PWM channel 2.

PWM3 - Output from PWM channel 3.

PWM4 - Output from PWM channel 4.

PWM5 - Output from PWM channel 5.

PWM6 - Output from PWM channel 6.

PWMTCR PWM Timer Control Register-

It is used to control the Timer Counter functions. The Timer

Counter can be disabled or reset through the PWMTCR.

PWMTC PWM Timer Counter-

The 32-bit TC is incremented every PWMPR+1 cycles of

PCLK. The PWMTC is controlled through the PWMTCR.

PWMPR PWM Prescale Register-

The PWMTC is incremented every PWMPR+1 cycles of

PCLK

PWMMCR PWM Match Control Register-

The PWMMCR is used to control if an interrupt is

generated and if the PWMTC is reset when a Match occurs

PWMMR0 PWM Match Register 0.

PWMMR0 can be enabled through PWMMCR to

reset the PWMTC, stop both the PWMTC and

PWMPC, and/or generate an interrupt when it

matches the PWMTC.

In addition, a match between PWMMR0 and the

PWMTC sets all PWM outputs that are in single-

edge mode, and sets PWM1 if it is in double-edge

mode.

7:4 3 2 1 0

PWM Enable - Counter Reset Counter Enable

1=PWM mode is 1=PWM Timer Counter 1= PWM Timer

enabled. and the PWM Prescale Counter and PWM

PWM mode causes Counter are synchronously Prescale

shadow registers to reset on the next positive Counter are enabled

operate in connection edge of PCLK. The for counting.

with the Match counters remain reset until 0=counters are

registers TCR is returned to zero. disabled.

20- 17- 14- 11- 8-7-6 5-4-3 2 1 0

19- 16- 13-12 10-9

18 15

PWMMR0S PWMMR0R PWMMR0I

PW PW PWM PWM PWM PWM 1: Stop on 1: Reset on 1: Interrupt on

MM MM MR4 MR3 MR2 MR1 PWMMR0: the PWMMR0: PWMMR0: an

R6BI R5 BITS BITS BITS BITS PWMTC and the interrupt is

TS BITS PWMPC will be PWMTC generated

stopped and will be when

PWMTCR[0] reset if PWMMR0

will be set to 0 PWMMR0 matches the

if PWMMR0 matches it. value in the

matches the PWMTC

PWMTC

Enables PWM outputs and selects PWM

channel types as either single edge or double

edge controlled.

15 14 13 12 11 10 9 8:7 6 5 4 3 2 1:0

PWM PWM PWM PWM PWM PWM PWM PWM PWM PWM PWM

ENA6 ENA5 ENA4 ENA3 ENA2 ENA1 SEL6 SEL5 SEL4 SEL3 SEL2

1 = Enable 1=Selects double edge

0 = disable controlled mode for the PWM

output

0=Selects single edge

controlled mode for PWM

The PWM Latch Enable Register is used to

control the update of the PWM Match

registers when they are used for PWM

generation

7 6 5 4 3 2 1 0

- Enable Enable Enable Enable Enable Enable Enable

PWM PWM PWM PWM PWM PWM PWM

Match 6 Match 5 Match 4 Match 3 Match 2 Match 1 Match 0

Latch Latch Latch Latch Latch Latch Latch

Writing a one to this bit allows the last value written to the PWM Match register

to be become effective when the timer is next reset by a PWM Match event

#include <LPC214X.H>

#define PWMPRESCALE 60

void initPWM(void)

{

PINSEL0 = (1<<1); // Select PWM1 output for Pin0.0

PWMPCR = 0x0;

PWMPR = PWMPRESCALE-1; // 1 micro-second resolution

PWMMR0 = 20000; // 20ms = 20k us - period duration

PWMMR1 = 1000; // 1ms - pulse duration i.e width

PWMMCR = (1<<1); // Reset PWMTC on PWMMR0 match

PWMLER = (1<<1) | (1<<0); // update MR0 and MR1

PWMPCR = (1<<9); // enable PWM output

PWMTCR = (1<<1) ; //Reset PWM TC & PR

PWMTCR = (1<<0) | (1<<3); // enable counters and PWM Mode

}

]int main(void)

{

initPWM(); //Initialize PWM

while(1)

{

if( !((IOPIN0) & (1<<1)) ) // Check P0.1

{

PWMMR1 = 4000;

PWMLER = (1<<1); //Update Latch

Enable bit for PWMMR1

}

else if( !((IOPIN0) & (1<<2)) ) // Check P0.2

{

PWMMR1 = 7000;

PWMLER = (1<<1);

}

else if( !((IOPIN0) & (1<<3)) ) // Check P0.3

{

PWMMR1 = 10000;

PWMLER = (1<<1);

}

else if( !((IOPIN0) & (1<<4)) ) // Check P0.4

{

PWMMR1 = 15000;

PWMLER = (1<<1);

}

}

}

You might also like

- PWM RegistersDocument14 pagesPWM RegistersAshok KumarNo ratings yet

- LPC2148 PWM Programming GuideDocument14 pagesLPC2148 PWM Programming GuideVinothkumar UrumanNo ratings yet

- RC Servo Motor Control Using LPC2148 MicrocontrollerDocument12 pagesRC Servo Motor Control Using LPC2148 Microcontrollersameer khanNo ratings yet

- 06 Nutiny-Nuc029 PWMDocument25 pages06 Nutiny-Nuc029 PWMDharmendra SavaliyaNo ratings yet

- MCES - 18CS44 - Unit4 PWM - DCMotorDocument9 pagesMCES - 18CS44 - Unit4 PWM - DCMotorSAKSHAM PRASADNo ratings yet

- PWM Atmega328Document30 pagesPWM Atmega328JUNIOR700No ratings yet

- PWM On The ATmega328Document10 pagesPWM On The ATmega328dardosordiNo ratings yet

- Atmel Avr Atmega48 PWMDocument9 pagesAtmel Avr Atmega48 PWMAlfred J. NgunyiNo ratings yet

- Dspic30F6010 Motor Control PWMDocument34 pagesDspic30F6010 Motor Control PWMSourabh KhandelwalNo ratings yet

- Sine Wave GeneratorDocument12 pagesSine Wave GeneratorkjfensNo ratings yet

- PWMDocument17 pagesPWMmaintboardNo ratings yet

- Secrets of Arduino PWMDocument20 pagesSecrets of Arduino PWMDany Setyawan100% (1)

- Os Segredos Do PWM Do ArduinoDocument6 pagesOs Segredos Do PWM Do ArduinoFernando EsquírioNo ratings yet

- PWMC - Pulse Width Modulation ControllerDocument19 pagesPWMC - Pulse Width Modulation ControllerRaman GuptaNo ratings yet

- Secrets of Arduino PWMDocument8 pagesSecrets of Arduino PWMpcrmengeNo ratings yet

- PWM Motor ControllerDocument44 pagesPWM Motor ControllerTrương Tuấn VũNo ratings yet

- LED Brightness Control Using PWM of LPC2138: ESD Lab Mini-ProjectDocument8 pagesLED Brightness Control Using PWM of LPC2138: ESD Lab Mini-ProjectAditya GadgilNo ratings yet

- HBridgeMotorControl With PICDocument11 pagesHBridgeMotorControl With PICcoceicr100% (3)

- Atmega16: Square Wave GenerationDocument3 pagesAtmega16: Square Wave Generationshahbazalam4a5No ratings yet

- Book PIC Microcontrollers-Chapter 5 CCP ModulesDocument17 pagesBook PIC Microcontrollers-Chapter 5 CCP ModulesHammamiSalah100% (1)

- 3 Power LED Dimmer Using ATmega32 MicrocontrollerDocument5 pages3 Power LED Dimmer Using ATmega32 MicrocontrollerAmiruddinNo ratings yet

- Microcontroller Based Sinusoidal PWM Inverter For Photovoltaic ApplicationDocument4 pagesMicrocontroller Based Sinusoidal PWM Inverter For Photovoltaic ApplicationDumitrescu Camil SorinNo ratings yet

- PWM With Microcontroller 8051 For SCR or Triac Power ControlDocument8 pagesPWM With Microcontroller 8051 For SCR or Triac Power ControlSyedMahinNo ratings yet

- CCP PWMDocument19 pagesCCP PWMalaa_saq100% (1)

- Timer Counter AVRDocument105 pagesTimer Counter AVRفايزميلي الأبد100% (1)

- Sine Wave GeneratorDocument12 pagesSine Wave GeneratortranvandoanhNo ratings yet

- Safari - 13 Mai 2023 À 09:40Document1 pageSafari - 13 Mai 2023 À 09:40Paréto BessanhNo ratings yet

- 08 - NuMicro PWMDocument20 pages08 - NuMicro PWMThienNo ratings yet

- PWM DAN TIMERDocument54 pagesPWM DAN TIMERmasrinaNo ratings yet

- Sine Wave Generation and Implementation Using dsPIC33FJDocument27 pagesSine Wave Generation and Implementation Using dsPIC33FJTahmid100% (10)

- AVR_Timers0Document32 pagesAVR_Timers0Muhammad ejaz RamzanNo ratings yet

- PWM Using 8 0 5 1 A N D P I C: BY Balaji K S Sai Kishore P GDocument16 pagesPWM Using 8 0 5 1 A N D P I C: BY Balaji K S Sai Kishore P GPoonthalirNo ratings yet

- Control DC Motor Speed using STM32 PWMDocument4 pagesControl DC Motor Speed using STM32 PWMJohn FarandisNo ratings yet

- Ds PICDocument3 pagesDs PICSharad Chandra SharamaNo ratings yet

- PIC (PWM PGM Steps)Document20 pagesPIC (PWM PGM Steps)Elena Gilbert100% (2)

- 16-B PWM U O - C T Relevant Devices: IT Sing AN N HIP ImerDocument12 pages16-B PWM U O - C T Relevant Devices: IT Sing AN N HIP ImerLauderi MartinsNo ratings yet

- Fast PWMDocument3 pagesFast PWMAlexis FernandoNo ratings yet

- ATMPWMDocument6 pagesATMPWMOkiPetrus Hutauruk LumbanBaringinNo ratings yet

- PWM in Avr: Developed byDocument10 pagesPWM in Avr: Developed byParth Sarthi SharmaNo ratings yet

- Timers and PWM on PIC MicrocontrollersDocument38 pagesTimers and PWM on PIC MicrocontrollersThanh LeNo ratings yet

- ELEC 3040/3050 Lab #7: PWM Waveform GenerationDocument22 pagesELEC 3040/3050 Lab #7: PWM Waveform GenerationBrandon2017No ratings yet

- Sine Wave Generation and Implementation Using DsPIC33FJDocument27 pagesSine Wave Generation and Implementation Using DsPIC33FJpaaraib100% (1)

- PWM Atmega8Document8 pagesPWM Atmega8mostafa_s37893No ratings yet

- LPCTimer and PWM OperationsDocument38 pagesLPCTimer and PWM OperationsNikhil SinghNo ratings yet

- PWM Implementation GuideDocument31 pagesPWM Implementation GuideZesi Villamor Delos SantosNo ratings yet

- Infineon-Component - PSoC - 4 - Timer - Counter - and - PWM - V1.10-Software Module Datasheets-V02 - 01-ENDocument42 pagesInfineon-Component - PSoC - 4 - Timer - Counter - and - PWM - V1.10-Software Module Datasheets-V02 - 01-ENFatenn BellakhdharNo ratings yet

- Fast PWM Mode. DC Motor. Servo MotorDocument21 pagesFast PWM Mode. DC Motor. Servo MotorAya Adel Gouma AbdElGaidNo ratings yet

- PWM - 51Document12 pagesPWM - 51Nong Suriya100% (1)

- PIC18F4550 PWM - PIC ControllersDocument7 pagesPIC18F4550 PWM - PIC ControllersKrishanu Modak100% (2)

- TOPIC 5 - PWMDocument23 pagesTOPIC 5 - PWMMuhammad WaqiuddinNo ratings yet

- On-Chip PeripheralsDocument73 pagesOn-Chip PeripheralsR R DeshmukhNo ratings yet

- Controlling Servo Motors With AVR MicrocontrollersDocument4 pagesControlling Servo Motors With AVR MicrocontrollersAri Kurniawan S100% (2)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 110 Waveform Generator Projects for the Home ConstructorFrom Everand110 Waveform Generator Projects for the Home ConstructorRating: 4 out of 5 stars4/5 (1)

- LPC2148 DacDocument14 pagesLPC2148 DacSmruti Pore100% (1)

- RTCDocument10 pagesRTCAkshay FarakateNo ratings yet

- UART Interfacing With ARM PrimerDocument13 pagesUART Interfacing With ARM PrimerSmruti PoreNo ratings yet

- lpc2148 TimersDocument11 pageslpc2148 TimersSmruti PoreNo ratings yet

- A Spice Model For The Ideal TransformerDocument2 pagesA Spice Model For The Ideal TransformerCristian LiviuNo ratings yet

- Chapter 2.1 CoaDocument5 pagesChapter 2.1 CoaSamuel AdamuNo ratings yet

- Introduction To VLSI DesignDocument33 pagesIntroduction To VLSI DesignAnonymous P9xMOgEYt1No ratings yet

- PCM ProjectDocument7 pagesPCM Projectsuresh NamgiriNo ratings yet

- Wireless World 1971 09Document54 pagesWireless World 1971 09jacomartNo ratings yet

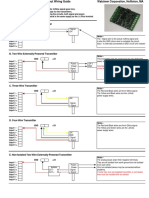

- 4-20ma Input WiringDocument2 pages4-20ma Input WiringAnurag Gupta100% (1)

- 2-input gates using 2_1 muxDocument8 pages2-input gates using 2_1 muxvarun186No ratings yet

- Solved Find Vo in Fig E824 Using Thevenin's Theoremfigure E CheggcomDocument10 pagesSolved Find Vo in Fig E824 Using Thevenin's Theoremfigure E Cheggcom20280110No ratings yet

- DM74LS90/DM74LS93 Decade and Binary Counters: General DescriptionDocument10 pagesDM74LS90/DM74LS93 Decade and Binary Counters: General DescriptionThế giới điện tửNo ratings yet

- DOD Gonkulator How It Works OriginalDocument1 pageDOD Gonkulator How It Works OriginaltttymonNo ratings yet

- Lecture 4 PDFDocument17 pagesLecture 4 PDFsajjadNo ratings yet

- IL300 Appn50Document19 pagesIL300 Appn50Shirish Bhagwat100% (1)

- Octal 3-State Noninverting D Flip-Flop: KK74HC574ADocument6 pagesOctal 3-State Noninverting D Flip-Flop: KK74HC574Ajksb100No ratings yet

- Joshi Thesis 2016Document94 pagesJoshi Thesis 2016Phạm Đức ThuậnNo ratings yet

- PIC32MX470 Family Datasheet - 60001185GDocument364 pagesPIC32MX470 Family Datasheet - 60001185GJuan PachonNo ratings yet

- CO2037 - L03b - OpAmpDocument36 pagesCO2037 - L03b - OpAmpHào NguyễnNo ratings yet

- AC Voltage Measurement Using Arduino - Circuits4you PDFDocument4 pagesAC Voltage Measurement Using Arduino - Circuits4you PDFJesus HuitronNo ratings yet

- Digital Logic RTL & Verilog Interview Questions PreviewDocument34 pagesDigital Logic RTL & Verilog Interview Questions Previewkoushikroopa hk71% (7)

- DPD Release NotesDocument3 pagesDPD Release Notestomasz bartnikNo ratings yet

- Renesas Technology Corp. announces name change from Mitsubishi brandsDocument10 pagesRenesas Technology Corp. announces name change from Mitsubishi brandsTahar BenacherineNo ratings yet

- IcpinoutDocument3 pagesIcpinouthakyNo ratings yet

- EE352L Experiment N# 1 Objectives: 1.1 Pre-LabDocument3 pagesEE352L Experiment N# 1 Objectives: 1.1 Pre-LabYassine DjillaliNo ratings yet

- Analog Electronic Circuit: Prof. Shouribrata ChatterjeeDocument1 pageAnalog Electronic Circuit: Prof. Shouribrata ChatterjeechadNo ratings yet

- Electronics Lab IIDocument3 pagesElectronics Lab IIVikram RaoNo ratings yet

- Digital System DesignDocument10 pagesDigital System DesignGourav VashistNo ratings yet

- Logic Gates, Boolean Algebra and Simplification FormulasDocument26 pagesLogic Gates, Boolean Algebra and Simplification FormulasErnesto AntonioNo ratings yet

- 7400 Nand GatesDocument4 pages7400 Nand Gatessrc e-solutionsNo ratings yet

- Amplifier Design: Bilateral Design of Amplifier With Conjugately Matched (Design For Maximum Gain)Document12 pagesAmplifier Design: Bilateral Design of Amplifier With Conjugately Matched (Design For Maximum Gain)jascnjNo ratings yet