Professional Documents

Culture Documents

Dynamatic Tutorial: Exercise Instructions Summary

Uploaded by

Srijeet GuhaOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Dynamatic Tutorial: Exercise Instructions Summary

Uploaded by

Srijeet GuhaCopyright:

Available Formats

Dynamatic Tutorial: Exercise Instructions

Exercises 1, 2, and 3: Using Dynamatic

This part of the Dynamatic tutorial contains three exercises which illustrate the basic features and usage of Dyna-

matic on a toy example. The exercises are located in the following folders:

– Exercise 1: tutorial/1-example-naive

– Exercise 2: tutorial/2-example-buffers

– Exercise 3: tutorial/3-example-lsq

For all three exercises, follow the five steps below. Each exercise has additional questions in the following section.

1) Open a terminal and set the appropriate exercise folder as the working directory. For Exercise 1:

cd tutorial/1-example-naive

2) Consider the code in src/example.cpp and the Dynamatic commands in synthesis.tcl. Use this script to

synthesize the example function into a dataflow circuit:

dynamatic synthesis.tcl

3) Study the DOT, PNG, and VHDL outputs of Dynamatic in folders reports and hdl.

4) Simulate the design using ModelSim:

vsim -do simulation.tcl

Study the waveforms and note the total execution time. Refer to the next page for tips on using ModelSim.

5) Check the correctness of the circuit by comparing the simulation results with the software results:

meld sim/C OUT/output a.dat sim/VHDL OUT/output a.dat

For details on the compiler commands and the output files, please refer to the Dynamatic tutorial paper.

Exercises 1, 2, and 3: Additional Questions

Exercise 1*. All questions refer to the outputs of Exercise 1 in tutorial/1-example-naive.

a) In example.png, consider the buffer buffI 0. In the waveform, find the input and output signals of this

buffer. What do the values stored in this buffer (i.e., values of buffI 0 dataOutArray 0) correspond to? Find

a point in the simulation when the buffer is stalled by its successor (i.e., signal buffI 0 nReadyArray 0 is set

to zero while the buffer produces valid data and buffI 0 validArray 0 is set to 1).

b) In example.png, consider component icmp 15. Find a point in the simulation where the loop condition (i.e.,

i < 100) evaluates to false (i.e., icmp 15 dataOutArray 0 returns from value 1 to value 0).

c) In example.png, consider component branch 1. In the simulation, investigate how the change of the condi-

tion value from true to false affects the validity of the Branch outputs (i.e., signals branch 1 validArray 0

and branch 1 validArray 1).

Exercise 2*. All questions refer to the outputs of Exercise 2 in tutorial/2-example-buffers.

a) In example optimized.png, find all buffers and investigate their size and transparency (values provided

in squared brackets for each buffer; for instance, Buffer 1[2] indicates a 2-slot nontransparent buffer and

Buffer 2[2t] indicates a 2-slot transparent buffer).

b) In example optimized.png, consider the buffer Buffer 1. In the waveform, find the input and output

signals of this buffer. Check if, at any point in the simulation, the buffer is stalled by its successor (i.e., signal

Buffer 1 nReadyArray 0 is set to zero while the buffer produces valid data and Buffer 1 validArray 0

is set to 1).

c) In the simulation, locate the read-after-write hazard between loop iterations 4 and 5. The load of iteration 5

occurs at 42 ns and the store of iteration 4 at 58 ns. The read and write address are named a address1 and

a address0, respectively.

Exercise 3*. All questions refer to the outputs of Exercise 3 in tutorial/3-example-lsq.

a) In example optimized.png, locate the new LSQ component and study its inputs and outputs. Note that only

the load (load 7) and store (store 0) to array a are connected to the LSQ, whereas the other loads connect to

separate memories.

b) Check if the read-after-write dependency between iterations 4 and 5 is honoured. The load receives the read

data (signal load 7 dataInArray 0) of iteration 5 at 82 ns. The store writes the data of iteration 4 to memory

at 74 ns. Write address and data are named a address0 and a dout0, respectively.

1

7

4 2

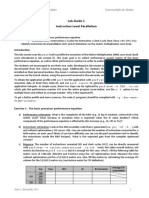

Figure 1: ModelSim.

Exercise 4: Modifying the Dynamatic Flow

This part of the tutorial illustrates some possibilities for modifying the Dynamatic flow (i.e., integrating new VHDL

components and changing the intermediate representation). All questions refer to the files in tutorial/4-example-mul.

a) Synthesize and simulate example mul.cpp as in the previous exercises. Note the simulation execution time.

b) In hdl/mul wrapper.vhd, replace the 4-stage multiplier with an 8-stage multiplier by changing the multiplier

entity from work.mul 4 stage to work.mul 8 stage. In the same file, change the LATENCY constant to

reflect the component latency change. Simulate the design and compare the execution time to the prior one.

c) Integrate the information about the new multiplier into the Dynamatic flow:

– Invoke the Dynamatic shell using the command dynamatic and type manually the commands from

synthesis.tcl to set up the project and synthesize the design (i.e., all commands up to optimize).

– Before invoking the optimize command, in reports/example mul.dot, update the latency field of mul-

tiplier mul 8 to reflect the latency change.

– Run the remaining commands from synthesis.tcl to place buffers and produce the VHDL netlist.

– Repeat the steps from question 4b to replace the multiplier in hdl/mul wrapper.vhd.

Simulate the design, note the total execution time, and compare it from the one from the previous questions.

Using ModelSim

To complete the exercises, use the ModelSim features described in this section and depicted in Figure 1.

– After running the simulation.tcl script, wait for the simulation to complete; a green text line will appear

in the Transcript window (marked with number 1 in the figure), indicating simulation break.

– Extend the waveform across the entire screen by clicking on the undock button (number 2).

– To change the number format of a signal from binary to unsigned, right-click on the signal name (e.g., number

3) and choose Radix > Unsigned.

– Zoom in/out of the waveforms using the zoom in/out buttons (number 4).

– Scroll through simulation time using the horizontal bar (number 5) and through signals using the vertical bar

(number 6).

– Search for a signal by name using the find button (number 7).

You might also like

- Programming with MATLAB: Taken From the Book "MATLAB for Beginners: A Gentle Approach"From EverandProgramming with MATLAB: Taken From the Book "MATLAB for Beginners: A Gentle Approach"Rating: 4.5 out of 5 stars4.5/5 (3)

- Q400 Presentation - PowerplantDocument44 pagesQ400 Presentation - PowerplantTom100% (6)

- Abinitio Intvw QuestionsDocument20 pagesAbinitio Intvw Questionsayon hazra100% (1)

- 1 ResSimCh3Document30 pages1 ResSimCh3weldsv1No ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- Setting Up A Reservoir Simulation ModelDocument30 pagesSetting Up A Reservoir Simulation ModelMariam Tatty LeonNo ratings yet

- C & C++ Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesFrom EverandC & C++ Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesNo ratings yet

- Thinking ArchitecturallyDocument68 pagesThinking ArchitecturallyJose RojasNo ratings yet

- Huawei LTE CountersDocument14 pagesHuawei LTE CountersRocky33% (3)

- HANS - Udyam Registration CertificateDocument2 pagesHANS - Udyam Registration Certificateshivi mishraNo ratings yet

- Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastiDocument11 pagesSolution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastitargetiesNo ratings yet

- Connecting Matlab With OpenFOAM JPDocument17 pagesConnecting Matlab With OpenFOAM JPSomdeb BandopadhyayNo ratings yet

- Lab 2Document4 pagesLab 2geoaamer100% (1)

- 5th Sem ADA ManualDocument41 pages5th Sem ADA ManualManjunath GmNo ratings yet

- MATLAB Structure and Use: 1.1 Pre-Lab AssignmentDocument29 pagesMATLAB Structure and Use: 1.1 Pre-Lab AssignmentYu YangNo ratings yet

- CS 349, Summer 2015 Optimizing The Performance of A Pipelined Processor Assigned: June 6, Due: June 21, 11:59PMDocument12 pagesCS 349, Summer 2015 Optimizing The Performance of A Pipelined Processor Assigned: June 6, Due: June 21, 11:59PMBen SmithNo ratings yet

- Lab4 MultipleLinearRegressionDocument7 pagesLab4 MultipleLinearRegressionJason ThiamNo ratings yet

- Introduction to MOA Massive Online AnalysisDocument10 pagesIntroduction to MOA Massive Online AnalysisusernameusernaNo ratings yet

- System Modeler Getting Started Modelica Aspects Modeling Advice PDFDocument10 pagesSystem Modeler Getting Started Modelica Aspects Modeling Advice PDFindebtanup2443No ratings yet

- Lab 1 Spring 13Document3 pagesLab 1 Spring 13Kumaraguru RauNo ratings yet

- 2013 Lab MatlabSimulinkDocument9 pages2013 Lab MatlabSimulinkwilldota100% (1)

- Scilab Recipe 3 - Xcos Blocks Seasoning - Scilab NinjaDocument8 pagesScilab Recipe 3 - Xcos Blocks Seasoning - Scilab NinjaWendell Kim LlanetaNo ratings yet

- Introduction to Scilab for Control System SimulationDocument10 pagesIntroduction to Scilab for Control System SimulationJohaira MauteNo ratings yet

- CS 475/675 Machine Learning: Homework 3 VisualizationsDocument8 pagesCS 475/675 Machine Learning: Homework 3 VisualizationsAli ZainNo ratings yet

- Arch LabDocument12 pagesArch LabDavid Cho0% (1)

- Lab Description - Keil ToolsDocument21 pagesLab Description - Keil ToolsGnurt NeyugnNo ratings yet

- MC OpenmpDocument10 pagesMC OpenmpBui Khoa Nguyen DangNo ratings yet

- The Opensees Examples PrimerDocument46 pagesThe Opensees Examples PrimerMahmoud Elkhedr100% (1)

- Lab3 PDFDocument6 pagesLab3 PDFSELVAKUMAR RBNo ratings yet

- MIT6 189IAP11 hw2Document8 pagesMIT6 189IAP11 hw2Ali AkhavanNo ratings yet

- Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFDocument5 pagesSolution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFtargeties0% (1)

- ML Coursera Python AssignmentsDocument20 pagesML Coursera Python AssignmentsMNo ratings yet

- Lab 2Document6 pagesLab 2Iskandar HambaAllahNo ratings yet

- Using Simulink To Perform Open-Loop SimulationsDocument4 pagesUsing Simulink To Perform Open-Loop SimulationsMansour AbdulazizNo ratings yet

- ECLIPSE Blackoil User Course ExercisesDocument14 pagesECLIPSE Blackoil User Course ExerciseszemabderNo ratings yet

- Toaz - Info Control Systems Lab 1 PRDocument8 pagesToaz - Info Control Systems Lab 1 PRrhydnar KimNo ratings yet

- Lab 2: Brief Tutorial On Openmp Programming Model: Adrián Álvarez, Sergi Gil Par4207 2019/2020Document11 pagesLab 2: Brief Tutorial On Openmp Programming Model: Adrián Álvarez, Sergi Gil Par4207 2019/2020Adrián AlvarezNo ratings yet

- CS 201, Spring 2021: Homework Assignment 2Document4 pagesCS 201, Spring 2021: Homework Assignment 2Arda Barış ÖrtlekNo ratings yet

- Su 2011 Final SolDocument19 pagesSu 2011 Final SolmissionchocolateNo ratings yet

- ENGR6012 Assignment #1: Mechanical Vibrations and Condition MonitoringDocument8 pagesENGR6012 Assignment #1: Mechanical Vibrations and Condition MonitoringUsama MughalNo ratings yet

- Full Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFDocument18 pagesFull Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipasti PDFtargetiesNo ratings yet

- Updated Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastiDocument8 pagesUpdated Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastitargetiesNo ratings yet

- Full Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. LipastiDocument27 pagesFull Solution Manual For Modern Processor Design by John Paul Shen and Mikko H. Lipastitargeties50% (2)

- Lab Guide 1: Instruction Level Parallelism and Matrix MultiplicationDocument3 pagesLab Guide 1: Instruction Level Parallelism and Matrix MultiplicationJoão LourençoNo ratings yet

- Astrophysics Lab Work - Computational Basics: Exercise 1 - Files and DirectoriesDocument5 pagesAstrophysics Lab Work - Computational Basics: Exercise 1 - Files and DirectoriesB RaoNo ratings yet

- Four-Tank Plant Benchmark Distributed MPCDocument7 pagesFour-Tank Plant Benchmark Distributed MPCmail2saravanancNo ratings yet

- Ece4750 Lab1 ImulDocument7 pagesEce4750 Lab1 ImulThuy NguyenNo ratings yet

- L2 Modeling and Simulation of Motor Speed BMMP 2343Document6 pagesL2 Modeling and Simulation of Motor Speed BMMP 2343Lk BanNo ratings yet

- Matlab Chapter 2Document16 pagesMatlab Chapter 2Chathura Priyankara WijayarathnaNo ratings yet

- Cs4/Msc Parallel Architectures Practical 2 - Cache Coherence ProtocolsDocument5 pagesCs4/Msc Parallel Architectures Practical 2 - Cache Coherence Protocolsbobby123450No ratings yet

- The Essential BYOM ManualDocument18 pagesThe Essential BYOM ManualDavor ProfesorNo ratings yet

- HW4: Merge Sort: 1 Assignment GoalDocument6 pagesHW4: Merge Sort: 1 Assignment GoalRafael MendoncaNo ratings yet

- Spring 2018 Lab Assignment #4: Understanding Cache Memories Assigned: Apr. 25 Deadline: May 9, 04:59:59 PMDocument10 pagesSpring 2018 Lab Assignment #4: Understanding Cache Memories Assigned: Apr. 25 Deadline: May 9, 04:59:59 PMSohaib ChoudharyNo ratings yet

- Chapter 5 - CO - BIM - IIIDocument7 pagesChapter 5 - CO - BIM - IIIAnkit ShresthaNo ratings yet

- Lab: Title: Lab Objectives:: Type Function - Name (Optional Parameter List) (Function Code Return Value )Document8 pagesLab: Title: Lab Objectives:: Type Function - Name (Optional Parameter List) (Function Code Return Value )elshaday desalegnNo ratings yet

- Finn Haugen, TechTeach - Introduction To LabVIEW Simulation ModuleDocument12 pagesFinn Haugen, TechTeach - Introduction To LabVIEW Simulation Moduleeeindustrial100% (1)

- Lab ManualDocument15 pagesLab Manualgideontargrave7100% (1)

- PID Control Experiment: Mechanical Engineering LabDocument4 pagesPID Control Experiment: Mechanical Engineering LabFreddy A. SanchezNo ratings yet

- CitectSCADA Assignment 2Document24 pagesCitectSCADA Assignment 2AshikaNo ratings yet

- Introduction to MATLAB for Signal PlottingDocument8 pagesIntroduction to MATLAB for Signal PlottingRadu NiculaeNo ratings yet

- Cache LabDocument10 pagesCache Labarteepu37022No ratings yet

- Cadence Tutorial 4Document14 pagesCadence Tutorial 4bk249No ratings yet

- Experimentation Documentation PDFDocument8 pagesExperimentation Documentation PDFSrijeet GuhaNo ratings yet

- Routing Inside Pblock - OdtDocument3 pagesRouting Inside Pblock - OdtSrijeet GuhaNo ratings yet

- Dynamatic (4) OdtDocument4 pagesDynamatic (4) OdtSrijeet GuhaNo ratings yet

- FPT19 TimingModel 1Document8 pagesFPT19 TimingModel 1Srijeet GuhaNo ratings yet

- RapidWright Tutorials (3) .OdtDocument17 pagesRapidWright Tutorials (3) .OdtSrijeet GuhaNo ratings yet

- Silcostart: Static Motor Softstarter Solving Starting ProblemsDocument4 pagesSilcostart: Static Motor Softstarter Solving Starting ProblemsMohamed AlkharashyNo ratings yet

- AWS Solution Architect-Associate (AWSSA-C002) : IntroductionDocument2 pagesAWS Solution Architect-Associate (AWSSA-C002) : IntroductionIsmail SayyedNo ratings yet

- A Corona Ring Is A Conducting Ring Mounted On The End of or RadiallyDocument6 pagesA Corona Ring Is A Conducting Ring Mounted On The End of or RadiallygopalNo ratings yet

- Arco en C Siemens Polymobil 3 MS EngDocument34 pagesArco en C Siemens Polymobil 3 MS EngAzucena RivasNo ratings yet

- GSMDocument119 pagesGSMAlas Mallari DonatoNo ratings yet

- H 264/avcDocument23 pagesH 264/avcdkchqmpNo ratings yet

- C-Arrays & Strings and FunctionsDocument33 pagesC-Arrays & Strings and FunctionsSambhaviNo ratings yet

- Infomark: Cut Part Identification SystemDocument2 pagesInfomark: Cut Part Identification SystemTommy LeeNo ratings yet

- Lifts 150324053755 Conversion Gate01 PDFDocument43 pagesLifts 150324053755 Conversion Gate01 PDFAjay JainNo ratings yet

- EZET ACADEMY ROUTE TO PROFESSIONAL ENGINEER (Ir.) DEVELOPMENT PACKAGEDocument8 pagesEZET ACADEMY ROUTE TO PROFESSIONAL ENGINEER (Ir.) DEVELOPMENT PACKAGEkesavan1990No ratings yet

- FSMODocument3 pagesFSMOsivadashxyz8066No ratings yet

- Huawei CloudEngine S5731-H Series Switches BrochureDocument13 pagesHuawei CloudEngine S5731-H Series Switches BrochureMurillo SilvaNo ratings yet

- IBM Decision Optimization For IBM Cloud Pak For Data v3Document32 pagesIBM Decision Optimization For IBM Cloud Pak For Data v3Antonio BlancoNo ratings yet

- Turbine Design SKODA MTD10-30Document13 pagesTurbine Design SKODA MTD10-30Rajnish SrivastavaNo ratings yet

- Curriculum Vitae: Personal InformationDocument2 pagesCurriculum Vitae: Personal InformationAnonymous 2HxqQVNo ratings yet

- Context DrivenDocument18 pagesContext DrivenRajib BoseNo ratings yet

- Critical and Cultural Theories of Mass Communication Challenges To Minimal Effects Theory-PPT-61Document61 pagesCritical and Cultural Theories of Mass Communication Challenges To Minimal Effects Theory-PPT-61Keith Knight100% (1)

- Tutorial 1 - Exploring Arcgis: ObjectivesDocument11 pagesTutorial 1 - Exploring Arcgis: ObjectivesMoses KaswaNo ratings yet

- Lycoming Engine Order Form: (If Different)Document2 pagesLycoming Engine Order Form: (If Different)Michel LefebvreNo ratings yet

- Automatic Weather StationDocument8 pagesAutomatic Weather StationMyat Tun OoNo ratings yet

- Backup RelayDocument3 pagesBackup RelayTinashe MupayaNo ratings yet

- Pycharm TutorialDocument9 pagesPycharm Tutorialrashed44No ratings yet

- Digilocker VacDocument5 pagesDigilocker Vacanshikasgh3012No ratings yet

- CiscoDocument4 pagesCiscoMaryam ZafarNo ratings yet

- A Process Story in Firozabad ClusterDocument257 pagesA Process Story in Firozabad ClustersudshkNo ratings yet

- Supor Operation Manual Suporssv1 1b E 131207Document163 pagesSupor Operation Manual Suporssv1 1b E 131207raschid alberto palacios lopezNo ratings yet