Professional Documents

Culture Documents

Introduction To Vivado

Introduction To Vivado

Uploaded by

Koush RastogiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Introduction To Vivado

Introduction To Vivado

Uploaded by

Koush RastogiCopyright:

Available Formats

Introduction to AMD Vivado™

AMD Tools and Frameworks

AMD Vitis™ AI AMD Vitis™ Petalinux

Enables the implementations of Embedded and accelerated SW Embedded Linux solutions

machine learning inference, using development. Used to develop

Tensor Flow, Caffe and PyTorch software solutions for

MicroBlaze™, Arm® R5, A9, A53

*Requires a SoC/RFSoC/AMD Alveo™ and A72.

PYNQ AMD Vitis™ / Vivado HLS AMD Vivado™

Python framework for rapid High-Level Synthesis (HLS) tool Design capture and

prototyping on SoC/RFSoC/Alveo supporting C/C++/OpenCL implementation for the base

platform

© Adiuvo Engineering and Training, Ltd. 2020 2

AMD Vivado™ Overview

• Vivado is the foundation of all design

and higher level tools

• Vivado enables us to capture ✓ Simulate designs using

designs using VHDL or Verilog Vivado Simulator

✓ Synthesize, place and

• Large IP library to accelerate our route the design

designs ✓ Generate power

estimations

• Integrates Vivado / Vitis HLS IP

✓ Create AMD support

cores architecture

© Adiuvo Engineering and Training, Ltd. 2020

AMD Vivado™ Overview

FPGA Implementation Flow

Synthesis – Translates the HDL design into a series of logic equations

which are then mapped onto the resources available in the target FPGA.

Place – The logic resources determined by the synthesis tool are placed at We can control the flow

available locations within the target device.

implementation settings

by using constraints (XDC

file) and implementation

Routing – The placed logic resources in the design are interconnected strategies.

using routing and switch matrixes to implement the final application.

Bit File – The generation of the final programming file for the target FPGA.

© Adiuvo Engineering and Training, Ltd. 2020

AMD Vivado™ IP Integrator

AMD Vivado™ IP Integrator (IPI)

Create system-level designs

• Instantiate and interconnect IP cores

• IP-centric design flow

• Plug-and-play IP

• Vast IP catalog

• Accelerates

• Integration

• Productivity

• Example applications

• Embedded

• DSP

• Video

• Analog

• Networking

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ IP Integrator:

Intelligent IP Integration

• Automated IP subsystems

• Block automation for rapid design creation Hierarchy

Support

• One click IP customization System Hierarchy

View

Interface Connections with

• Board aware Live DRCs

• Support all 7 Series FPGAs and AMD Tcl Console

Zynq™ SoCs

Extensible IP Catalog

• Built-in presets, accelerating design

creation

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ IP Integrator:

Intelligent IP Integration

Correct-by-construction

• Interface level connections

• Extensible IP repository

• Real-time DRCs and parameter

propagation / resolution

• Designer assistance

© Adiuvo Engineering and Training, Ltd. 2023

Demonstration

AMD Vivado™

Clock Domain Crossing

Clock Domain Crossing

Ideal solution uses one clock and the entire design is synchronous.

BUT!

Modern devices have multiple clocks to address different clock domains e.g.

ADC / DAC clocks, source synchronous interfaces.

Brings with it the need to transfer data, and signals safely and reliability

between the clock domains.

11 © Adiuvo Engineering and Training, Ltd. 2023

Metastability

One issue which can arise with incorrect domain crossing is metastability.

This can lead to corruption of data or incorrect behaviour.

Occurs when a flip flops set up or hold time is violated.

12 © Adiuvo Engineering and Training, Ltd. 2023

Metastability

13 © Adiuvo Engineering and Training, Ltd. 2023

Clock Domain Crossing

Several techniques can be used depending upon what needs to be transferred:

• Two stage synchroniser – Ideal for single bit data

• Grey code synchroniser – Encodes data bus in grey code and transfer between domains

– Ideal for counters as input to be converted to grey code can only decrement /

increment by one from previous value

• Hand shake synchroniser – Transfers data bus between two clock domains using

handshake signals

• Pulse synchroniser – transfer pulse from one clock domain to another

• Asynchronous FIFO – transfers data from one domain to another, useful for high

throughput / burst transfers

14 © Adiuvo Engineering and Training, Ltd. 2023

Clock Domain Crossing

To support reset functionality across clock domains we may need the

following synchronisers structures.

» Asynchronous Reset Synchroniser – enables asynchronous assertion and

synchronous de-assertion.

» Synchronous Reset Synchroniser – synchronises a synchronous reset to another

clock domain.

15 © Adiuvo Engineering and Training, Ltd. 2023

CDC in AMD

AMD Parameterised Macros (XPM) – provide CDC structures

Use registers optimised for CDC in the fabric

» Registers located close together and have small set up and hold windows

Described within UG953 Libraries Guide

Described within UG 974 UltraScale™ Architecture Libraries

16 © Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ CDC Report

Following Synthesis – in TCL window run the command report_cdc

Page 17 © Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ Timing Analysis – Clock Interaction

Generated from Flow Navigator when implementation is

open.

Yellow show unrelated clock – Indicates CDC issues as well.

(Means we need to define constraints.)

Page 18 © Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ Timing Analysis – Inter clock Issues

Detailed path report – Source and Destination Clocks different

If you forget to report_cdc

following synthesis. CDC issues

will be apparent in the timing

report if we have not correctly

addressed the constraints.

Page 19 © Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ Flow - Schematic

Engineers can use

information

provided in the text

report to navigate

to the schematic to

understand where

CDC might be.

Page 20 © Adiuvo Engineering and Training, Ltd. 2023

Strategies and Reports

AMD Vivado™ – Strategies

• Strategies are a defined set of Vivado implementation feature options that control the implementation

results.

• These strategies can be used to explore:

• Timing Performance (e.g., Performance_Explore)

• Congestion - Strategies to reduce routing congestion in areas of the design

• Area - Optimize for area

• Power – Optimize for power

• Quick Flow – Reduced implementation time

We should always try to achieve timing closure.

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ – Reports

• Vivado provides several reports which can be used to help focus in on performance

issues in the design:

• Design Analysis Report – Provides information on design timing, congestion, and

complexity of design.

• Quality of Result Report – Provides overall design assessment and methodology

check – QOR can also make suggestions to fix issues in the design.

• Both are very useful to achieve timing closure of the design.

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ – Design Analysis Report

Design Analysis Report provides information on:

• Timing – Provides information on the timing and

physical characteristics of timing paths.

• Complexity – Provides information on routing

complexity and LUT distribution.

• Congestion – Provides information on routing

congestion.

No need to run full implementation.

Generate report after running opt_design

command in TCL.

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ – Design Analysis Report

• Along with timing information, DAR can provide information on design complexity

including indicating design risk for implementation.

• Low Risk Rent Analysis <0.65 and Fan Out <4.

• High Risk Rent Analysis >0.65 <0.85 and Fan Out >4 % <5 – May be difficult to place

without congestion.

• Very High Risk, Rent Analysis >0.85 and Fan Out >5 – May not implement

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ – Quality of Result

• Quality of Result Assessment (QoRA) and Quality of Result Suggestions

(QoRS) since both provide information that can be used to achieve timing

closure.

• Like Design Analysis Report – Run initially after doing the Opt.

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ – Quality of Results

SCORE MEANING CORRECTIVE ACTION

1 Design will not implement Redesign RTL / HLS modules

2 Design will implement timing Review constraints & RTL HLS

problems

3 Design Runs have a small Use QoR suggestions, review

chance of success clocking, ML strategies

4 Design should meet timing if Use QoR suggestions, ML

directives used strategies

5 Design will implement without Run Implementation

timing issues

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ – Quality of Results

© Adiuvo Engineering and Training, Ltd. 2023

Reducing Run Time

Design Check Points

• AMD Vivado™ uses a physical design

database to store placement and routing

information.

• Design checkpoint files (.dcp) allow you to

save and restore this physical database at key

points in the design flow.

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ – Reducing Compile Time

• Implementing a FPGA design can take a considerable time > 1 Hour.

• Iterating the design can therefore be an issue, there are several options which can

reduce the implementation time both in synthesis and place and route.

Synthesis

Global Performs a traditional top-down synthesis of the entire design. Selecting this

option takes the longest time because you need to re-run the entire synthesis

every time you make a change.

Out of Context Per IP Runs synthesis and creates a Design Check Point (DCP) for every individual

IP block within your design. These check points are then collected into a

black-box at the top-level implementation. Using this option means that only

the blocks you change need to be re-synthesized, which saves time. OOC-IP

also creates an IP customization file (XCI) for each IP block, allowing for

customization and OOC XDC files. OOC-IP is the default setting for synthesis

within Vivado. This option applies to all IP within the block diagram.

Out of Context Per Block Diagram Like the OOC-IP option however this option allows you to define the entire

block diagram as OOC.

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ – Reducing Compile Time

• Incremental synthesis can also be used when

the changes are small.

• Write out incremental synthesis to the post

synthesis design check point.

• Selecting incremental synthesis then provides

two options:

• Automatically use previous DCP

• Use a defined DCP

© Adiuvo Engineering and Training, Ltd. 2023

AMD Vivado™ – Reducing Compile Time

• Incremental implementation allows use of

Design Check Point as the starting point.

• Preserves QoR predictability by reusing

prior placement and routing from a

reference design.

• Speeds up place and route run time or

attempts last mile timing closure.

© Adiuvo Engineering and Training, Ltd. 2023

www.adiuvoengineering.com

adam@adiuvoengineering.com

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5814)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- 8086 StringDocument2 pages8086 StringKoush RastogiNo ratings yet

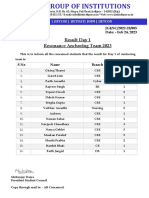

- Anchoring Result Day-1Document1 pageAnchoring Result Day-1Koush RastogiNo ratings yet

- SDN ArchDocument1 pageSDN ArchKoush RastogiNo ratings yet

- Motor FuzzyDocument5 pagesMotor FuzzyKoush RastogiNo ratings yet

- SCAN186Document1 pageSCAN186Koush RastogiNo ratings yet

- Sep 2020Document2 pagesSep 2020Koush RastogiNo ratings yet

- 077 - BTU-Improvement Exam. Notice For B. Tech. VII Semester, March-2023Document1 page077 - BTU-Improvement Exam. Notice For B. Tech. VII Semester, March-2023Koush RastogiNo ratings yet

- Iot Reference Model PDFDocument7 pagesIot Reference Model PDFKoush RastogiNo ratings yet

- Basic Data Types in Python - Ipynb - ColaboratoryDocument5 pagesBasic Data Types in Python - Ipynb - ColaboratoryKoush RastogiNo ratings yet

- Iot ArchitectureDocument14 pagesIot ArchitectureKoush RastogiNo ratings yet

- 3 SEPT 2021 Final Scheme and SyllabusDocument33 pages3 SEPT 2021 Final Scheme and SyllabusKoush RastogiNo ratings yet

- Delay Calculation of Cell Based Designs For The Pre-Layout and Post-Layout Timing VerificationDocument6 pagesDelay Calculation of Cell Based Designs For The Pre-Layout and Post-Layout Timing VerificationKoush RastogiNo ratings yet

- Copyright StatementDocument1 pageCopyright StatementKoush RastogiNo ratings yet