Professional Documents

Culture Documents

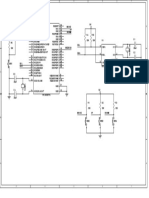

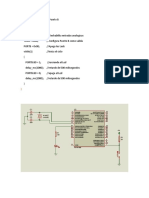

Architecture of PIC18F4550

Uploaded by

veeramaniks408Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Architecture of PIC18F4550

Uploaded by

veeramaniks408Copyright:

Available Formats

Data Bus<8>

Table Pointer<21> PORTA

RA0/AN0

Data Latch RA1/AN1

inc/dec logic 8 8

RA2/AN2/VREF-/CVREF

Data Memory RA3/AN3/VREF+

PCLATU PCLATH (2 Kbytes) RA4/T0CKI/C1OUT/RCV

21

Address Latch RA5/AN4/SS/HLVDIN/C2OUT

20

PCU PCH PCL OSC2/CLKO/RA6

Program Counter 12

Data Address<12>

PORTB

31 Level Stack

12 RB0/AN12/INT0/FLT0/SDI/SDA

Address Latch 4 4

RB1/AN10/INT1/SCK/SCL

BSR FSR0 Access

Program Memory STKPTR Bank RB2/AN8/INT2/VMO

(24/32 Kbytes) FSR1 RB3/AN9/CCP2(4)/VPO

FSR2 12 RB4/AN11/KBI0/CSSPP

Data Latch

RB5/KBI1/PGM

RB6/KBI2/PGC

inc/dec

8 logic RB7/KBI3/PGD

Table Latch

Address PORTC

ROM Latch

Instruction Bus <16> Decode RC0/T1OSO/T13CKI

RC1/T1OSI/CCP2(4)/UOE

IR RC2/CCP1/P1A

RC4/D-/VM

RC5/D+/VP

8 RC6/TX/CK

Instruction State Machine RC7/RX/DT/SDO

Decode & Control Signals

Control

PRODH PRODL

PORTD

8 x 8 Multiply

VDD, VSS 3 8

Internal

(2) Oscillator Power-up RD0/SPP0:RD4/SPP4

OSC1 Timer BITOP W

Block 8 8 8 RD5/SPP5/P1B

OSC2(2) Oscillator RD6/SPP6/P1C

INTRC RD7/SPP7/P1D

Start-up Timer

T1OSI Oscillator 8 8

Power-on

T1OSO 8 MHz

Oscillator Reset ALU<8>

Watchdog 8

ICPGC(3) Single-Supply Timer

Programming Brown-out

ICPGD(3) Reset PORTE

In-Circuit RE0/AN5/CK1SPP

(3)

ICPORTS Debugger Fail-Safe RE1/AN6/CK2SPP

Clock Monitor Band Gap RE2/AN7/OESPP

ICRST(3)

Reference MCLR/VPP/RE3(1)

MCLR(1) USB Voltage

Regulator

VUSB

BOR Data

EEPROM Timer0 Timer1 Timer2 Timer3

HLVD

MSSP EUSART ADC

Comparator ECCP1 CCP2 USB

10-Bit

You might also like

- PREPARE FOR FINAL WITH PIC16F887 FUNCTIONSDocument29 pagesPREPARE FOR FINAL WITH PIC16F887 FUNCTIONSGöksun NejatNo ratings yet

- 16F88Document24 pages16F88thetkhinechoNo ratings yet

- KS31203 Embedded System: LECTURE 6 - Working With Time: Interrupts and TimersDocument32 pagesKS31203 Embedded System: LECTURE 6 - Working With Time: Interrupts and TimersZulhaily ZhafranNo ratings yet

- 7.3. Analog Input: Embedded System DesignDocument23 pages7.3. Analog Input: Embedded System DesignGia HuyNo ratings yet

- PIC16C773Document202 pagesPIC16C773Luis Oliveira SilvaNo ratings yet

- Gesture Controlled Slide NavigatorDocument17 pagesGesture Controlled Slide NavigatorAnkur GuptaNo ratings yet

- Tai Lieu Thi Nghiem VXL Top 100 - ModifyDocument33 pagesTai Lieu Thi Nghiem VXL Top 100 - ModifyTrần Anh KhoaNo ratings yet

- 16F877 Data SheetDocument201 pages16F877 Data Sheetjohn11221No ratings yet

- Experiment 4: Connecting Input DevicesDocument15 pagesExperiment 4: Connecting Input DevicesTariq MograbiNo ratings yet

- Datasheet PIC16f870Document9 pagesDatasheet PIC16f870Esteban AdrianNo ratings yet

- Datasheet Pic 16 F 871Document172 pagesDatasheet Pic 16 F 871Sound AplicacionNo ratings yet

- 16F87X Datasheet - Version ResumidaDocument69 pages16F87X Datasheet - Version ResumidamowliwhiteNo ratings yet

- Timers, Interrupts and LCD ControlDocument11 pagesTimers, Interrupts and LCD ControlTrần Ngọc Thiên DiNo ratings yet

- Exemplo KetyDocument2 pagesExemplo Ketyric1988lealNo ratings yet

- GPSUser ManualDocument15 pagesGPSUser ManualaravindbprasadNo ratings yet

- PIC16F88X Memory Programming Specification PDFDocument36 pagesPIC16F88X Memory Programming Specification PDFMarcio FreitasNo ratings yet

- PIC-WEB-BOX, Board Revision C - PORT PINOUTDocument1 pagePIC-WEB-BOX, Board Revision C - PORT PINOUTalo 247No ratings yet

- SDNL 1Document1 pageSDNL 1Trọng LêNo ratings yet

- PIC16F882/883/884/886/887: 28/40/44-Pin Flash-Based, 8-Bit CMOS MicrocontrollersDocument78 pagesPIC16F882/883/884/886/887: 28/40/44-Pin Flash-Based, 8-Bit CMOS Microcontrollersfranklin monteroNo ratings yet

- Lecture 3Document39 pagesLecture 3Nour Ziad Ibrahim AlkurdiNo ratings yet

- Drill 6.0 Adc Dac Sensors Part 2Document14 pagesDrill 6.0 Adc Dac Sensors Part 2DuaneNo ratings yet

- Ch4 TimersDocument18 pagesCh4 TimersBerra BeşerNo ratings yet

- KeypadDocument1 pageKeypadPhap Nguyen100% (1)

- PIC18F4550 LED Blink Using CCS C CompilerDocument5 pagesPIC18F4550 LED Blink Using CCS C CompilerManuel godoy ramirez100% (1)

- Interfacing Keypad With PIC 16F877A MicrocontrollerDocument6 pagesInterfacing Keypad With PIC 16F877A MicrocontrollerEysha qureshi100% (1)

- Read Chapter 3, The 8051 Microcontroller Architecture, Programming and Applications by Kenneth .J.AyalaDocument32 pagesRead Chapter 3, The 8051 Microcontroller Architecture, Programming and Applications by Kenneth .J.AyalapsmeeeNo ratings yet

- Usbmod1: USB Plug and Play Serial Development ModuleDocument5 pagesUsbmod1: USB Plug and Play Serial Development ModuleMaiChiVuNo ratings yet

- East West LDR CircuitDocument1 pageEast West LDR CircuitSahariar Bin ShafiqueNo ratings yet

- Da DKCNDocument3 pagesDa DKCNTrọng LêNo ratings yet

- ATtiny2313 DatasheetDocument224 pagesATtiny2313 DatasheetIonut AlexeNo ratings yet

- Attiny 441Document366 pagesAttiny 441micNo ratings yet

- Circuito EletrônicoDocument1 pageCircuito EletrônicoLucas Pardinho MoraisNo ratings yet

- PIC16F87XA Data Sheet: 28/40-Pin Enhanced FLASH MicrocontrollersDocument56 pagesPIC16F87XA Data Sheet: 28/40-Pin Enhanced FLASH MicrocontrollersXinantecatl L SolaresNo ratings yet

- Datasheet - HK Pic16f73 271716 PDFDocument168 pagesDatasheet - HK Pic16f73 271716 PDFAbdul QadirNo ratings yet

- Project 07aDocument1 pageProject 07aPushpa kumaraNo ratings yet

- Dokumen - Tips - 11 Siemens s5s7 Series M2icokr Siemen11 Siemens s5s7 Series s5 95uDocument20 pagesDokumen - Tips - 11 Siemens s5s7 Series M2icokr Siemen11 Siemens s5s7 Series s5 95uzahra ghaziNo ratings yet

- Programa LedsDocument8 pagesPrograma Ledsodin11611No ratings yet

- 03 - Circuit DescriptionDocument37 pages03 - Circuit Descriptionkhoi vuNo ratings yet

- PIC16F87XA Pin Diagram OverviewDocument3 pagesPIC16F87XA Pin Diagram OverviewKev Vaca100% (1)

- 8-Bit Microcontroller With 8K Bytes In-System Programmable Flash Atmega48/V Atmega88/V Atmega168/V PreliminaryDocument25 pages8-Bit Microcontroller With 8K Bytes In-System Programmable Flash Atmega48/V Atmega88/V Atmega168/V PreliminaryJose Oscar ManriqueNo ratings yet

- MDT2051Document13 pagesMDT2051Tarzan JoeNo ratings yet

- Adc Pic16f877Document1 pageAdc Pic16f877Phap Nguyen100% (1)

- 4 IOports v21Document24 pages4 IOports v21Thao Vo VanNo ratings yet

- PIC16C72ADocument122 pagesPIC16C72AsafsaNo ratings yet

- Microcontroller With 2/4K Bytes In-System Programmable FlashDocument22 pagesMicrocontroller With 2/4K Bytes In-System Programmable FlashRicardoNo ratings yet

- Kepad Password Report&Document12 pagesKepad Password Report&eugeni madaNo ratings yet

- Skematik Pengaman Pintu DG RFID PDFDocument1 pageSkematik Pengaman Pintu DG RFID PDFEka KusyantoNo ratings yet

- ATmega 84,88,168Document25 pagesATmega 84,88,168Nikita LeškoNo ratings yet

- A14rm LP 1018a K456Document37 pagesA14rm LP 1018a K456chipmaster86No ratings yet

- BAI 1 - Led Don - 7 DoanDocument7 pagesBAI 1 - Led Don - 7 DoanTrần Ngọc Thiên DiNo ratings yet

- Transformer voltage regulator circuit with 7805 rectifier and motor driverDocument1 pageTransformer voltage regulator circuit with 7805 rectifier and motor driverWaqas AhmadNo ratings yet

- AVR and C Programming FinalDocument58 pagesAVR and C Programming Finalzbhp zNo ratings yet

- Final Exam Topic 6 - Example Questions - SPIDocument4 pagesFinal Exam Topic 6 - Example Questions - SPITiến ThànhNo ratings yet

- PIC16F684: 14-Pin Diagram (PDIP, SOIC, TSSOP)Document1 pagePIC16F684: 14-Pin Diagram (PDIP, SOIC, TSSOP)Dreamon YaNo ratings yet

- ATtiny 461Document242 pagesATtiny 461Alberto LimónNo ratings yet

- How To Set Input and Output (PIC16F84) : RA4 RA3 RA2 RA1 RA0Document18 pagesHow To Set Input and Output (PIC16F84) : RA4 RA3 RA2 RA1 RA0Linda purnamaNo ratings yet

- ELD310Document44 pagesELD310Nhật Tú TrầnNo ratings yet

- VB MCQ 3Document2 pagesVB MCQ 3veeramaniks408No ratings yet

- Question Paper 8051 Microcontroller and ApplicationsDocument1 pageQuestion Paper 8051 Microcontroller and Applicationsveeramaniks408No ratings yet

- Section - A Answer All Questions (10 X 1 10 Marks)Document1 pageSection - A Answer All Questions (10 X 1 10 Marks)veeramaniks408No ratings yet

- PIC18F4550 Pin FunctionsDocument2 pagesPIC18F4550 Pin Functionsveeramaniks408No ratings yet

- Question Paper Robotics and Arduino ProgrammingDocument1 pageQuestion Paper Robotics and Arduino Programmingveeramaniks408No ratings yet

- VB MCQ 1Document2 pagesVB MCQ 1veeramaniks408No ratings yet

- VB MCQ 2Document3 pagesVB MCQ 2veeramaniks408No ratings yet

- Square Wave GenerationDocument1 pageSquare Wave Generationveeramaniks408No ratings yet

- VB MCQ 2Document3 pagesVB MCQ 2veeramaniks408No ratings yet

- Power ElectronicsDocument1 pagePower Electronicsveeramaniks408No ratings yet

- VB MCQ 1Document1 pageVB MCQ 1veeramaniks408No ratings yet

- VB MCQ 2Document3 pagesVB MCQ 2veeramaniks408No ratings yet

- Electric Drives and ControlDocument1 pageElectric Drives and Controlveeramaniks408No ratings yet

- Power System ProtectionDocument1 pagePower System Protectionveeramaniks408No ratings yet

- Power Sytem AnalysisDocument1 pagePower Sytem Analysisveeramaniks408No ratings yet

- Priniciples of Embedded SystemsDocument2 pagesPriniciples of Embedded Systemsveeramaniks408No ratings yet

- Microprocessor and ControllersDocument1 pageMicroprocessor and Controllersveeramaniks408No ratings yet

- DSP QuestionsDocument2 pagesDSP Questionsveeramaniks408No ratings yet

- Embedded System Design Unit - I Embedded Systems OverviewDocument1 pageEmbedded System Design Unit - I Embedded Systems Overviewveeramaniks408No ratings yet

- Analog and Digital ElectronicsDocument1 pageAnalog and Digital Electronicsveeramaniks408No ratings yet

- Digital Signal ProcessingDocument1 pageDigital Signal Processingveeramaniks408No ratings yet

- ECS Modulation Antennas Digital Microwaves Optical SatelliteDocument1 pageECS Modulation Antennas Digital Microwaves Optical Satelliteveeramaniks408No ratings yet

- Microprocessor Instruction Set of Intel 8085Document9 pagesMicroprocessor Instruction Set of Intel 8085Sreejith UnnikrishnanNo ratings yet

- Analog, Digital and Circuit SimulationDocument1 pageAnalog, Digital and Circuit Simulationveeramaniks408No ratings yet

- DSP QuestionsDocument2 pagesDSP Questionsveeramaniks408No ratings yet

- MTECH EE Power Electronics & Drives Common Detail Syllabus 4 2010 2Document18 pagesMTECH EE Power Electronics & Drives Common Detail Syllabus 4 2010 2shashibhushanwashereNo ratings yet

- DSP QuestionsDocument2 pagesDSP Questionsveeramaniks408No ratings yet

- Industrial Networking: Industrial Communication Network Is A Special Type of Network Made To Handle Real-TimeDocument1 pageIndustrial Networking: Industrial Communication Network Is A Special Type of Network Made To Handle Real-Timeveeramaniks408No ratings yet

- Programmable Peripheral Interface 8255: Microprocessor Unit 4 1Document32 pagesProgrammable Peripheral Interface 8255: Microprocessor Unit 4 1veeramaniks408No ratings yet