Professional Documents

Culture Documents

计算机组成原理A复习提纲 2022年春

Uploaded by

顾磊Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

计算机组成原理A复习提纲 2022年春

Uploaded by

顾磊Copyright:

Available Formats

《计算机组成原理 A》2022 年春复习提纲

计算机组成原理课程组

考试时间: 6 月 2 日 16:00-18:00

一、题型:

填空 10 分;选择 15 分;综合题 75 分;

二、复习资料:

主要结合教学 PPT、作业,教材为辅。

复习提纲

一、填空 10

海明校验的基本原理、GB2312 与区位码的转换(实验对应内容)、补码与真值

的转换、补码加减法运算、一位全加器原理、浮点数规格化左规和右规的原理、

数据对齐、单总线 CPU 简单模型中指令执行的过程细节(3.2 节 PPT38 页对应的

单总线 CPU 指令执行过程)、Cache 地址映射(三种映射方式,特点)、寻址方式

(PPT 上结合图)、指令周期与机器周期含义 、总线分类(三种类型)。

二、选择 15

(出题范围是雨课堂习题、SPOC 单元测试和章节测试、教材每章的选择题

其中简单的题目)

补码的概念以及计算(特别注意特殊真值的补码)、进制数的互相转换、奇

偶校验原理相关、大小端与数据对齐(对应雨课堂例题搞懂)、存储器的基本知

识(各种存储器的特点 RAM、SRAM、DRAM、ROM、EPROM)、存储器芯片的寻址范

围、各种寻址方式的特点、中断的过程(中断响应周期)、中断屏蔽技术原理。

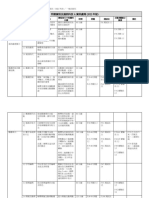

三、综合题(75 分)

1、 浮点数的规格化(754 标准十进制写成 754 规格二进制;十六进制 754 编码

转换为十进制真值) 2 套题 8 分

参见教学 PPT2.1 节 72 也-75 页例题。教材例题(已收入复习 PPT)

搞懂以上例题原理才可以解题。

2、浮点数的手动计算。作业 3.9 类似题目。6 分

搞懂 PPT3.2 节例题(已收入复习 PPT)和作业 3.9 题(3.9-1 已收入复习 PPT)。

解题步骤:转换为浮点数形式、对阶、尾数运算、规格化、舍入、溢出判断

3、 海明编码 (根据编码规则填写海明校验组分布表,并给出 Pi 和 Gi 逻辑表

达式,实验画图-海明编码,写出给定有效信息为 XXXX(如 1001)的海明码。)9

分

1) 要求被编码的数据位小于等于 16 位。作业搞懂。

2) 教学 PPT2.4 节 18-23 页内容原理。重点是 23 页的填表原理,从而得出

Pi 和 Gi 的表达式,理解后可以做出不同有效数据位的海明校验组分布

表。分组有了,就很容易可以得到 Pi 和 Gi 逻辑表达式,以及画图如何

连线。

3) 注意 PPT 里面的备注有助于理解。

4、ALU 并行加法器进位链设计(4 位并行进位链 74182 内部逻辑,部分连线,

表达式)8 分

1) 教学 PPT 3.1 节,31-42 页。

2) 可能要求补充画出某些电路的连线,如 74182。并写出某个进位 Cn 或 P*

和 G*的表达式。

3) 重点是学会分析推导并行加法器的进位链,会推导 Cn 以及 Pn 和 Gn 的逻

辑表达式(n<=4),表达式有了就可以很方便的补充画图了。

5、指令格式。按照相应要求设计指令格式;或者给了指令格式写出不同寻址方

式的 EA 以及寻址范围。5 分

两类题目均已收录入复习 PPT。

6、主存扩展(字位同时扩展),并回答问题、画图。出 2 套题 8 分

1) 教学 PPT 4.3 节,字位同时扩展例题(已收入复习 PPT)。和存储器作业

第二题(自己出的题目)类似题目

2) 考字位同时扩展,字节编址,一定要考虑 CPU 地址线低位空余的问题(半

字节对齐问题)

3) 需要回答搞清楚需要的芯片数量,地址线和数据线数量(不要求写出各

个芯片地址范围)。注意地址线条数是按照字节编址来计算的的。

4) 会画出图(类似 PPT 例题)。

5、Cache(组相连地址映射。主存地址和 Cache 地址位数计算;主存地址的划分

情况,并标出各部分的位数;计算 Cache 容量)2 套题 7 分

1) 考察组相连 2 路、4 路或 8 路。

2) 教学 PPT 对应 4.5 节。Cache 例题选讲例 1 类似题目(已收入复习 PPT);

作业三,4.12 题目类似(增加 Cache 容量计算内容)。

知识点:

1) 主存和 Ccache 的数据块大小相同。

2) K 路组相连,Cache 每组 K 个块。

3) Cache 分组,每组 K 个块/行。主存按 Cache 组数分组。

4) Cache 共 n 组,主存第 j 块号映射到 Cache 的组号为: i=j mod n 即主

存组内的 0 号块映射到 Cache0 号组的任意行,依次类推。

5) 主存地址构成

6)Cache 容量=cache 行的位数×行数;

Cache 行的位数=D + V + Tag(标记) + 数据块位数

6、数据通路与指令流程:考察内容包括 CPU 内部部件名称与功能;相应指令(2

条指令,包含取指过程)的数据通路(每个周期执行何种操作/数据流、控制信

号);出两套题(要求写出的功能部件名称不同,MIPS 指令不同) 16 分

1) CPU 结构中某 2 个功能部件名称和功能 4 分

2) 写出某指定指令的数据通路(取指令、基本指令——LW、SW、BEQ、ADD、

ADDI 的数据通路,可能出现没有讲过的指令,但都是非常简单的,只有

在某个节拍发出的 ALU 控制信号不同,类似作业五第二题)

3) 给出指定指令(参见作业和 PPT 内容)及时钟节拍,填写给出的指令每

个节拍的数据流和控制信号。2 条指令,共 12 分。

4) 整体内容对应 PPT6.1 节 CPU 结构与数据通路 PPT 的内容(均已收入复习

PPT)。

7、中断屏蔽字与中断处理顺序;类似 PPT 例题。出 2 套题。8 分,中断屏蔽字,

4 分;图 4 分。

1) 教学 PPT 9.1 节,32-44 页。特别注意其中例题,例题搞懂。

2) 给出处理优先级、填写中断屏蔽字的表;或者给出中断屏蔽字的表,写

出处理优先级。

3) 画出 CPU 执行程序的轨迹;

You might also like

- 安泰数据结构Document6 pages安泰数据结构刘奕涵No ratings yet

- 计原00 PDFDocument120 pages计原00 PDFLeming ShenNo ratings yet

- 王道计算机考研团队整理 22考研408真题及答案Document21 pages王道计算机考研团队整理 22考研408真题及答案Riet ANo ratings yet

- C语言程序设计上机指导教程 人民邮电出版社 贾若 刘枧 主编 Isbn:9787115254887Document257 pagesC语言程序设计上机指导教程 人民邮电出版社 贾若 刘枧 主编 Isbn:9787115254887poorkids pkNo ratings yet

- 计算机组成原理Document18 pages计算机组成原理lilliadriggarsNo ratings yet

- ch0 课程前言Document19 pagesch0 课程前言Herman QinNo ratings yet

- ch0 课程前言Document19 pagesch0 课程前言Herman QinNo ratings yet

- 2022数据库系统概论 期末项目相关论文Document23 pages2022数据库系统概论 期末项目相关论文马文辉No ratings yet

- 【不周山之读薄 CSAPP】贰 机器指令与程序优化Document39 pages【不周山之读薄 CSAPP】贰 机器指令与程序优化刘岑岑No ratings yet

- Hive调优及优化的12种方式 - 知乎Document5 pagesHive调优及优化的12种方式 - 知乎zhao.tangNo ratings yet

- 基于numeca Fine Turbo的并行计算测试 董晶Document4 pages基于numeca Fine Turbo的并行计算测试 董晶彭昊No ratings yet

- CsharpDocument166 pagesCsharpNicolas YanNo ratings yet

- 软件设计师笔记Document16 pages软件设计师笔记luzhousfNo ratings yet

- Chapter 03Document52 pagesChapter 03陳思媛No ratings yet

- 1.1 计算机系统简介Document28 pages1.1 计算机系统简介XiaXiao DengNo ratings yet

- 2015 2016第二学期微机原理II B卷Document1 page2015 2016第二学期微机原理II B卷Zhongjie YangNo ratings yet

- 第1章 matlab基础入门Document122 pages第1章 matlab基础入门Ralf ReinhartNo ratings yet

- GeoScene地理编码服务器产品用户手册Document38 pagesGeoScene地理编码服务器产品用户手册mipslupNo ratings yet

- 多核及众核体系结构下线性代数算法研究进展 陶袁Document10 pages多核及众核体系结构下线性代数算法研究进展 陶袁shang zhangNo ratings yet

- labuladong的算法秘籍V1 5Document664 pageslabuladong的算法秘籍V1 5张晨No ratings yet

- 第一章计算机系统概论Document84 pages第一章计算机系统概论KeiraNo ratings yet

- CH5 习题课 课件Document7 pagesCH5 习题课 课件Yang ZhouNo ratings yet

- HGM7220N 7220S通信协议V1.0 cnDocument27 pagesHGM7220N 7220S通信协议V1.0 cn何青No ratings yet

- CPU与GPU上几种矩阵乘法的比较与分析Document3 pagesCPU与GPU上几种矩阵乘法的比较与分析Tse On KiNo ratings yet

- 数学建模竞赛 自学指导建议Document2 pages数学建模竞赛 自学指导建议dubai52233No ratings yet

- Python面试大全Document59 pagesPython面试大全ほう子じゃんNo ratings yet

- 天勤408真题2019Document8 pages天勤408真题2019Regol wangNo ratings yet

- 153面试疑难杂症问题集锦Document30 pages153面试疑难杂症问题集锦一世长安No ratings yet

- (陈英时 2007) 采用多波前法求解大型结构方程组 PDFDocument3 pages(陈英时 2007) 采用多波前法求解大型结构方程组 PDFAnonymous 3XJRG5SINo ratings yet

- 2015计算机考研408真题Document9 pages2015计算机考研408真题zyc15207269894No ratings yet

- 哈工大入学考试大纲Document7 pages哈工大入学考试大纲yingduo liuNo ratings yet

- 05数组:为什么很多编程语言中数组都从0开始编号?Document14 pages05数组:为什么很多编程语言中数组都从0开始编号?zhang1032No ratings yet

- 935考试大纲2023Document8 pages935考试大纲2023陈独秀No ratings yet

- Nodejs Mongo SQL Query GuideDocument17 pagesNodejs Mongo SQL Query Guidexhacker.pengNo ratings yet

- BESS 5 介绍 2009Document5 pagesBESS 5 介绍 2009zhong weiNo ratings yet

- 孙淼 系统硬件综合设计报告Document79 pages孙淼 系统硬件综合设计报告miao sunNo ratings yet

- 01 字节跳动+EB+级+Iceberg+数据湖的机器学习应用与优化-谢凯Document34 pages01 字节跳动+EB+级+Iceberg+数据湖的机器学习应用与优化-谢凯hunaos1No ratings yet

- 1emp Introduction 2021 FallDocument24 pages1emp Introduction 2021 Fall陈新No ratings yet

- 屋 宇 裝 備 工 程 Autocad 電 腦 繪 圖 I 基 礎 證 書 (兼 讀 制)Document3 pages屋 宇 裝 備 工 程 Autocad 電 腦 繪 圖 I 基 礎 證 書 (兼 讀 制)Best PalNo ratings yet

- Python数据结构与算法分析(第2版) by 布拉德利·米勒 戴维·拉努姆Document594 pagesPython数据结构与算法分析(第2版) by 布拉德利·米勒 戴维·拉努姆dsfsdfNo ratings yet

- 崔百胜:初级班课程大纲Document6 pages崔百胜:初级班课程大纲lixuanNo ratings yet

- Slides V2 Pengcheng AiDocument29 pagesSlides V2 Pengcheng Ai964520978sbjNo ratings yet

- HKU PUB ICT DSE Scheme of Work - ChiDocument26 pagesHKU PUB ICT DSE Scheme of Work - Chicpu.lmkNo ratings yet

- 111?????????e-Learning???? - 1101208 2Document14 pages111?????????e-Learning???? - 1101208 2吳東翰No ratings yet

- 可部署的量化感知训练算法研究-商汤科技见习研究员李雨杭 智东西公开课Document35 pages可部署的量化感知训练算法研究-商汤科技见习研究员李雨杭 智东西公开课jiahao liNo ratings yet

- 可部署的量化感知训练算法研究-商汤科技见习研究员李雨杭 智东西公开课Document35 pages可部署的量化感知训练算法研究-商汤科技见习研究员李雨杭 智东西公开课jiahao liNo ratings yet

- 20150105第5版ppt 第3章 关系数据库标准语言sql(1)Document96 pages20150105第5版ppt 第3章 关系数据库标准语言sql(1)Chengwei WuNo ratings yet

- 华为FPGA设计流程指南Document24 pages华为FPGA设计流程指南lieshi2958100% (1)

- 系統分析與設計補充教材 (0) 系統分析規格書製作Document55 pages系統分析與設計補充教材 (0) 系統分析規格書製作Huang ZHENGNo ratings yet

- 陈宇凡 201913158072 操作系统课设Document22 pages陈宇凡 201913158072 操作系统课设闵和祥No ratings yet

- F7811 CH18Document49 pagesF7811 CH18RDNo ratings yet

- Fpga TCP Stack UgDocument16 pagesFpga TCP Stack UgyiqingqazwsxNo ratings yet

- 严蔚敏《数据结构》冲刺串讲与模拟四套卷Document29 pages严蔚敏《数据结构》冲刺串讲与模拟四套卷adsasd dsadadsNo ratings yet

- c 面经总结Document24 pagesc 面经总结卓航李No ratings yet

- 2020212309 安柯锦 实验报告Document38 pages2020212309 安柯锦 实验报告徐赟博No ratings yet

- 基于"神威·太湖之光"的三维有限长方柱绕流直接数值模拟Document8 pages基于"神威·太湖之光"的三维有限长方柱绕流直接数值模拟3310417314No ratings yet

- CCNA1 - Final Exam Answers (04!18!2008 10-30)Document18 pagesCCNA1 - Final Exam Answers (04!18!2008 10-30)Keiran RitsonNo ratings yet

- (鑫威資訊) ICFD簡易訓練用講義20170724Document43 pages(鑫威資訊) ICFD簡易訓練用講義20170724fyfoxNo ratings yet

- 计算机组成原理课后习题及答案 唐朔飞 (完整版)Document335 pages计算机组成原理课后习题及答案 唐朔飞 (完整版)Junyi ZhongNo ratings yet

- HUAWEI SP - Flash - Tool - v1.3 - 1352 Instruction (中文) - 20140217Document15 pagesHUAWEI SP - Flash - Tool - v1.3 - 1352 Instruction (中文) - 20140217Sherif KhedrNo ratings yet

- NI VeriStand 2010 使用手册Document59 pagesNI VeriStand 2010 使用手册jackgeng1971No ratings yet

- Java PPT AllDocument269 pagesJava PPT AllShanyue HuangNo ratings yet

- 深入理解计算机系统第二版中文Document729 pages深入理解计算机系统第二版中文ALEX CHANGNo ratings yet

- 晶晨烧录工具V2指南 V0.7Document16 pages晶晨烧录工具V2指南 V0.7Aaron Zheng100% (1)

- 1 入门Document47 pages1 入门Johanna YeNo ratings yet