Professional Documents

Culture Documents

ESC Overview

Uploaded by

raytsao65Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

ESC Overview

Uploaded by

raytsao65Copyright:

Available Formats

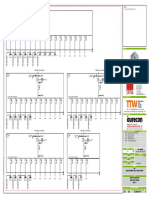

EtherCAT SubDevice Controller Overview (1/3)

as of Oct 2023

Name AX58100 AX58200 AX58400 fido5200 TMC8462 ET1100 ET1810/ET1811/ET1812 ET1851/ET1816/ET1817 Anybus NP40 XMC4300 XMC4800

Type ASIC ARM MPU Dual-Core ARM MPU ASIC ASIC ASIC Intel (Altera) FPGA + IP Core Xilinx FPGA + IP Core ARM MPU ARM MPU ARM MPU

Supplier

80-pin LQFP 144-pin HSFBGA 225LD EHS-TFBGA 144 FBGA (0.8 mm) BGA121 BGA128 BGA VF400

Package FPGA dependent FPGA dependent 100 LQFP (0.5 mm) 100 LQFP (0.5 mm)

0.4 mm pitch 0.8 mm pitch 0.8 mm pitch 144 LQFP (0.5 mm) 0.75 mm pitch 0.8 mm pitch 0.8 mm pitch

20 x 20 mm

10 x 10 mm (FBGA)

Size 12 x 12 mm 10 x 10 mm 13 x 13 mm 9x9 mm 10 x 10 mm FPGA dependent FPGA dependent 17 x 17 mm 16 x 16 mm 16 x 16 mm

20 x 20 mm (LQFP)

12 x 12 mm

serial/parallel serial/parallel Anybus interface (8- / 16-bit 30

SPI/parallel uC bus uC bus parallel serial/parallel µC bus µC bus

µC Interface serial or standalone (8- /16-bit, async) (8- /16-bit, async) ns parallel, 20 MHz SPI, Shift

(8/16-bit, asynchronous) (Internal, AHB) (Internal, AHB) (16/32-bit) (8/16bit, sync/async)* (internal, AHB) (internal, AHB)

AVALON®* OPB®* and PLB®* register, UART)

8 256 / 256

Digital I/O 32 - 20 0..16* 8-32* 8-32* 8-32* - -

(Event Output/Capture) (Shift register mode)

General Purpose I/O 32 up to 76* up to 97* - 0..24* 0-32* 0-128* 0-128* - 0 - 46 0 - 123

DPRAM 9 kByte 160 kByte 1 Mbyte 10 kByte 16 kByte 8 kByte 0...60 kByte* 0...60 kByte* 12 kByte 8 kByte 8 kByte

SyncManager Entities 8 8 8 8 8 8 0…8* 0…8* 4 8 8

FMMU Entities 8 8 8 8 8 8 0…8* 0…8* 4 8 8

Distributed Clock Support yes (64-bit) yes (64-bit) yes (64-bit) yes yes yes yes* yes* yes yes (64 Bit) yes (64 Bit)

No. of Ports 2 (100BaseTX) + Opt. 1 (MII) 2 (100BaseTX) + Opt. 1 (MII) 2 (100BaseTX) + Opt. 1 (MII) 2 (MII/RMII) 2 (100BaseTX) 2-4 (MII/E-BUS)* 1-3 (MII/max. 2 RMII) 1-3 (MII/max. 2 RMII) 2 (MII) 2 (MII) 2 (MII)

2 integrated Ethernet PHYs, USB

2.0 HS OTG, 10/100Mbps

Ethernet MAC with RMII and Dual-Core 480MHz ARM Cortex-M7 &

240MHz Cortex-M4 MCU,

hardware cryptography 2 Mbytes embedded Flash memory, 2

accelerator ESC Integrated PHY, USB HS

EtherCAT® node on an ARM® EtherCAT® node on an ARM®

6xLPUARTs, 3xISO-7816-3, OTG, Additional RMII/MII Ethernet MAC Wide supply range (up to 35V),

100BASE-FX support with IEEE 1588 for multiprotocol

Various license models and Various license models and Cortex®-M4 processor with up to Cortex®-M4 processor with up to

1xQuad-SPI, 3xI2C, 1xI2S, 2x Integrated DC/DC regulators, Multi-protocol support, ESC

2 integrated PHYs support, TFT-LCD display controller, Multi-protocol support, OpenCore Plus evaluation Version 256kB on-chip flash, 128kB on- 2MB on-chip flash, 352kB on-

2xUSCI, 2xCAN, 1xSPI Flash I/F, 8x Direct High Voltage I/Os, Frame forwarding delay: 114 ns,

Specials 3-ch PWM and S/D I/F Security and Gigabit Ethernet support, BGA routable with standard PCB are available. are available. chip RAM and analog/mixed chip RAM and analog/mixed

2xSDHC, 1x16-ch/12-bit ADC, Cryptographic Accelerator , 96-bit UID, Multi-function I/O block, MDP, possible to implement

ABZ and Hall encoder I/F Event Output/Capture I/O A wide range of Intel (former: A wide range of Xilinx FPGAs are signal capabilities. Qualified for signal capabilities. Qualified for

2x12-bit DAC, 2xAnalog Watchdog, RTC /SysTick Integrated PHYs, several device profiles

SPI master I/F Altera) FPGAs are supported supported up to 125°C ambient up to 125°C ambient

Comparators, 2xOperational timers, Rich communication/control BGA routable with standard PCB

interfaces such as SPI/UART/I2C temperature. temperature.

Amplifiers , 4x32-bit timers,

/I2S/SAI/CAN/SDMMC/ADC/DAC/HDMI-

24x16-bit PWM counters, 2xQEI, CEC/PWM/DFSDM,

1xECAP, supports Real-Time etc.

Clock (RTC) , Built-in Die

Temperature Sensor (DTS)

Further information https://www.asix.com.tw/en/product/IndustrialEthernet/EtherCAT/AX58100 https://www.asix.com.tw/en/product/IndustrialEthernet/EtherCAT/AX58200 https://www.asix.com.tw/en/product/IndustrialEthernet/EtherCAT/AX58400

www.analog.com https://www.trinamic.com/products/integrated-circuits/details/tmc8462-ba/ https://www.beckhoff.com/ET1100 https://www.beckhoff.com/en-en/products/i-o/ethercat-development-products/etxxxx-software/et1810-et1811.html https://www.beckhoff.com/en-en/products/i-o/ethercat-development-products/etxxxx-software/et1815-et1816.html www.anybus.com/technologies/network_processors.shtml www.infineon.com/ethercat www.infineon.com/ethercat

Data Sheet https://www.asix.com.tw/en/product/IndustrialEthernet/EtherCAT/AX58100 https://www.asix.com.tw/en/product/IndustrialEthernet/EtherCAT/AX58200 https://www.asix.com.tw/en/product/IndustrialEthernet/EtherCAT/AX58400 https://www.analog.com/en/products/fido5200.html https://www.trinamic.com/products/integrated-circuits/details/tmc8462-ba/ https://www.beckhoff.com/en-en/products/i-o/ethercat-development-products/ www.anybus.com/downloads/MMA318%20Anybus%20CompactCom%20C40.pdf

www.infineon.com/ethercat www.infineon.com/ethercat

*configurable

Trademarks and Patents

EtherCAT® is a registered trademark and patented technology, licensed by Beckhoff Automation GmbH, Germany. Other designations used in this publication may be trademarks whose use by third parties for their own purposes could violate the rights of the owners.

Note: Subject to technical modifications; no responsibility is accepted for the accuracy of this information. The content of all entries within the ESC overview is submitted by ETG members themselves. The ETG members are in charge of sales and support of their products as well as for the content of their entries. ETG therefore disclaims any liability for information contained therein.

EtherCAT SubDevice Controller Overview (2/3)

as of Oct 2023

Name netX 500 netX 51 netX 52 netX 90 netX 100 LAN9252 EC-1 RZ/T1 RZ/N2L RZ/T2M R-IN32M3-EC RX72M

Type ASIC ASIC ASIC ASIC ASIC ASIC ARM MPU ARM MPU ARM MPU ARM MPU ARM MPU ARM MPU

Supplier

LFBGA224, 0.8mm pitch

LFBGA176, 0.8mm pitch

BGA345 PBGA324 PBGA244 LFBGA144 BGA345 64 pin QFN (0.5 mm pitch) FBGA320 FBGA225, 0.8mm pitch FBGA320, 0.8mm pitch BGA324

Package 196 pin BGA (0.8 mm) LFQFP176, 0.5mm pitch

1 mm pitch 1 mm pitch 1 mm pitch 0.8 mm pitch 1 mm pitch 64 pin TQFP-EP (0.5 mm pitch) 0.8 mm pitch FBGA121, 0.8mm pitch FBGA225, 0.8mm pitch 1 mm pitch LFQFP144, 0.5mm pitch

LFQFP100, 0.5mm pitch

LFBGA224: 13 x 13 mm

LFBGA176: 13 x 13 mm

9 x 9 mm 13 x 13 mm 17 x 17 mm

Size 22 x 22 mm 19 x 19 mm 15 x 15 mm 10 x 10 mm 22 x 22 mm 12 x 12 mm 17 x 17 mm 19 x 19 mm LFQFP176: 24 x 24 mm

12 x 12 mm 10 x 10 mm 13 x 13 mm LFQFP144: 20 x 20 mm

LFQFP100: 14 x 14 mm

USB Host/Function, CAN-FD, SPI, USB Host/Function, CAN-FD, SPI,

µC bus µC bus µC bus µC bus µC bus USB Host/Function, CAN, SCIFA, 16/32-bit parallel and various 16/32-bit parallel (master/slave) USB, CAN, UART, SPI, I2C, SCI,

µC Interface Host Bus/SPI/SQI SCI, DSMIF, I2C, xSPI, External SCI, DSMIF, I2C, xSPI, External

(internal, 32bit) (internal, 32bit) (internal, 32bit) (internal, 32bit) (internal, 32bit) I2C RSPI, Flash serial (SPI/I2C/UART) and serial (SPI/I2C/UART) QSPI

BUS IF(SRAM/SDRAM/Host IF) BUS IF(SRAM/SDRAM)

Digital I/O - - - - - 0-16* - - - - - 44

115* GPIOs / 8 Input (port

General Purpose I/O 16 32 24 16 16 0-16* multiplexed, partial 5V-tolerant, 0-209* 0-134* 0-193* 0-96* 0-182*

open drain, input pull-up)

256/512 Byte 256/512 Byte 512 KB (ATCM) with ECC

DPRAM 6 kByte 6 kByte 6 kByte 4 kByte 8 kByte 8 kByte 8 kByte 8 kByte 8 kByte

(Mailbox/Process Data) (Mailbox/Process Data) 32 KB (BTCM) with ECC

SyncManager Entities 4 8 8 8 4 4 8 8 8 8 8 8

FMMU Entities 3 8 8 8 3 3 8 8 8 8 8 8

Distributed Clock Support yes yes yes yes yes yes yes (64 bit) yes yes yes yes yes (64 bit)

No. of Ports 2 (100BaseTX) 2 (100BaseTX) 2 (100BaseTX) 2 (100BaseTX) 2 (100BaseTX) 2 (100BaseTX) + opt. 1 (MII) 2 (MII) 2 (RMII/MII) 3 (RGMII/RMII/MII) 3 (RGMII/RMII/MII) 2 (100BaseTX) 2 (100BaseTX/MII/RMII)

Multi-protocol support

Additional Ethernet port

Multi-protocol support, (EtherCAT, etc), Multi-protocol support

(RMII/MII), 2-axis high-speed

Integrated PHYs, Optimized for network (EtherCAT, etc),

motion control support, Multi-protocol support

Integrated μC, companion chip (parallel bus Optimized for motor control (2-

Multi-protocol support, Multi-protocol support, Multi-protocol support, Multi-protocol support, Cable Diagnostics, digital encoder interfaces (EnDat, (EtherCAT, etc.), Security option,

OnChip Flash 1,5 Mbytes, slave, xSPI slave interface to axis high-speed motion control Multi-protocol support, SPI, I2C,

Integrated PHYs, Integrated PHYs, Integrated PHYs, Integrated PHYs, 100FX support, Safety Functions, Multi-Function BiSS, others), Multi-protocol Encryption option,

Specials OnChip DC-DC Converter, connect external application support, digital encoder UART, 1.3 Mbyte int. RAM, <1W

Integrated µC Integrated μC Integrated μC Integrated µC 2 integrated PHYs, Pin Controller support, 105 °C operating temperature

(ARM Cortex M4-100MHz) CPU), interfaces (EnDat, BiSS, others, typical incl. 2 PHYs

(ARM9-200MHz) (ARM9-100MHz) (ARM9-100MHz) (ARM9-200MHz) integrated 1.2V regulator security option, functional safety support, Functional safety

Additional integrated Application One chip solution for various etc.),

support, Cortex-R4F support

Controller applications, Functional safety support,

(450/600MHz), Cortex-M3

(ARM Cortex M4 - 100 MHz) Functional safety support, Cortex-R52 Dual (800MHz) cores

(150MHz) cores

Cortex-R52 (400MHz) core

Further information https://www.hilscher.com/netx https://www.hilscher.com/netx https://www.hilscher.com/netx https://www.hilscher.com/netx https://www.hilscher.com/netx www.microchip.com/design-centers/ethernet/ethernet-devices/products/ethercat www.renesas.com/en-eu/ec-1 www.renesas.eu/products/mpumcu/rz/index.jsp www.renesas.com/rzn2l www.renesas.com/rzt2m www.renesas.eu/automation www.renesas.com/products/microcontrollers-microprocessors/rx-32-bit-performance-efficiency-mcus/rx72m-high-performance-32-bit-microcontroller-industrial-network-solutions

Data Sheet https://www.hilscher.com/fileadmin/cms_upload/en-US/Resources/pdf/netX-100-500_Datasheet_10-2009_GB.pdf https://www.hilscher.com/fileadmin/cms_upload/en-US/Resources/pdf/netX-51_Datasheet_11-2014_GB.pdf https://www.hilscher.com/fileadmin/cms_upload/en-US/Resources/pdf/netX-52_Datasheet_11-2014_GB.pdf https://www.hilscher.com/fileadmin/cms_upload/en-US/Resources/pdf/netX-90_Datasheet_10-2019_GB.pdf https://www.hilscher.com/fileadmin/cms_upload/en-US/Resources/pdf/netX-100-500_Datasheet_10-2009_GB.pdf www.microchip.com/wwwproducts/en/LAN9252 https://www.renesas.com/en-eu/doc/products/mpumcu/doc/rz/r01ds0289ej0100-ec-1.pdf www.renesas.eu/products/mpumcu/rz/Documentation.jsp https://www.renesas.com/us/en/document/dst/rzn2l-group-datasheet https://www.renesas.com/us/en/document/dst/rzt2m-group-datasheet www.renesas.eu/r-in www.renesas.com/document/dst/rx72m-group-datasheet-rev111?r=1054481

*configurable

Trademarks and Patents

EtherCAT® is a registered trademark and patented technology, licensed by Beckhoff Automation GmbH, Germany. Other designations used in this publication may be trademarks whose use by third parties for their own purposes could violate the rights of the owners.

Note: Subject to technical modifications; no responsibility is accepted for the accuracy of this information. The content of all entries within the ESC overview is submitted by ETG members themselves. The ETG members are in charge of sales and support of their products as well as for the content of their entries. ETG therefore disclaims any liability for information contained therein.

EtherCAT SubDevice Controller Overview (3/3)

as of Oct 2023

C2000™

Name ANTAIOS TRITON Sitara AMIC110 SoC Sitara AM3357/9 Sitara AM4377/9 Sitara AM571xE Sitara AM572xE Sitara AM65x SoC Sitara AM64x SoC Sitara AM243x SoC Sitara AM263x SoC

(TMS320F28388D/S)

TI C28x subsystem(s) with ARM

Type ARM MPU ARM MPU ARM MPU ARM MPU ARM MPU ARM MPU ARM MPU ARM MPU ARM MPU ARM MCU ARM MCU

Connectivity Manager

Supplier

441-pin FCBGA 0.8mm pitch /

TFBGA-380 (0.65 mm pitch) 337 BGA 0.8mm pitch 324-pin NFBGA 324-pin NFBGA 491-pin NFBGA, 0.65mm pitch 760-pin FCBGA 760-pin FCBGA 784-pin S-PBGA 441-pin FCBGA 324-pin NFBGA

Package FCBGA-784 (0.8 mm pitch) 293-pin FCCSP 0.5mm pitch via

TFBGA-385 (0.8 mm pitch) 176 QFP 0.5mm pitch 0.8mm pitch 0.8 mm pitch (0.8 mm effective routing) 0.8 mm pitch 0.8 mm pitch 0.8mm pitch 0.8mm pitch 0.8mm pitch

channel array

15 mm x 15 mm 16 x16 mm 17.2mmx17.2mm /

Size 23 mm x 23 mm 15x15mm 15 x 15 mm 17 x 17 mm 23 x 23 mm 23 x 23 mm 23mmx23mm 17.2mmx17.2mm 15mmx15mm

19 mm x 19 mm 26 x 26 mm 11mmx11mm

250MHz interconnect (internal,

SPI / QSPI / 16 Bit asynchronous SPI / QSPI / 16 Bit asynchronous 200MHz interconnect (internal, 200 MHz interconnect 200 MHz interconnect 200 MHz interconnect 200 MHz interconnect 250MHz interconnect 250MHz interconnect 200MHz interconnect (internal,

µC Interface 16-bit async PDI interface 128bit),

interface interface 32bit) (internal, 32bit) (internal, 32bit) (internal, 32bit) (internal, 32bit) (internal, 256bit) (internal, 128bit) 64bit)

SPI (external)

Digital I/O 26Bits Input, 20Bits Output 32Bits Input, 22Bits Output N/A 8 8 8 8 8 8 8 8 8

General Purpose I/O up to 32 up to 32 32 >32 > 32 > 32 > 32 > 32 >32 >32 >32 >32

DPRAM up to 64 kByte up to 64 kByte 16 kByte 8 kByte 8 kByte 28 kByte 28 kByte 28 kByte 60 kByte 60 kByte 60 kByte 28 kByte

SyncManager Entities 8 8 8 8 8 8 8 8 8 8 8 8

FMMU Entities 8 8 8 8 8 8 8 8 8 8 8 8

Distributed Clock Support yes (64 bit) yes (64 bit) yes yes yes yes yes yes yes yes yes yes

No. of Ports 2 (100BaseTX) or 2 (MII) 4 Gbit Ethernet port 2 (MII) 2 (MII) 2 (MII) 2 (MII) 2 (MII) 2 (MII) 2 (MII) 2 (MII) 2 (MII) 2 (MII)

Entire ESC can be implemented

Entire ESC can be implemented Entire ESC can be implemented

Multi fieldbus protocol support, on internal memory (no external

Multi fieldbus protocol support, 2 on internal memory (no external on internal memory (no external

2 x integrated PHYs, EtherCAT slave enabled real-time DDR needed), Dual Gigabit

port Real-Time Ethernet switch with DDR needed), 3x Gigabit DDR needed), Dual Gigabit

1 x integrated GBit Ethernet controller. Up to 925 MIPS. Dual Industrial Communications Industrial Communications

integrated PHYs, Industrial Communications Industrial Communications Entire EtherCAT slave controller

MAC, Integrated ARM® Cortex®- Single or dual C28x + CLA control Subsystem (PRU-ICSS) for multi- Dual Industrial Communications Subsystem (PRU_ICSSG) for multi-

2x integrated GBit Ethernet MAC,3 Subsystem (PRU_ICSSG) for multi- Subsystem (PRU_ICSSG) for multi- can be implemented on internal

A5 (288MHz), Backplane Integrated ARM® Cortex®-A17 subsystems for real-time control Multi-protocol support, protocol support (2 EtherCAT Subsystem (PRU-ICSS) for multi- protocol support (2 EtherCAT

Entire EtherCAT slave controller protocol support (up to 3 protocol support (2 EtherCAT memory, Industrial

communication: SliceBus master (1.26GHz), Secure Core, Backplane loops. Arm based Connectivity Industrial Communications Second PRU-ICSS for Motor slave instances or EtherCAT slave protocol support (2 EtherCAT slave instances or EtherCAT slave

can be implemented on internal EtherCAT slave instances), slave instances or EtherCAT slave Communications Subsystem

for profichip’s SNAP+ ASIC, communication: SliceBus master for Manager for communictions and Subsystem (PRU-ICSS) control (EnDat, sigma delta to protocol gateway), Motor slave instances or EtherCAT slave to protocol gateway), PRU_ICSSG

memory (no external DDR PRU_ICSSG also supports Motor to protocol gateway), PRU_ICSSG (PRU_ICSS), PRU_ICSS also

Integrated technology module profichip’s SNAP+ ASIC, Integrated host control. On-chip flash, RAM, for multi-protocol support, filtering etc), Gigabit Switch, control (EnDat, sigma delta to protocol gateway), 2D/3D also supports Motor Control

Specials needed), Industrial Control functionality (Encoder also supports Motor Control supports Motor Control

(2xSII / 4xPWM / 4xCounter), technology module (2xSII / 4xPWM / 4x 16-bit ADC, SDFM, 32-ch Gigabit Switch, CAN, display, CAN, Display subsystem, 2D/3D filtering), 2D/3D Graphics, Graphics, Display subsystem, functionality (Encoder feedback

4xCounter), QuadSPI interface (e.g. Communications Subsystem feedback such as Hiperface-DSL functionality (Encoder feedback functionality (Encoder feedback

QuadSPI interface (e.g. NOR PWM, analog comparator ARM Cortex-A8 graphics, Camera I/F, Optional Display subsystem, Video Video acceleration, PCIe, SATA, such as Hiperface-DSL and EnDat

NOR Flash for firmware), DDR4 (PRU-ICSS) for multi-protocol and EnDat and Sigma Delta such as Hiperface-DSL and EnDat such as Hiperface-DSL and EnDat

Flash for firmware), DDR2 subsystem, multiple (275MHz-1000MHz) secure boot, ARM Cortex-A9 acceleration, PCIe, SATA, Optional secure boot, 2x ARM and Sigma Delta filtering), up to

external memory interface, 3 PCI support, CAN filtering), up to 4x Arm Cortex- and Sigma Delta filtering), up to and Sigma Delta filtering), up to

external memory interface, communications ports, (upto 1 GHz) Optional secure boot, ARM Cortex-A15 (upto 1.5 GHz), 2x 4x Arm Cortex-R5F cores at

Express® Controller, Other external A53 cores at 1.1GHz, 2x Cortex- 4x Arm Cortex-R5F cores at 4x Arm Cortex-R5F cores at

Other external interfaces: configurable logic block for Cortex-A15 (upto 1.5GHz), 2x M4 M4 cores, 2x C66x DSP cores 800MHz, up to 2x Cortex-A53

interfaces: 3 SD/MMC, NAND, USB2 R5F core at 400MHz with 800MHz, 1x Cortex-M4 core at 400MHz, 2MB on-chip SRAM

SD/MMC, NAND, USB2 device, device, SRAM master/slave, SPI

CPLD/FPGA replacement and cores, 1x C66x DSP core cores at 1GHz, 1x Cortex-M4

optional lock-step for functional 400MHz for functional safety or

SRAM master/slave, SPI master/slave absolue encoder support. core at 400MHz for functional

safety or other purposes, 2MB other purposes, 2MB on-chip

master/slave safety or other purposes, 2MB

on-chip SRAM SRAM

on-chip SRAM

Further information https://www.yaskawa.eu.com/products/profichip/productdetail/product/antaios_974 https://www.yaskawa.eu.com/products/profichip/productdetail/product/triton_9946 www.ti.com/product/tms320f28388d www.ti.com/amic110 www.ti.com/AM335x www.ti.com/AM437x www.ti.com/product/AM5718 www.ti.com/product/AM5728 www.ti.com/product/am6548 www.ti.com/product/am6442 www.ti.com/product/am2434 www.ti.com/product/am2634

Data Sheet https://www.yaskawa.eu.com/products/profichip/productdetail/product/antaios_974 https://www.yaskawa.eu.com/products/profichip/productdetail/product/triton_9946 www.ti.com/lit/gpn/tms320f28388d http://www.ti.com/product/AMIC110/datasheet www.ti.com/lit/ds/symlink/am3359.pdf www.ti.com/lit/ds/symlink/am4379.pdf www.ti.com/lit/ds/symlink/am5718.pdf www.ti.com/lit/ds/symlink/am5728.pdf http://www.ti.com/product/am6548/datasheet http://www.ti.com/product/am6442/datasheet http://www.ti.com/product/am2434/datasheet http://www.ti.com/product/am2634/datasheet

*configurable

Trademarks and Patents

EtherCAT® is a registered trademark and patented technology, licensed by Beckhoff Automation GmbH, Germany. Other designations used in this publication may be trademarks whose use by third parties for their own purposes could violate the rights of the owners.

Note: Subject to technical modifications; no responsibility is accepted for the accuracy of this information. The content of all entries within the ESC overview is submitted by ETG members themselves. The ETG members are in charge of sales and support of their products as well as for the content of their entries. ETG therefore disclaims any liability for information contained therein.

You might also like

- Security+ Cheat SheetDocument54 pagesSecurity+ Cheat SheetSourabh Chowdhury100% (1)

- RCD 2010 GillesaniaDocument223 pagesRCD 2010 GillesaniaMatt Julius CorpuzNo ratings yet

- PWM DCDocument2 pagesPWM DCĐỗ Xuân BằngNo ratings yet

- TH350B, TH355B, and TH360B Electrical System TelehandlerDocument2 pagesTH350B, TH355B, and TH360B Electrical System TelehandlerMohamed Harb100% (1)

- BS en Iec 63327-2021Document44 pagesBS en Iec 63327-2021damaso taracena75% (4)

- Cat12k ElectricoDocument2 pagesCat12k ElectricoAlexis CentuNo ratings yet

- Caterpillar Curso de HidraulicaDocument2 pagesCaterpillar Curso de Hidraulicamisaelandres1100% (1)

- Diagrama Eléctrico Tractor D4GDocument4 pagesDiagrama Eléctrico Tractor D4GRimbertNo ratings yet

- Oil City Division: Rev. Description Date BY CH'KDocument1 pageOil City Division: Rev. Description Date BY CH'KHendrias ari sujarwoNo ratings yet

- Epec 2023 Control Module PDFDocument40 pagesEpec 2023 Control Module PDFमुकेश कुमार झाNo ratings yet

- Asimov Frankenstein ComplexDocument6 pagesAsimov Frankenstein Complexkatgirl999No ratings yet

- Qj241 Jaw Crusher: Engineering in MotionDocument2 pagesQj241 Jaw Crusher: Engineering in MotionA2 BUDNo ratings yet

- Drive Technology, Automation, and System Integration ServicesDocument1 pageDrive Technology, Automation, and System Integration Servicesmarius_brkt6284No ratings yet

- Horizon AFC 564A 566ADocument6 pagesHorizon AFC 564A 566AKBR Graphics CanadaNo ratings yet

- 1 Overview: STC8A8K64S4A12 Series ManualDocument18 pages1 Overview: STC8A8K64S4A12 Series Manualhossein gholamiNo ratings yet

- Server RackDocument7 pagesServer Racksys2uNo ratings yet

- Motorola V3 1Document3 pagesMotorola V3 1Techno Max IT SolutionsNo ratings yet

- 10-011-01 NEC DS ENG SV8100 Communications ServerDocument2 pages10-011-01 NEC DS ENG SV8100 Communications ServerDavid YangNo ratings yet

- Block DiagramDocument5 pagesBlock Diagramonurkirmizi86No ratings yet

- Fourth Floor: Drawing Title: Factory Name: Address: Date: Design & Drawing By: Checked By: Approved byDocument1 pageFourth Floor: Drawing Title: Factory Name: Address: Date: Design & Drawing By: Checked By: Approved byMunzurulKaderNo ratings yet

- Overveiw CNC Ver1.5 2021-06-07Document1 pageOverveiw CNC Ver1.5 2021-06-07Kien Nguyen TrungNo ratings yet

- qj341 Brochure English PDFDocument2 pagesqj341 Brochure English PDFZaché le JusteNo ratings yet

- GT S5360L Tshoo 7 PDFDocument51 pagesGT S5360L Tshoo 7 PDFCelublack CkNo ratings yet

- Horizon AF 406Document7 pagesHorizon AF 406KBR Graphics Canada0% (1)

- NPM-DX BrochureDocument4 pagesNPM-DX BrochureRahul SinghNo ratings yet

- Features General Description: Ht78Xx Series 500ma Tinypower LdoDocument9 pagesFeatures General Description: Ht78Xx Series 500ma Tinypower LdomessyaxNo ratings yet

- Presurizacion de GradasDocument13 pagesPresurizacion de GradasAndres Aguilar-MatamorosNo ratings yet

- qj241 Brochure EnglishDocument2 pagesqj241 Brochure EnglishRafaelDevNo ratings yet

- Fan - KDKDocument2 pagesFan - KDKmitra perkasa multigunaNo ratings yet

- Irobot Catalogue Glance PDFDocument2 pagesIrobot Catalogue Glance PDFsekarNo ratings yet

- Robo 8718vg2aDocument1 pageRobo 8718vg2aHeli FirebladerNo ratings yet

- S5360 Block Diagram: 8. Level 3 RepairDocument51 pagesS5360 Block Diagram: 8. Level 3 RepairSLK srilankaNo ratings yet

- Instructions and Cautions For Safe Use of AC Servos: General-Purpose AC Servo CautionDocument1 pageInstructions and Cautions For Safe Use of AC Servos: General-Purpose AC Servo CautiontadyNo ratings yet

- G41MXE Support ListDocument7 pagesG41MXE Support ListIng. Christopher R. Pérez P.No ratings yet

- EX3G HMI PLC All-In-One User ManualDocument2 pagesEX3G HMI PLC All-In-One User ManualSeferino CampazNo ratings yet

- EX3G HMI PLC All-in-One User Manual: Compact Automation Controller with Integrated HMIDocument2 pagesEX3G HMI PLC All-in-One User Manual: Compact Automation Controller with Integrated HMIKarim NasriNo ratings yet

- MMT Ed2 01 PC FX 0003 - 0Document1 pageMMT Ed2 01 PC FX 0003 - 0Thalles ResendeNo ratings yet

- RTN 900 Product Family PosterDocument1 pageRTN 900 Product Family PosterAung Aung OoNo ratings yet

- Kafd A2 410 SHP Hom Reg 00001 R04Document36 pagesKafd A2 410 SHP Hom Reg 00001 R04md afaque rahmatNo ratings yet

- Esa08f A12f G2422 EngDocument2 pagesEsa08f A12f G2422 EngStanisław ZakrzewskiNo ratings yet

- ANT Block Diagram CurrentDocument1 pageANT Block Diagram CurrentGurinderjeet SinghNo ratings yet

- Dump Truck 773E (BDA259-485)Document2 pagesDump Truck 773E (BDA259-485)Marwan SahendraNo ratings yet

- 145B58(QTY=8NOS)]-ModelDocument1 page145B58(QTY=8NOS)]-ModelDass MNo ratings yet

- 90usb646 647 1286 1287Document435 pages90usb646 647 1286 1287Sorin AlexandruNo ratings yet

- Diagrama de Bloco: Micro System Bs 333Document4 pagesDiagrama de Bloco: Micro System Bs 333Felipe silva santanaNo ratings yet

- Ireless Communications Standards: Test and Measurement Solutions For Every Aspect of Wireless CommunicationsDocument2 pagesIreless Communications Standards: Test and Measurement Solutions For Every Aspect of Wireless Communicationsa hNo ratings yet

- Lc60 70le650ua PWB UnitDocument30 pagesLc60 70le650ua PWB UnitLeonel F. CamarilloNo ratings yet

- User'S Guide: JY992D50401EDocument6 pagesUser'S Guide: JY992D50401Evuitinhnhd9817No ratings yet

- Ex4 01 - SISDocument2 pagesEx4 01 - SISMario Quinteiro0% (1)

- Nokia 6233 rm-145 6234 rm-123Document10 pagesNokia 6233 rm-145 6234 rm-123me academyNo ratings yet

- Taae Rce 11 09 2022Document22 pagesTaae Rce 11 09 2022Orbenson TanNo ratings yet

- Electrical System 793D Off-Highway Truck: Harness and Wire Electrical Schematic SymbolsDocument4 pagesElectrical System 793D Off-Highway Truck: Harness and Wire Electrical Schematic SymbolsJose luis ConsuegraNo ratings yet

- UENR2643UENR2643-05 - SIS Electrico Diagrama PDFDocument4 pagesUENR2643UENR2643-05 - SIS Electrico Diagrama PDFJaime LopezNo ratings yet

- Sistema Eletrico 226Document4 pagesSistema Eletrico 226f8ytws84csNo ratings yet

- Jak1 Aur El DWG A 0 9030 (D)Document1 pageJak1 Aur El DWG A 0 9030 (D)Budi HahnNo ratings yet

- Third Floor: 08 Neelnagar, Konabari, GazipurDocument1 pageThird Floor: 08 Neelnagar, Konabari, GazipurMunzurulKaderNo ratings yet

- MPS DatasheetDocument2 pagesMPS DatasheetrajendrasoloniNo ratings yet

- Techdeal$ Pte LTD: #04-17 & #04-69 Sim Lim Square, Singapore 188504Document4 pagesTechdeal$ Pte LTD: #04-17 & #04-69 Sim Lim Square, Singapore 188504JayNo ratings yet

- Service Manual: KDC-6047U KDC-BT60U/BT945U/MP745U KDC-X7016/X7016L/X794 KDC-X8016BT/X8016BTL/X994Document15 pagesService Manual: KDC-6047U KDC-BT60U/BT945U/MP745U KDC-X7016/X7016L/X794 KDC-X8016BT/X8016BTL/X994luispider74No ratings yet

- Samsung Mm-E320 SCHDocument8 pagesSamsung Mm-E320 SCHCarlos EsparzaNo ratings yet

- A Video Controller for an FPGA ProjectDocument57 pagesA Video Controller for an FPGA ProjectCharbel TadrosNo ratings yet

- Cambridge-Audio Azur 640t-V2 Service enDocument22 pagesCambridge-Audio Azur 640t-V2 Service enChris YorkNo ratings yet

- Rsag7.820.4614 PSDocument1 pageRsag7.820.4614 PSvasul.denusNo ratings yet

- Radio Frequency Identification and Sensors: From RFID to Chipless RFIDFrom EverandRadio Frequency Identification and Sensors: From RFID to Chipless RFIDNo ratings yet

- K3765 K4505 Issues Troubleshooting Guide 1Document8 pagesK3765 K4505 Issues Troubleshooting Guide 1Makhful AdhimNo ratings yet

- MATH042 - Lesson 8Document16 pagesMATH042 - Lesson 8Yukimura SanadaNo ratings yet

- Uc 1823Document13 pagesUc 1823Mauricio Fernando BaezNo ratings yet

- Roll Number 301644: Ukssv %& VH FKHZ Izr SD Iz'U I GSRQ Vyx&Vyx Izos'K I E Miflfkfr I Mkmuyksm DjsaaDocument1 pageRoll Number 301644: Ukssv %& VH FKHZ Izr SD Iz'U I GSRQ Vyx&Vyx Izos'K I E Miflfkfr I Mkmuyksm DjsaaPushpendra BiwalNo ratings yet

- Technical Manual Weight Indicator: E-Lw: Software For Continuous Dosage in Unloading With Flow AdjustmentDocument103 pagesTechnical Manual Weight Indicator: E-Lw: Software For Continuous Dosage in Unloading With Flow AdjustmentValentin MaricaNo ratings yet

- Image Sensor Kmpd0002eDocument52 pagesImage Sensor Kmpd0002eLakmal GayanNo ratings yet

- Sets PythonDocument20 pagesSets Pythonrbharati078No ratings yet

- Farmbot SynopsisDocument10 pagesFarmbot SynopsisTanvi Khurana100% (2)

- IRF9520 Power MOSFET DatasheetDocument9 pagesIRF9520 Power MOSFET DatasheetBuho FielNo ratings yet

- Using Goal SeekDocument5 pagesUsing Goal SeekZahra ZahidNo ratings yet

- Deal Maven Excel ShortcutsDocument4 pagesDeal Maven Excel Shortcutschuff6675No ratings yet

- Hotel Sales OfficeDocument14 pagesHotel Sales OfficeAgustinus Agus PurwantoNo ratings yet

- GAMESHARK DIGIMON WORLD 2 Games GuidesDocument20 pagesGAMESHARK DIGIMON WORLD 2 Games GuidesWanwan Agile TigerNo ratings yet

- Jay Dave Flowchart AssignmentDocument5 pagesJay Dave Flowchart Assignmentapi-225496804No ratings yet

- Answers Student Text: UNIT 1 Decimals and FractionsDocument4 pagesAnswers Student Text: UNIT 1 Decimals and FractionsChristineNo ratings yet

- Tampermonkey Autorefresh-1Document2 pagesTampermonkey Autorefresh-1JOSENo ratings yet

- Pws 005311 EmersonDocument4 pagesPws 005311 EmersonSiddharthJoshiNo ratings yet

- School FormDocument2 pagesSchool FormBngrc Mrtnz Edn100% (1)

- Fejer Kernel PDFDocument2 pagesFejer Kernel PDFVictorNo ratings yet

- FEM 1D FormulationDocument39 pagesFEM 1D FormulationJORGE FREJA MACIASNo ratings yet

- Udemy Business Course ListDocument74 pagesUdemy Business Course ListPavel Ludert CharmeloNo ratings yet

- Philips 32PFL3404 FuenteDocument1 pagePhilips 32PFL3404 FuenteMatias IbañezNo ratings yet

- Inverse Nichols Chart ProblemDocument5 pagesInverse Nichols Chart ProblemKgotsofalang Kayson Nqhwaki0% (1)

- Introduction To Nonlinear Control Lecture # 4 PassivityDocument69 pagesIntroduction To Nonlinear Control Lecture # 4 PassivityZain BhattiNo ratings yet

- TeklaStructures License Agreement EnuDocument5 pagesTeklaStructures License Agreement EnuLev Maravi MandujanoNo ratings yet

![145B58(QTY=8NOS)]-Model](https://imgv2-2-f.scribdassets.com/img/document/724939431/149x198/c6f52ea33e/1713620215?v=1)