Professional Documents

Culture Documents

Noise Voltage - Text

Noise Voltage - Text

Uploaded by

Shivam Gauns0 ratings0% found this document useful (0 votes)

1 views3 pagesCopyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

1 views3 pagesNoise Voltage - Text

Noise Voltage - Text

Uploaded by

Shivam GaunsCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 3

NOISE VOLTAGE OBJECTIVES.

Since noise problems in digital logic produce marginal performance, proper

operation of z lab model or protorype system is not enough to guarantee @

reliable Gesign. [n addition to proper operation the following measurements

should be made: (1) ground noise voltage and (2) power-supply noise

voltage.

The best method for determining the quality of the power and ground

system on 9 printed wiring board is to measure the peak-differential ground.

noise voltage between various points on the bourd, and also the V,,

ground voltage on each IC.

Although many digital devices will work with ground noise differentials

as large as 1 V (Motorola Application Note AN-707), operational margins

and reliability may well be compromised. Therefore every effort should be

made to limit the peak-differential ground voltage to SU0mV or less.

Experience has shown that this can be achieved with s ground grid or plane

A well-designed grid system can hold the peak-

—

(CURRENT,

GARAYING

CONDUCTOR

8

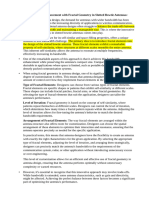

Figure 10.10, Tost ot up to mzarare the volhage drop betwen points A end B an a curren!

erring condurior (A) Tes: lee pale! eurtenvcnnrsing comelactor pick up au erat vali

tue to the carrenecrrsing conductor's magnetic jeld. (1B) Tes leads perpenaialar to ear

earning conducior do net pick up at errr voltae

MEASURING NOISE VOLTAGES

When measuring digital logie noise voltages consideration must be given to

(1) the bandwidth of the measuring instrumentation, (2) the high-frequency

common-mode rejection ratio (CMRR) of the instrumentation, and (3) the

dress of the leads trom the measuring instrument to the circuit under test

Nowe measurements must be made with a wide-bandwidth oscilloscope

(100 MHz. minimum, with 20) MHz preferred) and with a wide-bandwidth

differential probe with a good high-frequency CMRR (100 to 1 at 100 MHz

Logic FAMILIES 235

or better; ¢.g., Tektronix P6046 Active Differential Probe). ‘This type of

differential probe has high common-mode rejection at high frequencies

because it performs the common-mode rejection within the probe body and

then transmits the sional back to the single-ended oscilloscope. Instrumenta-

tion with large bandwidth and large CMRR is required to measure the

high-frequency components of the noise pulses.

Equal length leads should be connected to the two terminals of the

Aifferential probe. These leads should be dressed perpendicular to the

circuit board to minimize the inductive coupling between the conductors on

the board and the test leads (Paul, 1986; also Skilling, 1951, pp. 103-105).

Figure 10-10 shows two methods of measuring the voltage between points A

and B of @ current-carrying conductor. Figure 10-104 shows an incorrect

setup, and Fig, 10-108, a correct one. When the test leads are ran close 10.

and parallel with, the curtent-carrying conductor (Fig. 10-10A), the mag-

netic field from the conductor encircles the test leads, thereby coupling a

fe into the leads. When the leads are perpendicular fo the conductor 4s

10-10 coupling does not occur, Ideally the leads should be perpen-

dicular to the conductor for a great distence, to minimize the coupling,

Normally the test leads are routed perpendicular to the conductor for at

least Sem

If differential probe is not available. measurements can be made with i

wide-bandwidth, single-ended probe and scope, provided the circuit ean be

floated (with no gronnd connection) and powered from 2 battery. This way

the only ground on the circuit will be the ground connection of the seope,

and common-mode problems will be minimized, The routing of the test

Teads should be done in the way previously discussed.

UNUSED INPUTS

To prevent unintentional switching and aoise generation, all unused inputs

must be connected somewhere, and not lef open. Otherwise, a floating

input, picking up noise, may cause a gate to switch randomly. ‘This connec

tion is especially important for CMOS because of its high input impedance,

but applies to other logic families as well. In addition, for CMOS circuits, an

unused gate whese inputs are not connected may, hecause of noise, bias

itself into the linear region and significantly increase the ée current drawn by

the circuit, The unused inputs are normally connected to V., voltage through

2 series resistor, or to ground,

LOGIC FAMILIES

‘The principles discussed in this chapter are independent of logic families

‘They can be applied to TIL, STTL, LSTTL, CMOS, HCMOS. FAST.

ALS. ACL. and ECL. ‘The most important parameters are the rise/fall time

296 10 + OIGITAL GICUIT NOISE AND LAYOUT

and the magnitude of the trensient switching current. The faster the rise/all

time and the greater the transient current, the more important the principles

discussed here ate. For exemple, poor grounds and improper decoupling can

often be tolerated, although they should not be encouraged, in the case 0:

slow-speed CMOS when the rise! fell times are 30 to S0 ns, When rise times

are under Ins, however, these principles are very important

With the many different logic technologies available today, designers

should resist the temptation to use the fastest logic available. Instead, ihe

slowest- and lowest-power logic family that ean do the job should be used,

¢ noise and interference.

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5819)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1092)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (845)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (540)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (348)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (822)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- Emi Emc 07 11 2023 22mia004Document18 pagesEmi Emc 07 11 2023 22mia004Shivam GaunsNo ratings yet

- RF Communication SystemDocument2 pagesRF Communication SystemShivam GaunsNo ratings yet

- Bow-Tie Antenna in USNDocument6 pagesBow-Tie Antenna in USNShivam GaunsNo ratings yet

- Water PropertiesDocument5 pagesWater PropertiesShivam GaunsNo ratings yet

- P6248 1.7 GHZ (Typical) Differential Probe Service ManualDocument55 pagesP6248 1.7 GHZ (Typical) Differential Probe Service ManualShivam GaunsNo ratings yet

- Handout 07Document49 pagesHandout 07Shivam GaunsNo ratings yet

- BowTie Microstrip Antenna DesignDocument4 pagesBowTie Microstrip Antenna DesignShivam GaunsNo ratings yet

- Dielectric and Conduction Properties of Polyimide FilmsDocument4 pagesDielectric and Conduction Properties of Polyimide FilmsShivam GaunsNo ratings yet

- Bow-Tie Antenna For Underwater Wireless Sensor Networks (WSN)Document4 pagesBow-Tie Antenna For Underwater Wireless Sensor Networks (WSN)Shivam GaunsNo ratings yet

- Bode Plots Lecture Notes Study MaterialDocument9 pagesBode Plots Lecture Notes Study MaterialShivam GaunsNo ratings yet

- NotesDocument1 pageNotesShivam GaunsNo ratings yet

- GEC-ME - IndustrialAutomationAndRFDocument22 pagesGEC-ME - IndustrialAutomationAndRFShivam GaunsNo ratings yet

- ACHIEVE YOUR DREAM BrochureDocument4 pagesACHIEVE YOUR DREAM BrochureShivam GaunsNo ratings yet

- GEC M.E. Prospectus 2022-23Document41 pagesGEC M.E. Prospectus 2022-23Shivam GaunsNo ratings yet