Professional Documents

Culture Documents

Unidade Didática VI

Uploaded by

Ger MayCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Unidade Didática VI

Uploaded by

Ger MayCopyright:

Available Formats

SISTEMAS OPERACIONAIS

ESTA APOSTILA ABRANGER A UNIDADE DIDTICA VI DO PLANO DE ENSINO, ABORDANDO OS SEGUINTES ASSUNTOS: - Princpios Bsicos do hardware 1. Principios bsicos do Hardware a. Introduo Um computador digital constitudo por um conjunto de componentes interligados e composto por processadores, memria principal e dispositivos fsicos (hardware). Esses dispositivos manipulam dados na forma digital, o que proporciona uma maneira confivel de representao. Todos os componentes de um computador so agrupados em trs subsistemas bsicos: unidade central de processamento (UCP), memria principal, e dispositivos de entrada e sada. Estes subsistemas, tambm chamados de unidades funcionais, esto presentes em todo computador digital, apesar de suas implementaes variarem nas diferentes arquiteturas existentes e comercializadas pelos diversos fabricantes de computadores. b. Subsistemas bsicos 1) Unidade Central de Processamento A unidade central de processamento (UCP), ou processador, tem como funo principal unificar todo o sistema, controlando as funes realizadas por cada unidade funcional. A UCP tambm responsvel pela execuo de todos os programas do sistema, que obrigatoriamente devero estar armazenados na memria principal. Um programa composto por uma srie de instrues que so executadas sequencialmente pela UCP, atravs de operaes bsicas como somar, subtrair, comparar e movimentar dados. Desta forma, a UCP busca cada instruo na memria principal e a interpreta para sua execuo.

Sistemas Operacionais- UD VI- EAD FORTIUM

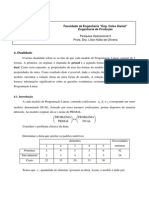

Esquema 1- Unidades Funcionais de um computador

A UCP composta por dois componentes bsicos: unidade de controle e unidade lgica aritmtica. A Unidade de controle (UC) responsvel por controlar as atividades de todos os componentes do computador, mediante a emisso de pulsos eltricos (sinais de controle) gerados por um dispositivo denominado clock. Este controle pode ser a gravao de um dado no disco ou a busca de uma instruo da memria. A unidade lgica e aritmtica (ULA), como o nome indica, responsvel pela realizao de operaes lgicas (testes e comparaes) e aritmticas (somas e subtraes). A especificao da velocidade de processamento de uma UCP determinada pelo nmero de instrues que o processador executa por unidade de tempo, normalmente segundos. Alguns fabricantes utilizam unidade de processamento prprias, j que no existe uma padronizao, sendo as mais comuns o MIPS (milhes de instrues por segundo) e o MFLOPS/GFLOPS (milhes/bilhes de instrues de ponto flutuante por segundo). A mostra alguns processadores e suas respectivas velocidades de processamento.

Esquema 2- Velocidade de Processamento de processadores

Sistemas Operacionais- UD VI- EAD FORTIUM

2) Clock O clock um dispositivo localizado na UCP que gera pulsos eltricos sncronos em um determinado intervalo de tempo (sinal de clock). A quantidade de vezes que este pulso se repete em um segundo define a freqncia do clock. O sinal de clock utilizado pela unidade de controle pare a execuo das instrues. A freqncia do clock de um processador medida em Hertz (Hz), que significa o nmero de pulsos eltricos gerados em um segundo de tempo. A freqncia tambm pode ser utilizada como unidade de desempenho entre diferentes processadores, sendo que quanto maior a freqncia, mais instrues podem ser executadas pela UCP em um mesmo intervalo de tempo. 3) Registradores Os registradores so dispositivos de alta velocidade, localizados fisicamente na UCP, para armazenamento temporrio de dados. O nmero de registradores varia em funo da arquitetura de cada processador. Alguns registradores so de uso especfico e tm propsitos especiais, enquanto outros so ditos de uso geral. Entre os registradores de uso especfico, merecem destaque: contador de instrues (CI) ou program counter (PC) e o registrador responsvel pelo armazenamento do endereo da prxima instruo que a UCP dever executar. Toda vez que a UCP execute uma instruo, o PC e atualizado com um novo endereo; o apontador da pilha (AP) ou stack pointer (SP) e o registrador que contm o endereo de memria do topo da pilha(*); o registrador de estado, tambm chamado em alguns equipamentos de program status word (PSW), o registrador responsvel por armazenar informaes sobre a execuo do programa, como a ocorrncia de carry e overflow. A cada instruo executada, o registrador de estado alterado conforme o resultado gerado pela instruo.

(*)-estrutura de dados onde o sistema mantm informaes sobre tarefas que estavam sendo processadas e tiveram que ser interrompidas por algum motivo

4) Memria Principal A memria principal, tambm conhecida como memria primria ou real, a parte do computador onde so armazenados instrues e dados. Ela composta por unidades de acesso chamadas clulas, sendo cada clula composta por um determinado nmero de bits (binary digit). O bit a unidade bsica de memria, podendo assumir o valor 0 ou 1. Atualmente, a grande maioria dos computadores utilize o byte (8 bits) como

Sistemas Operacionais- UD VI- EAD FORTIUM

tamanho de clula, porm encontramos computadores de geraes passadas com clulas de 16, 32 e at mesmo 60 bits. Podemos concluir, ento, que a memria formada por um conjunto de clulas, onde cada clula possui um determinado nmero de bits (Esquema 3).

Esquema 3- Memria Principal

O acesso ao contedo de uma clula realizado atravs da especificao de um nmero chamado endereo. O endereo uma referncia nica que podemos fazer a uma clula de memria. Quando um programa deseja ler ou escrever um dado em uma clula, deve primeiro especificar qual o endereo de memria desejado, pare depois realizar a operao. A especificao do endereo realizada atravs de um registrador denominado registrador de endereo de memria (memory register address - MAR). Atravs do contedo deste registrador a unidade de controle sabe qual a clula de memria que ser acessada. Outro registrador usado em operaes com a memria o registrador de dados da memria (memory buffer registerMBR) . Este registrador utilizado pare guardar o contedo de uma ou mais clulas de memria aps uma operao de leitura, ou para guardar o dado que ser transferido para a memria em uma operao de gravao. Este ciclo de leitura e gravao e mostrado no Esquema 4.

Esquema 4- Ciclo de Leitura e Gravao

Sistemas Operacionais- UD VI- EAD FORTIUM

A capacidade de uma memria limitada pelo tamanho do MAR. No caso do registrador possuir n bits, a memria principal poder no mximo enderear 2 x n clulas, isto , do endereo 0 ao 2n-1. A memria principal pode ser classificada em funo de sua volatilidade(*). As memrias volteis se caracterizam por poderem ser lidas ou gravadas e so conhecidas como RAM (random access memory). Constituem quase que a totalidade da memria principal de um computador. O outro tipo, chamado de no voltil, no permite alterar ou apagar seu contedo. Este tipo de memria conhecido como ROM (read-only memory), j vem prgravado do fabricante, geralmente com algum programa, e seu contedo preservado mesmo quando a alimentao desligada. Uma variao da ROM a EPROM (erasable programmable ROM), once podemos gravar e regravar a memria atravs de exposio de luz ultravioleta por um dispositivo especial. Atualmente, uma srie de memrias com diferentes caractersticas existem para diversas aplicaes, como a EEPROM, EAROM, EAPROM, NOVRAM entre outras.

(*)-capacidade da memria de preservar o seu contedo mesmo sem uma fonte de alimentao

5) Memria Cache A memria cache uma memria voltil de alta velocidade. O tempo de acesso a um dado nela contido muito menor que o da memria principal. Toda vez que o processador fez referncia a um dado armazenado na memria principal, ele "olha" antes na memria cache. Se o processador encontrar o dado na cache, no h necessidade do acesso memria principal; do contrrio, o acesso ser obrigatrio Neste ltimo caso, o processador, a partir do dado referenciado, transfere um bloco de dados para a cache. O tempo de transferncia entre as memrias pequeno, se comparado com o aumento do desempenho obtido com a utilizao desse tipo de memria. Apesar de ser uma memria de acesso rpido, seu uso limitado em funo do alto custo. O Esquema 5 mostra a relao entre as memrias cache e principal em alguns equipamentos.

Sistemas Operacionais- UD VI- EAD FORTIUM

Esquema 5- Relao entre as memrias cache e principal

6) Memria Secundria A memria secundria um meio permanente (no voltil) de armazenamento de programas e dados. Enquanto a memria principal precisa estar sempre energizada para manter suas informaes, a memria secundria no precisa de alimentao. O acesso a memria secundria lento, se comparado com o acesso a memria cache ou principal, porm seu custo baixo e sua capacidade de armazenamento bem superior a da memria principal. Enquanto a unidade de acesso a memria secundria da ordem de milissegundos, o acesso a memria principal de nanossegundos. Podemos citar, como exemplos de memrias secundrias, a fita magntica, o disco magntico e o disco ptico. O Esquema 6 mostra a relao entre os diversos tipos de dispositivos de armazenamento apresentados, comparando custo, velocidade e capacidade de armazenamento.

Esquema 6- Relao entre os diversos tipos de dispositivos de armazenamento

7) Dispositivos de Entrada e Sada Os dispositivos de entrada e sada (E/S) so utilizados para permitir a comunicao entre o computador e o mundo externo. Atravs desses dispositivos a UCP e a memria principal podem se comunicar, tanto com usurios quanto com memrias secundrias, a fim de realizar qualquer tipo de processamento.

Sistemas Operacionais- UD VI- EAD FORTIUM

Os dispositivos de E/S podem ser divididos em duas categorias: os que so utilizados como memria secundria e os que servem para a interface homem-mquina. Os dispositivos utilizados como memria secundria, como discos e fitas magnticas se caracterizam por armazenar de trs a quatro vezes mais informaes que a memria principal. Seu custo relativamente baixo, porm o tempo de acesso a memria secundria de quatro a seis vezes maior que o acesso a memria principal. Alguns dispositivos servem para a comunicao homemmquina, tais como teclados, monitores de vdeo, impressoras, plotters, entre outros. Com o avano no desenvolvimento de aplicaes de uso cada vez mais geral, procura-se aumentar a facilidade de comunicao entre o usurio e o computador. A implementao, de interfaces mais amigveis permite, cada vez mais, que pessoas sem conhecimento especfico sobre informtica possam utilizar o computador. Scanner, caneta tica, mouse, dispositivos sensveis a voz humana e ao calor do corpo humano so alguns exemplos desses tipos de dispositivos. 8) Barramento A UCP, a memria principal e os dispositivos de E/S so interligados atravs de canais de comunicao denominados barramentos, barras ou vias. Um barramento (bus) um conjunto de fios paralelos (linhas de transmisso), onde trafegam informaes, como dados, endereos ou sinais de controle(flags). Ele pode ser classificado como unidirecional (transmisso em um s sentido) ou bidirecional (transmisso em ambos os sentidos). Na ligao entre UCP e memria principal, podemos observar que trs barramentos so necessrios para que a comunicao seja realizada. O barramento de dados transmite informaes entre a memria principal e a UCP. O barramento de endereos utilizado pela UCP para especificar o endereo da clula de memria que ser acessada. Finalmente , o barramento de controle envia os pulsos de controle relativos as operaes de leitura e gravao. 9) Pipelining O conceito de processamento pipeline se assemelha muito a uma linha de montagem, onde uma tarefa dividida em uma seqncia de subtarefas, executadas em diferentes estgios, dentro da linha de produo.

Sistemas Operacionais- UD VI- EAD FORTIUM

Esquema 7- Configuraes de um sistema

Da mesma forma que em uma linha de montagem, a execuo de uma instruo pode ser dividida em subtarefas, como as fases de busca da instruo dos operandos, execuo e armazenamento dos resultados. O processador, atravs de suas vrias unidades funcionais pipeline, funciona de forma a permitir que, enquanto uma instruo se encontra na fase de execuo, ele possa estar na fase de busca simultaneamente. A tcnica de pipelining pode ser empregada em sistemas com um ou mais processadores, em diversos nveis, e tem sido a tcnica de paralelismo mais utilizada para maior desempenho dos sistemas de computadores. c. Ativao e desativao do Sistema O sistema operacional essencial para o funcionamento de um computador. Sem ele, grande parte dos recursos do sistema no estaria disponvel, ou se apresentaria de uma forma complexa para utilizao pelos usurios. Toda vez que um computador ligado, necessrio que o sistema operacional seja carregado da memria secundria para a memria principal. Esse processo, denominado ativao do sistema (boot), realizado por um programa localizado em um posio especifca do disco (disc block), geralmente o primeiro bloco. O procedimento de ativao varia em funo do equipamento, podendo ser realizado atravs do teclado, de um terminal ou por manipulao de chaves de um painel (Esquema 8).

Esquema 8- Ativao do sistema

Sistemas Operacionais- UD VI- EAD FORTIUM

Alm da carga do sistema operacional, a ativao do sistema tambm consiste na execuo de arquivos de inicializao. Nestes arquivos so especificados procedimentos de inicializao de hardware e software especficos para cada ambiente. Na maioria dos sistemas tambm existe o processo de desativao (shutdown). Este procedimento permite que as aplicaes e componentes do sistema sejam desativados de forma ordenada garantindo a integridade do sistema. d. Arquiteturas RISC e CISC Um processador com arquitetura RISC (Reduced Instruction Set Computer) se caracteriza por possuir poucas instrues de mquina, em geral bastante simples, que so executadas diretamente pelo hardware. Na sua maioria, estas instrues no acessam a memria principal, trabalhando principalmente com registradores que, neste tipo de processador, se apresentam em grande nmero. Estas caractersticas, alm de ajudarem as instrues serem executadas em alta velocidade, facilitam a implementao do pipeline. Como exemplos de processaores RISC podemos citar o Sparc (SUN), RS-6000 (IBM), PA-RISC (HP), Alpha AXP (DEC) e Rx000 (MIPS). Os processadores CISC (Complex Instruction Set computers) j possuem instrues complexas que so interpretadas por microprogramas. O nmero de registradores pequeno e qualquer instruo pode referenciar a memria principal. Neste tipo de arquitetura, a implementao do pipeline mais difcil. So exemplos de processadores CISC o VAX (DEC), 80x86 e o Pentium (Intel), e o 68xx (Motorola). Na prxima apostila falaremos dos princpios bsicos do software. At l e bons estudos!!

You might also like

- Aula 010Document10 pagesAula 010Ger MayNo ratings yet

- Aula 009Document11 pagesAula 009Ger MayNo ratings yet

- Modelo Iluminacao IDocument20 pagesModelo Iluminacao IGer MayNo ratings yet

- As 100 Palavras Mais Comuns Da Lingua InglesaDocument4 pagesAs 100 Palavras Mais Comuns Da Lingua InglesaSérgio CarvalhoNo ratings yet

- Seleção e Combinação Criativa de FontesDocument24 pagesSeleção e Combinação Criativa de FontesGer MayNo ratings yet

- Sorteios Aleatórios em JavaDocument5 pagesSorteios Aleatórios em JavaGer MayNo ratings yet

- Modo de Serviço de TV AiwaDocument18 pagesModo de Serviço de TV AiwaAlessandro PussenteNo ratings yet

- OasismontajTutorialnew v7.1 PortugueseDocument334 pagesOasismontajTutorialnew v7.1 PortugueseRobson AquinoNo ratings yet

- Matriz de ComunicaçãoDocument1 pageMatriz de ComunicaçãoAnderson Reimão100% (1)

- Inversor de Frequencia hd300 173Document2 pagesInversor de Frequencia hd300 173Rogerio Alves ResendeNo ratings yet

- Pesquisa BinariaDocument31 pagesPesquisa Binariacordeiro89No ratings yet

- Como Invadir TelegramDocument6 pagesComo Invadir TelegramDomNo ratings yet

- Apostila SketchUp 8Document103 pagesApostila SketchUp 8talesdaniel22No ratings yet

- Teoria Da Informação - ExercíciosDocument2 pagesTeoria Da Informação - ExercíciosHenrique BeloNo ratings yet

- Manual G31DM D2Document16 pagesManual G31DM D2Flávia Lima100% (1)

- MplsDocument6 pagesMplsJorge ValenteNo ratings yet

- Atualização e Configuração Manual Do Client-ServicesDocument1 pageAtualização e Configuração Manual Do Client-ServicesplastikliebeNo ratings yet

- Aula4 - DualidadeDocument15 pagesAula4 - DualidadeniltonsamaralNo ratings yet

- BCDocument24 pagesBCvinicusNo ratings yet

- Tutorial Working ModelDocument4 pagesTutorial Working ModelbenettiluanaNo ratings yet

- Guia MoodleDocument219 pagesGuia MoodleAnonymous pYEJQDTqNo ratings yet

- Implantação de Um Ambiente de Armazenamento em Nuvem Corporativo Utilizando A Ferramenta Livre Owncloud Aplicado No Parque Tecnológico ItaipuDocument13 pagesImplantação de Um Ambiente de Armazenamento em Nuvem Corporativo Utilizando A Ferramenta Livre Owncloud Aplicado No Parque Tecnológico ItaipuAirton Bordin JuniorNo ratings yet

- Cuidados Com A Consultavel (Evitar Bloqueio) Tropa Do 7-1Document2 pagesCuidados Com A Consultavel (Evitar Bloqueio) Tropa Do 7-1Ag Moura75% (4)

- Um MicrocontroladorDocument5 pagesUm MicrocontroladorOsvaldo PortoNo ratings yet

- TOP 10 Principais SGBDs Do Mercado GlobalDocument14 pagesTOP 10 Principais SGBDs Do Mercado GlobalCarlos Torres de FreitasNo ratings yet

- PortugolDocument23 pagesPortugolhermanherzel100% (1)

- Portfolio 01 - Pre-CalculoDocument8 pagesPortfolio 01 - Pre-CalculoHermann Pessoa0% (1)

- Função de Utilidade IndiretaDocument30 pagesFunção de Utilidade IndiretaDeborahrabelloNo ratings yet

- Erro - O Windows Explorer Parou de FuncionarDocument6 pagesErro - O Windows Explorer Parou de FuncionarJosé Henrique CruzNo ratings yet

- Aula 05 (Distribuição de Frequências)Document4 pagesAula 05 (Distribuição de Frequências)valdicleyNo ratings yet

- Parametros e SocialDocument11 pagesParametros e SocialRoberto LimaNo ratings yet

- Alguns Aspectos MatemáticosDocument2 pagesAlguns Aspectos Matemáticosth2013No ratings yet

- Cartão de Convocação Individual - Cci PDFDocument1 pageCartão de Convocação Individual - Cci PDFLucas HonoratoNo ratings yet

- Aula Labview 1Document12 pagesAula Labview 1Paulo Pereira Jr.No ratings yet

- Pmbok UnipDocument31 pagesPmbok UnipBruno HenriqueNo ratings yet