Professional Documents

Culture Documents

HSADC

Uploaded by

demostenessCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

HSADC

Uploaded by

demostenessCopyright:

Available Formats

1 2 3 4 5 6

A A

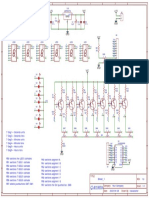

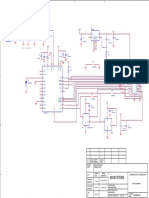

U3

+3V0 VCC

TPL740-3.0

5 1

VOUT VIN

C14

GND

C13 3

EN

0.1uF 0.1uF

2

R1 0 C12 1uF

GNDA

U2 3PA1030

GND

C9 C10 28 2

AVDD DVDD

+3V0 1uF 0.1uF

+3V0

B 23 17 B

C1 1uF MODE STBY

GNDA

R4 20

CLAMPIN GND

GNDA U1 19 16

6

18k CLAMP OE

5

3 TPH2501 J1

V+

+ PinPad2x8

DISABLE

1 R3 27 ADC_IN 27 13 D10

AIN OVR D0 1 16

R10 100K 4 12 D9

R2 - D9

V-

D1 2 15 GNDA

3.3k C7 21 11 D8

REFTS D8 D2 3 14 Vin

2

270pF 10 D7

D7 D3 4 13

25 9 D6

GNDA REFBS D6 D4 5 12 CLK

GNDA GNDA 8 D5

GNDA D5 D5 6 11 D10

26 7 D4

VREF D4 D6 7 10 D9

R5 10k 6 D3

D3 D7 8 9 D8

18 5 D2

C11 1p REFSENSE D2

C4 0.1uF 4 D1

C2 C6 D1

1uF 0.1uF 22 3 D0

C8 REFTF D0

0.1uF

24 15 CLK

REFBF CLK

C5 0.1uF

1 14

C AGND DGND C

GNDA

R9 0

GNDA GND

Using ADC from 3Peak

Designed by Gongyu Su

For national competition use

EETREE

Sheet: /

D File: HSADC.sch D

Title: 10bit/50Msps High Speed ADC Module

Size: A4 Date: 2020-09-12 Rev: V0.9

KiCad E.D.A. kicad (5.1.6)-1 Id: 1/1

1 2 3 4 5 6

You might also like

- Schematic 6502 Display 2023-05-31Document1 pageSchematic 6502 Display 2023-05-31Russell SherNo ratings yet

- FmradioDocument1 pageFmradiosiucarlos66No ratings yet

- esquematicoCIBDIC 1Document1 pageesquematicoCIBDIC 1Aklre KigoNo ratings yet

- S1G 915 CombinedDocument2 pagesS1G 915 CombinedDương LêNo ratings yet

- PowerSupply SDR SCH 20090522Document1 pagePowerSupply SDR SCH 20090522Hakim BenmajidNo ratings yet

- Akula Kacher Driver 1.3Document1 pageAkula Kacher Driver 1.3Osiris G.No ratings yet

- UDA1380 Board SchematicDocument1 pageUDA1380 Board SchematicasfafqwfwqNo ratings yet

- Vaula 274 WR Circuitry PDFDocument1 pageVaula 274 WR Circuitry PDFRiky GUNo ratings yet

- Vaula 274 WR Circuitry PDFDocument1 pageVaula 274 WR Circuitry PDFRiky GUNo ratings yet

- Schematic PDFDocument1 pageSchematic PDFMajk Stone100% (1)

- Subbu DAC SE V3 SchematicsDocument1 pageSubbu DAC SE V3 Schematicscristi289No ratings yet

- Assembly SchematicDocument1 pageAssembly Schematicmatt100% (2)

- Tme-Stm32F103 Dev. Board Tme-Stm32F103 Dev. Board Tme-Stm32F103 Dev. BoardDocument1 pageTme-Stm32F103 Dev. Board Tme-Stm32F103 Dev. Board Tme-Stm32F103 Dev. Boardbui thuyNo ratings yet

- Hold E - Out: GND GNDDocument2 pagesHold E - Out: GND GNDSheraz AhmedNo ratings yet

- Picprog CircuitDocument1 pagePicprog Circuitmiguel709100% (1)

- Complete Ultrasonic Driver CircuitDocument1 pageComplete Ultrasonic Driver CircuitEnrique Herrera100% (1)

- Snail Shield V2.1 SchematicDocument3 pagesSnail Shield V2.1 SchematicFernando GómezNo ratings yet

- 7343.TPA3116 SchematicDocument1 page7343.TPA3116 SchematicsrinivasanNo ratings yet

- S1G 915 SeparateDocument2 pagesS1G 915 SeparateDương LêNo ratings yet

- SB2040 SchematicDocument1 pageSB2040 Schematiccacalot93100% (1)

- Schematic - USDX MICRO v2.6Document1 pageSchematic - USDX MICRO v2.6luistorcatt72100% (1)

- Title: Dual Trace Oscilloscope: U5 ST7735s TFT ScreenDocument1 pageTitle: Dual Trace Oscilloscope: U5 ST7735s TFT ScreenAbdelkader Mechernene100% (2)

- Vin Vout: 1200Mhz VCO Mit MAX2754 Und 30W PADocument4 pagesVin Vout: 1200Mhz VCO Mit MAX2754 Und 30W PADUDULE100% (1)

- Schematic - Receptor Regenerativo 2 Fets - 2022!11!06Document1 pageSchematic - Receptor Regenerativo 2 Fets - 2022!11!06Doni SouzaNo ratings yet

- DiseqC SCHDocument1 pageDiseqC SCHnaseerak100% (2)

- Ciim00009 (DDC112) - DDC112Document2 pagesCiim00009 (DDC112) - DDC112ZXNo ratings yet

- Zed BULL SchematicDocument1 pageZed BULL SchematicAugustoferreira Ferreira100% (3)

- Usb GpsDocument2 pagesUsb Gpsla_vionexNo ratings yet

- Schematic Rover PCB1Document1 pageSchematic Rover PCB1Hassan AlviNo ratings yet

- MKR485ShieldV3.0 SCHDocument1 pageMKR485ShieldV3.0 SCHGa3iel100% (1)

- 100V-240V Woshine Machine Motor Driver-DiagrameDocument1 page100V-240V Woshine Machine Motor Driver-DiagrameWasantha MunasinghaNo ratings yet

- FlexDriver SDR SCH 20090522Document1 pageFlexDriver SDR SCH 20090522ami oreverNo ratings yet

- Dc-Cdi Atmel SCHDocument1 pageDc-Cdi Atmel SCHAdah BumboneNo ratings yet

- Component Ratings: Reflow & Lamp ControllerDocument1 pageComponent Ratings: Reflow & Lamp ControllerKeith Dobbelaere100% (4)

- PDF Created With Fineprint Pdffactory Trial Version: ZoudangDocument1 pagePDF Created With Fineprint Pdffactory Trial Version: ZoudangIgor MNo ratings yet

- Sol 1 2 Batt 1 2: 11/03/2020 7:17:07 CH C:/Users/Phamhung/Desktop/Mppt 10A/Eagle File - SCH (Sheet: 1/1)Document1 pageSol 1 2 Batt 1 2: 11/03/2020 7:17:07 CH C:/Users/Phamhung/Desktop/Mppt 10A/Eagle File - SCH (Sheet: 1/1)Mario MarcioNo ratings yet

- KNQ7 SchematicDocument1 pageKNQ7 SchematicFariborz SadeghivafaNo ratings yet

- 5V From +5V Power SuppyDocument1 page5V From +5V Power SuppySuny Khan100% (1)

- Blood Pressure Meter Schematic RevB PDFDocument4 pagesBlood Pressure Meter Schematic RevB PDFRene Gonzales Vasquez100% (2)

- Catalex-Micro-SD-Card-Module-SCH ModificadoDocument1 pageCatalex-Micro-SD-Card-Module-SCH ModificadoBabobrillNo ratings yet

- Schematic 24Vdc UPS v1.1Document1 pageSchematic 24Vdc UPS v1.1Nuaman SaghirNo ratings yet

- Micro ScheDocument1 pageMicro Schetradingview9339No ratings yet

- Schematic FL5150 Wifi Dimmer 2022-01-04Document1 pageSchematic FL5150 Wifi Dimmer 2022-01-04Naveen.R - SonetonixNo ratings yet

- Oneal Ocm250Document3 pagesOneal Ocm250JonnyNo ratings yet

- A350 Hyd PDFDocument16 pagesA350 Hyd PDFSaleh El DalyNo ratings yet

- DC-DC Step Down On XL4016Document1 pageDC-DC Step Down On XL4016Raghu Vutukuru100% (3)

- Ad7609 Module V1.0Document1 pageAd7609 Module V1.0bokic88No ratings yet

- original-schematic-STM32F411CEU6 WeAct Black Pill V2.0Document1 pageoriginal-schematic-STM32F411CEU6 WeAct Black Pill V2.0Max Pohl100% (1)

- KC868 A128 SchematicDocument13 pagesKC868 A128 SchematicMarek DužíNo ratings yet

- 逆变直流升压Document1 page逆变直流升压何青No ratings yet

- + - Speaker Output Audio InputDocument1 page+ - Speaker Output Audio InputTaufiq Safa'atkuNo ratings yet

- TarjetaDocument1 pageTarjetastarly ariza collNo ratings yet

- TPS3839G33DBZR U3 U1: Low PowerDocument1 pageTPS3839G33DBZR U3 U1: Low Powermarcoteran007No ratings yet

- Socl 506Document1 pageSocl 506IRAWAN SURYANATANo ratings yet

- Si4730 M Arduino Uno Share SCH OUGm8OO6SGDocument1 pageSi4730 M Arduino Uno Share SCH OUGm8OO6SGerpimperoNo ratings yet

- 11 Corrected Diy Soldering StationDocument1 page11 Corrected Diy Soldering StationСергей НикитинNo ratings yet

- Sic Driver Board SchematicDocument1 pageSic Driver Board Schematicluongktdt100% (2)

- TV On DVD-mst720-113Document3 pagesTV On DVD-mst720-113dann222No ratings yet

- Paso A PasaDocument1 pagePaso A PasaAlejandro Teruggi100% (1)

- Broadcast FM Radio Tuner For Portable Applications: Description FeaturesDocument3 pagesBroadcast FM Radio Tuner For Portable Applications: Description FeaturesdemostenessNo ratings yet

- KA2223 Balanço de TonDocument4 pagesKA2223 Balanço de TondemostenessNo ratings yet

- VU Meter Peak Hold Uno NanoDocument3 pagesVU Meter Peak Hold Uno NanodemostenessNo ratings yet

- 400pcs 1/4W Metal Film Resistor Assort Kit 20 Kinds Value 1% NewDocument1 page400pcs 1/4W Metal Film Resistor Assort Kit 20 Kinds Value 1% NewdemostenessNo ratings yet

- FM Transmitter System: Installation and User ManualDocument14 pagesFM Transmitter System: Installation and User ManualdemostenessNo ratings yet

- Usb U363Document6 pagesUsb U363demostenessNo ratings yet

- SB160 Schottky Diode 60V 1a PDFDocument3 pagesSB160 Schottky Diode 60V 1a PDFdemostenessNo ratings yet

- Datasheet IRFZ48Document9 pagesDatasheet IRFZ48demostenessNo ratings yet

- Tabela de VaristoresDocument4 pagesTabela de Varistoresdemosteness100% (1)

- Cross Référence MOSFETSDocument67 pagesCross Référence MOSFETSapi-26235400100% (1)

- Denah Lokasi Mess & Camp THN 2022 Ukuran 100 CM X 100 CMDocument2 pagesDenah Lokasi Mess & Camp THN 2022 Ukuran 100 CM X 100 CMnovalino raziNo ratings yet

- Mondorfer Bastelbogen - Rheidter WindmuehleDocument12 pagesMondorfer Bastelbogen - Rheidter WindmuehlePatrick Manalo100% (1)

- Las Bobinas Ing. Daniel Pérez LW1ECPDocument7 pagesLas Bobinas Ing. Daniel Pérez LW1ECPDiego García MedinaNo ratings yet

- Giddins - 101 Chess Endgame TipsDocument113 pagesGiddins - 101 Chess Endgame TipsLRNo ratings yet

- Summary - Naroditsky MethodDocument9 pagesSummary - Naroditsky MethodfcjjcfNo ratings yet

- Emaar Lucknow PlotDocument7 pagesEmaar Lucknow PlotShikhar SinghNo ratings yet

- Informe QueuesDocument19 pagesInforme QueuesJoseph Arafab Yapoleb PupunoVizchhNo ratings yet

- Chess ScrabbleDocument5 pagesChess Scrabbleannur90No ratings yet

- Nyc Rolling SalesDocument4,371 pagesNyc Rolling SalesCover SongNo ratings yet

- MAX8774Document1 pageMAX8774Tim O BrienNo ratings yet

- Chess - From Beginner To Advanced at Warp Speed Volume 2Document100 pagesChess - From Beginner To Advanced at Warp Speed Volume 2Cassidy VarneyNo ratings yet

- Victory in The OpeningDocument146 pagesVictory in The OpeningSarath Mohan100% (1)

- Abcdefgh Abcdefgh Abcdefgh: 1. ... Openings ... Openings 1. ... OpeningsDocument4 pagesAbcdefgh Abcdefgh Abcdefgh: 1. ... Openings ... Openings 1. ... Openingsabudu3a2No ratings yet

- Modern Chess Magazine 21Document109 pagesModern Chess Magazine 21Mauricio Abril Guiza100% (1)

- Adrian Mikhalchishin - Power of Exchange PDFDocument30 pagesAdrian Mikhalchishin - Power of Exchange PDFJerem Nowina KonopkaNo ratings yet

- The Instructor: An Historical Serial ContinuesDocument17 pagesThe Instructor: An Historical Serial ContinuesFuad AkbarNo ratings yet

- The Modern English Vol 2 - Kiril Georgiev 2columns PDFDocument234 pagesThe Modern English Vol 2 - Kiril Georgiev 2columns PDFazazel100% (6)

- Manual de Taller Video Home Cinema ThompsonDocument2 pagesManual de Taller Video Home Cinema ThompsonJosep LluisNo ratings yet

- Chess BookDocument64 pagesChess BookJo BatsNo ratings yet

- Four Pawns Attack Move OrderDocument2 pagesFour Pawns Attack Move OrderNiki MullinsNo ratings yet

- Agents of Edgewatch 2 Sixty Feet Under Interactive Mapspdf PDF FreeDocument6 pagesAgents of Edgewatch 2 Sixty Feet Under Interactive Mapspdf PDF FreeRafaelBiondoNo ratings yet

- Philips 32PFL3605D LCD Esquema Fonte Tv32pfl3605dDocument2 pagesPhilips 32PFL3605D LCD Esquema Fonte Tv32pfl3605dJeank RivadeneyraNo ratings yet

- Soltis & McCormick - The United States Chess Championship 1845-1996 PDFDocument243 pagesSoltis & McCormick - The United States Chess Championship 1845-1996 PDFjuan qu100% (1)

- Guitar Power Chords ChartDocument1 pageGuitar Power Chords ChartErick Stefano Kulcheski Alves De LimaNo ratings yet

- Kasparov PDFDocument16 pagesKasparov PDFGanesh HegdeNo ratings yet

- Latest B-Stars UPDATE 2021Document171 pagesLatest B-Stars UPDATE 2021Stanley RamirezNo ratings yet

- Thats The Way Love GoesDocument1 pageThats The Way Love GoesJeremy Cotton100% (1)

- World of RepertoireDocument8 pagesWorld of Repertoirechandra6865No ratings yet

- Bosch Jeroen - Pawn Chain and Kingside AttackDocument9 pagesBosch Jeroen - Pawn Chain and Kingside AttackRenukha PannalaNo ratings yet

- The Following Table Lists The 8051 Instructions by HEX CodeDocument5 pagesThe Following Table Lists The 8051 Instructions by HEX CodeBruce_Jass_3739No ratings yet