Professional Documents

Culture Documents

APznzaaw2ORoRWxw2cHZTrQf-nvEdq8ZfsRH-W2rtGqw_RKeH3M9CzsCp3TwStUDajWoxmHKcirqvkKVyo2Ii370FTuh54mC0M0jTkJYoauMeJ5l0JDriaZlR1VYy-BtO7LNlyx58f9W9hKM_Ux7N9SxJbds1Ds1aN2L2_0qu3ohubmH6EcbtFdk_HRcBP22i1vNgjiqLbrkav1iyHBVvdXu

APznzaaw2ORoRWxw2cHZTrQf-nvEdq8ZfsRH-W2rtGqw_RKeH3M9CzsCp3TwStUDajWoxmHKcirqvkKVyo2Ii370FTuh54mC0M0jTkJYoauMeJ5l0JDriaZlR1VYy-BtO7LNlyx58f9W9hKM_Ux7N9SxJbds1Ds1aN2L2_0qu3ohubmH6EcbtFdk_HRcBP22i1vNgjiqLbrkav1iyHBVvdXu

Uploaded by

mohamed ben slimane0 ratings0% found this document useful (0 votes)

12 views6 pagesCopyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

12 views6 pagesAPznzaaw2ORoRWxw2cHZTrQf-nvEdq8ZfsRH-W2rtGqw_RKeH3M9CzsCp3TwStUDajWoxmHKcirqvkKVyo2Ii370FTuh54mC0M0jTkJYoauMeJ5l0JDriaZlR1VYy-BtO7LNlyx58f9W9hKM_Ux7N9SxJbds1Ds1aN2L2_0qu3ohubmH6EcbtFdk_HRcBP22i1vNgjiqLbrkav1iyHBVvdXu

APznzaaw2ORoRWxw2cHZTrQf-nvEdq8ZfsRH-W2rtGqw_RKeH3M9CzsCp3TwStUDajWoxmHKcirqvkKVyo2Ii370FTuh54mC0M0jTkJYoauMeJ5l0JDriaZlR1VYy-BtO7LNlyx58f9W9hKM_Ux7N9SxJbds1Ds1aN2L2_0qu3ohubmH6EcbtFdk_HRcBP22i1vNgjiqLbrkav1iyHBVvdXu

Uploaded by

mohamed ben slimaneCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 6

AD ty a hy

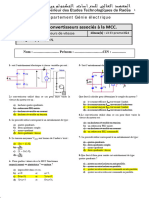

Ministére de 'Enscignement Supérieur

dela Recherche Scientifique

Direction Générale des Etudes Technologiques = Resi ala ta 59)

Institut Supérieur des Etudes Technologiques de Nabeul = Ae si a al spa

Département GE (4.0 : 2018-2019) (2019-2018 E09 Chg eal a

Classe; AN31 et AII32 ; Date: Janvier 2019

Matiére: Cireuits DSP Durée: 730mm

Enscignant : Mr Nizar TOUJENT Documents: — Autorisés C1 Nom autorisés

Examen Ds O Nombre de pages du document réponse : 06

Nom —Toueat — Prénoin -Nigan Classe : -—-------- N°CIN :

Note:

EXERCICE 1:

1. Définir les abréviations suivantes :

a Digitl Genel Prowe

RISC

ou Conaphex Tnsbuchion

Tiki © u if

Le Seconed

TiPeon of TAC Ber

Second hk

ThQlion Flouting - Bent

Operation Pe second

Tefa— Bile Be “ond Kf)

cpu Grob tose ony ame “Ue

DMA Dou Remary Access

© DARAM:.... RAQL...&. ALBA. A

Emulateur JTAG : .2db..tum. oct. puissant: poe facie. duc. debug Megaucel,

whats. Lsmulatun. TRG. / e

@),

1/6

EXERCICE 2:

1. Donner la définition du codage Qk.

2. Pour les nombres rationnels suivants, écrivez le mot binaire 8 bits signé au format Q3 qui

Tapproxime le mieux, en précisant si la représentation est exacte ou approchée =

Décimal “0.75 12 0.015 7

format Q3 signé | 4444.444.9.. |0000.4004.,....}a000.0009 too.cenf

43 & 3

exactelapprochée | Exachs........ Appcochée a Apprach....| Exacte.....

8. Coder en binaire puis en hexadécimal, les réels 51.575 et —532,8125 en =e.

normalisée. Justifier.

«BASIS A CAMEA8I ne,

0,6Ad24 995 4.25.4 2234320.

O22L.2HASAR = .A4YORS..

OY4G $95 x2..=.0,99.3%,

0/$9398....42..2. AFB.

= OSHE4CCCH

2/6

—

7

104.064.9414 0625 xt. QO8deg bbeMeC

D542 18923 126 42x04 6859765 665) Mamlrdse.:,.QC00.0

O/6I02IQERS.... Rc A SOFA EL

0,300FH42¢., O,SOATERS....

EXERCICE 3 :

1, Compléter le tableau ci-dessous par les alternatives suivantes :

~ Calcul de V'adresse du résultat + Décodage de l'instruction

+ Lecture des opérandes en mémoire * Calcul des adresses des opérandes

+ Exécution de l'instruction + Ecriture du résultat a l’adresse calculée

= Mémoire de programmes + Incrémentation du compteur ordinal

= Mémoire de données = Lecture du code de l'instruction en mémoire

3/6

Lo

ien écrire dans cette zone

~

~ ARAU( Auxiliary Register Arithmetic Unit)

~ AR (Adress Register) ~ ALU ( Arithmetic Logic Unit)

~ PC (Program Counter) ~ Décoduun.

Etage pipeline Description Partie hardware utilisée

P(refetch) [Tnovimutation du Comp hens. ec (o)9

FOFetcn) | ede du code de Parcs!

a Hue ar rege)

DOecoded | Decodage de Mnichuctin | Decoder [3

Aldocess) — | Cale dey adremes deo ARs, ARAU /O

© Read a i Témorre de ownins

Coeah de Vccurse dus

pasdki

ARs, ARAU ql

X(Bxecute) | Exdtin de Yunsbuuction TAC, ALU

£

hor be * | Wns dednsip/ (1)

sistére de I’Enselgnement Supérieur

de la Recherche Scientifique igaed

Direction Générale des Etudes Technologiques 2 Hea 8 oh tad Lata 5 91

Institut Supérieur des Etudes Technologiques de Nabeul. rie iy Ley gh gS lal tat gaa

Département GE (AU : 2018-2019) QUN-218 E29 Cp D igh

Classe: ANSI et AIL32, Date: Janvier 2019

Matiore Durée : 2430min

Enseis Mr Nizar TOUJENT Documents. Autorisés Non autorisés

[Examen psO Nombre de pages du document réponse : 06

Nom oun Prénom ta Classe N°CIN

/20

a

2. Les étapes d’exécution d'une instruction se fait en 4 étapes. Compléter le tableau ci-dessous :

@

2)

3)

@

3. En quoi architecture d'un DSP est-elle plus efficace que celle d'un microprocesseur pour les

algorithmes de traitement du signal ?

Archilechiene... de. Heavand

5/6

j crire d e .

a x rien ee _ _

4. Expliquer la différence entre Varchitecture Harvard et Von Neumann. Laquelle est pri

Jes DSP classiques, et iz

“éférée

pour

Un. Seal) cRerani..lacida. 2..De mémouie | SEparucin.clea. mde -pragaamame.

ie Z

2 U anckitediine ee BSE hrcpats et cable de

Harvard cor Be acticin dls dawndes oe Reaget tm

_ Temps lnk me wells bibesedion du LLU .

You might also like

- Corrigé New Test3Document3 pagesCorrigé New Test3mohamed ben slimaneNo ratings yet

- Correction Devoir 1Document3 pagesCorrection Devoir 1mohamed ben slimaneNo ratings yet

- New Test3Document3 pagesNew Test3mohamed ben slimaneNo ratings yet

- IntroductionDocument13 pagesIntroductionmohamed ben slimaneNo ratings yet

- Chapitre 3 Rãgimes de NeutreDocument19 pagesChapitre 3 Rãgimes de Neutremohamed ben slimaneNo ratings yet

- 01 Chapitre-1 VHDLDocument11 pages01 Chapitre-1 VHDLmohamed ben slimaneNo ratings yet

- Chapitre 4 HabilitationDocument12 pagesChapitre 4 Habilitationmohamed ben slimaneNo ratings yet

- Chap 3 Les Bascules Syst Log 2Document8 pagesChap 3 Les Bascules Syst Log 2mohamed ben slimaneNo ratings yet

- Chapitre 4 Les Compteurs Et Décompteurs Asynchrones Partie 1Document12 pagesChapitre 4 Les Compteurs Et Décompteurs Asynchrones Partie 1mohamed ben slimaneNo ratings yet

- Nouveau Document Microsoft Word 2Document3 pagesNouveau Document Microsoft Word 2mohamed ben slimaneNo ratings yet