Professional Documents

Culture Documents

Ect206 Computer Architecture and Microcontrollers, June 2022

Uploaded by

instapc0210Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Ect206 Computer Architecture and Microcontrollers, June 2022

Uploaded by

instapc0210Copyright:

Available Formats

"ffi

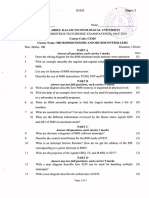

D 02000EcT206052106

RegNo.:

t'/ 3Y -€.lrrrr*a\E

APJ ABDUL K,{LAM TECHNOLOGICAL UN

Fourth Semester B.Tech Desree Examination June 2022 l9*

s##,,''

Course Code: ECT206

Course Name: COMPUTER ARCHITECTURE AI\D MICROCONTROLLERS

Max. Marks: 100 Duration: 3 Hours

PART A

(Answer all qaestions; eoch question carries 3 morks) Marks

I Di fferentiate between Von -Neumann and Harvard Arch itecture. (3)

2 Define Address bus, Data bus and Controlbus. (3)

a

J Draw and explain PSW of 8051 microcontroller. (3)

4 Write down the function of following instructions (3)

(a) ANL A,@Rr (b) RLC A (c) MOVX A,@Ro

5 What is constant in embedded C? (3)

6 Write an ALP to copy a block of 8 bytes of data to RAM locations starting at (3)

80H from RAM locations 20H.

7 What is the difference between a Timer and Counter? (3)

8 Explain the format of SCON Special Function Register. (3)

9 Define Virtualmemory. (3)

l0 Why does dynamic RAM need constant refreshing? How is this done? (3)

. PART B

(Aiswer one"full question from each module, each question conies 14 marks)

Module -1

II a) Explain Non-restoring division algoriinmWith an example. (8)

b) Explain Instruction Cycle with a sample timing diagram. (6)

12 a) Differentiate RISC and CISC Computer Architecture. (7)

b) How does a computer go from a set of stored instructions to running them? (7)

Module -2

13 a) Draw and explain the architecture of 8051 microcontroller. (9)

b) List the intemrpts available in the 8051 microcontroller. Explain IE and IP (5)

Specipl Function register.

Page 1 of 2

Downloaded from Ktunotes.in

020(rcEcT206052106

14, a) Explain. different Addressing Modes of 8051 Microcontroller with examples. (8)

b) Explain TCON and TMODtspecial function relister in 8051 Microcontroller. (6)

Module -3

15 a) Write an ALP to find the largest number in an array of l0 bytes, stored in the (6)

internal memory block starting with 2lH. Store the result at 50H.

b) Explain interfacing of stepper motor with microcontroller. Write an embedded C (8)

language program to rotate stepper motor in clockwise direction continuously in

full step mode.

16 a) Draw the block diagram to show how 8051 is connected to DAC 0808 at porr Pl. (S)

Write a program to generate Ramp signal.

,.

b) Write an 8051 C program to get a byte of data from Port Pr. If it is less than 100, (6)

send it to po; otherwise, send it to pz.

Module -4

l7 a) Draw and explain ARMT register architecture (7)

b) Write an ALP to generate a square wave of frequency l00KHz on pin PI.0, using (7)

Timer l-operating in mode 0. Assume Crystal frequency ll.0592MHz

18 a) Explain various System software. (8)

b) Write an embedded C program for the 8051 to transfer letter "A" serially at 9600 (6)

baud. continuouslv.

Module -5

19 a) Explain different mapping techniques in cache memory. (g)

b) Explain the Asynchronous input/output transfer with proper timing diagram. (6)

, 20 a) Explain the add4gss translation mechanism in Virtual Memory. (8)

b) Explain the working of DRAM and SRAM with neat diagram. .(6)

* rt*

Page2of 2

Downloaded from Ktunotes.in

You might also like

- Mercruiser 4.3L Mpi SpecsDocument2 pagesMercruiser 4.3L Mpi Specssalvatore dalessandro100% (1)

- Exploring BeagleBone: Tools and Techniques for Building with Embedded LinuxFrom EverandExploring BeagleBone: Tools and Techniques for Building with Embedded LinuxRating: 4 out of 5 stars4/5 (1)

- DL1 Dragons of DespairDocument38 pagesDL1 Dragons of DespairHeath Page100% (1)

- Egyptian Town PlanningDocument43 pagesEgyptian Town PlanningAbhishek Venkitaraman Iyer96% (23)

- p94-1738 Instrumentation t2000Document6 pagesp94-1738 Instrumentation t2000AaronNo ratings yet

- s4 CAM July 2022Document2 pagess4 CAM July 2022rensiNo ratings yet

- Ect206-Qp June21Document2 pagesEct206-Qp June21Rajeena VasudevanNo ratings yet

- APJ Abdul Kalam Technological University B.Tech Degree Exam QuestionsDocument2 pagesAPJ Abdul Kalam Technological University B.Tech Degree Exam QuestionsSourav SethuNo ratings yet

- Answer Any Five Questions Choosing at Least Two From Each PartDocument4 pagesAnswer Any Five Questions Choosing at Least Two From Each PartGuruprasadNo ratings yet

- Micro Processor and ApplicationsDocument2 pagesMicro Processor and Applicationsapi-3782519No ratings yet

- Microprocessors and Microcontrollers exam questionsDocument2 pagesMicroprocessors and Microcontrollers exam questionsAkash SahaNo ratings yet

- Rr310501 Interfacing Through MicroprocessorsDocument8 pagesRr310501 Interfacing Through MicroprocessorsSRINIVASA RAO GANTANo ratings yet

- CS305 Microprocessors and Microcontrollers, December 2019Document2 pagesCS305 Microprocessors and Microcontrollers, December 2019Anas AnsarNo ratings yet

- Sub Code & Name: Ec8691-Micro Processor and Micro Controller Portion Covered Units: 1 2 3 4 5 Max Marks: 100 PART-A (10X2 20)Document2 pagesSub Code & Name: Ec8691-Micro Processor and Micro Controller Portion Covered Units: 1 2 3 4 5 Max Marks: 100 PART-A (10X2 20)pradeepaNo ratings yet

- Apj Abdul Kalam Technological University: Answer All Questions, Each Carries3 MarksDocument2 pagesApj Abdul Kalam Technological University: Answer All Questions, Each Carries3 MarksVishal KeshariNo ratings yet

- Embedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Document2 pagesEmbedded Systems 9168 - Sample Paper of MSBTE For Sixth Semester Final Year Computer Engineering Diploma (80 Marks)Sanjay DudaniNo ratings yet

- Ect203 Logic Circuit Design, December 2022Document2 pagesEct203 Logic Circuit Design, December 2022ShakiraNo ratings yet

- PVP 19 Code: 19EE3602 III B.Tech - II Semester – Regular Examinations – JUNE 2022 MICROPROCESSORS & MICROCONTROLLERSDocument3 pagesPVP 19 Code: 19EE3602 III B.Tech - II Semester – Regular Examinations – JUNE 2022 MICROPROCESSORS & MICROCONTROLLERSSANAGAVARAPU BHAVANANo ratings yet

- rr310501 Interfacing Through MicroprocessorsDocument7 pagesrr310501 Interfacing Through MicroprocessorsSRINIVASA RAO GANTANo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological Universitykhushalee.chavadaNo ratings yet

- 15EE52Document2 pages15EE52varun gopaNo ratings yet

- Computer Science Engineering Model Question PaperDocument3 pagesComputer Science Engineering Model Question PaperChinnu Edwin A0% (1)

- 2018-Dec ECD-311 58Document2 pages2018-Dec ECD-311 58Tusshar PaulNo ratings yet

- Stucor QP Ee8551Document8 pagesStucor QP Ee8551NagendranNo ratings yet

- MCA (Revised) Term-End Examination - Une, 2409Document4 pagesMCA (Revised) Term-End Examination - Une, 2409ammanNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument3 pages3 Hours / 70 Marks: Seat NoC052 Diksha PawarNo ratings yet

- 3 Hours / 70 Marks: Seat NoDocument3 pages3 Hours / 70 Marks: Seat No58 EX Ramawat PankajNo ratings yet

- 316091winter 22Document2 pages316091winter 22khushalee.chavadaNo ratings yet

- Be Winter 2022Document2 pagesBe Winter 2022jagdishsimariyaNo ratings yet

- rr321402 MicroprocessorsDocument8 pagesrr321402 MicroprocessorsSRINIVASA RAO GANTANo ratings yet

- Model Question paper for Computer Architecture and Microcontrollers examDocument5 pagesModel Question paper for Computer Architecture and Microcontrollers examMr. Abhishek ViswakumarNo ratings yet

- 8086 Microprocessor Exam QuestionsDocument4 pages8086 Microprocessor Exam QuestionsnileshNo ratings yet

- Applied Electronics Watermark PDFDocument2 pagesApplied Electronics Watermark PDFRajat TaydeNo ratings yet

- r05320202 Microprocessors and Micro ControllersDocument5 pagesr05320202 Microprocessors and Micro ControllersSRINIVASA RAO GANTANo ratings yet

- Smart Materials, Sensors and ActuatorsDocument2 pagesSmart Materials, Sensors and ActuatorsmanojNo ratings yet

- rr321202 Vlsi Systems DesignDocument4 pagesrr321202 Vlsi Systems DesignSRINIVASA RAO GANTANo ratings yet

- Microprocessors and Interfacingjntumodelpaperwww Studentyogi Com 100113225356 Phpapp01Document8 pagesMicroprocessors and Interfacingjntumodelpaperwww Studentyogi Com 100113225356 Phpapp01Rakesh Kumar DNo ratings yet

- Gujarat Technological UniversityDocument2 pagesGujarat Technological UniversityBhautik Daxini100% (1)

- MCS 012june2020Document8 pagesMCS 012june2020kk2760057No ratings yet

- VI Sem Jun-July 2005Document10 pagesVI Sem Jun-July 2005Suraj KumarNo ratings yet

- 01385Document2 pages01385Kali MoorthiNo ratings yet

- MPMC 2Document2 pagesMPMC 2rityalonare21No ratings yet

- 151811-2151707-Mci - Winter 2018Document2 pages151811-2151707-Mci - Winter 2018Bhautik Daxini100% (1)

- Microcontroller App UnipuneTEElecDocument3 pagesMicrocontroller App UnipuneTEElecjupiteroxNo ratings yet

- C R5965 Pages: 2: Answer All Questions, Each Carries 3 MarksDocument2 pagesC R5965 Pages: 2: Answer All Questions, Each Carries 3 MarksVishal KeshariNo ratings yet

- MC& RISCDocument1 pageMC& RISCThirupathi MoorthyNo ratings yet

- Olp I/p. 8Document2 pagesOlp I/p. 8api-3782519No ratings yet

- rr312001 Microprocessors and InterfacingDocument8 pagesrr312001 Microprocessors and InterfacingSRINIVASA RAO GANTANo ratings yet

- KTU S5 Microprocessor and Microcontroller CSE May 2019 Question PaperDocument2 pagesKTU S5 Microprocessor and Microcontroller CSE May 2019 Question PaperAnand Baburajan0% (1)

- 9A04602 Microprocessors & MicrocontrollersDocument4 pages9A04602 Microprocessors & MicrocontrollerssivabharathamurthyNo ratings yet

- rr311903 Microprocessors and InterfacingDocument8 pagesrr311903 Microprocessors and InterfacingSRINIVASA RAO GANTANo ratings yet

- Stucor Qp-Ec8691Document21 pagesStucor Qp-Ec8691KrisHnA 2kNo ratings yet

- Ignou MCS 14Document5 pagesIgnou MCS 14Abhishek MandalNo ratings yet

- Summer 2023Document2 pagesSummer 2023khushalee.chavadaNo ratings yet

- Scheme - I Sample Question Paper: I. Instruction Set Ii. Applications Iii. Memory Organization. I/O CompatibilityDocument5 pagesScheme - I Sample Question Paper: I. Instruction Set Ii. Applications Iii. Memory Organization. I/O CompatibilityC052 Diksha PawarNo ratings yet

- Microprocessor and Microcontroller Anna University Question PapersDocument3 pagesMicroprocessor and Microcontroller Anna University Question PapersthennishaNo ratings yet

- rr420402 Radar EngineeringDocument8 pagesrr420402 Radar EngineeringSRINIVASA RAO GANTANo ratings yet

- MicroprocessorsDocument2 pagesMicroprocessorsShashank M ChanmalNo ratings yet

- Physics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSIFrom EverandPhysics and Technology of Crystalline Oxide Semiconductor CAAC-IGZO: Application to LSINo ratings yet

- Microprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureFrom EverandMicroprocessors & their Operating Systems: A Comprehensive Guide to 8, 16 & 32 Bit Hardware, Assembly Language & Computer ArchitectureRating: 1 out of 5 stars1/5 (1)

- CCST Cisco Certified Support Technician Study Guide: Networking ExamFrom EverandCCST Cisco Certified Support Technician Study Guide: Networking ExamNo ratings yet

- Topics in Engineering Logic: International Series of Monographs on Electronics and InstrumentationFrom EverandTopics in Engineering Logic: International Series of Monographs on Electronics and InstrumentationNo ratings yet

- Firelights PDFDocument2 pagesFirelights PDFEFG EFGNo ratings yet

- Chapter OneDocument18 pagesChapter Oneحيدر محمدNo ratings yet

- Job DescriptionDocument4 pagesJob Descriptionnafis hasnayenNo ratings yet

- PTE Academic Lesson Plan Ideas: Test Taking Strategies: Vikki Weston, Vessela GasperDocument2 pagesPTE Academic Lesson Plan Ideas: Test Taking Strategies: Vikki Weston, Vessela GasperStanley AlexNo ratings yet

- Question and AnsDocument33 pagesQuestion and AnsHawa MudalaNo ratings yet

- Linear Equations and Functions Financial PlansDocument3 pagesLinear Equations and Functions Financial PlansEmelyn AbucayNo ratings yet

- Showcase your talent and skills at Momentum 2021Document48 pagesShowcase your talent and skills at Momentum 2021Tanishq VermaNo ratings yet

- Plates of The Dinosaur Stegosaurus - Forced Convection Heat Loos FinsDocument3 pagesPlates of The Dinosaur Stegosaurus - Forced Convection Heat Loos FinsJuan Fernando Cano LarrotaNo ratings yet

- Collateral Asset DefinitionsDocument116 pagesCollateral Asset Definitionsapi-3748391100% (2)

- Finite Element and Analytical Modelling of PVC-confined Concrete Columns Under Axial CompressionDocument23 pagesFinite Element and Analytical Modelling of PVC-confined Concrete Columns Under Axial CompressionShaker QaidiNo ratings yet

- Student ProfileDocument2 pagesStudent Profileapi-571568290No ratings yet

- TIA PRO1 15 Drive With Startdrive ENGDocument35 pagesTIA PRO1 15 Drive With Startdrive ENGJoaquín RpNo ratings yet

- WBOX 0E-1GANGSIRN Spec SheetDocument1 pageWBOX 0E-1GANGSIRN Spec SheetAlarm Grid Home Security and Alarm MonitoringNo ratings yet

- A Day With Maria Becerra (1) - 2Document2 pagesA Day With Maria Becerra (1) - 2FelipeNo ratings yet

- Botulinum Toxin in Aesthetic Medicine Myths and RealitiesDocument12 pagesBotulinum Toxin in Aesthetic Medicine Myths and RealitiesЩербакова ЛенаNo ratings yet

- Illrigger - GM BinderDocument8 pagesIllrigger - GM BinderDorothyNo ratings yet

- Lesson 2.1Document16 pagesLesson 2.1Jeremie Manimbao OrdinarioNo ratings yet

- (PREP SƯU TẦM) Destination B1-22-25Document4 pages(PREP SƯU TẦM) Destination B1-22-25hanhuNo ratings yet

- Guide To Low Voltage Busbar Trunking Systems-BeamaDocument20 pagesGuide To Low Voltage Busbar Trunking Systems-BeamaGhayath Omer100% (1)

- Village Panchayat Secretary ApplicationDocument2 pagesVillage Panchayat Secretary Applicationsrpk serverNo ratings yet

- Strings: - A String Is A Sequence of Characters Treated As A Group - We Have Already Used Some String LiteralsDocument48 pagesStrings: - A String Is A Sequence of Characters Treated As A Group - We Have Already Used Some String LiteralsJNUNo ratings yet

- Isoefficiency Function A Scalability Metric For PaDocument20 pagesIsoefficiency Function A Scalability Metric For PaDasha PoluninaNo ratings yet

- Mitigating Contractor's Claim On Loss and Expense Due To The Extension of Time in Public Projects: An Exploratory SurveyDocument12 pagesMitigating Contractor's Claim On Loss and Expense Due To The Extension of Time in Public Projects: An Exploratory SurveyWeei Zhee70No ratings yet

- CALCULATE TRADE AND CASH DISCOUNTSDocument13 pagesCALCULATE TRADE AND CASH DISCOUNTSrommel legaspi71% (7)

- Med - Leaf - Full ReportDocument31 pagesMed - Leaf - Full ReportAdithya s kNo ratings yet

- SGM41542YTQF24G Ic Carga Moto g22Document47 pagesSGM41542YTQF24G Ic Carga Moto g22Gilson PereiraNo ratings yet