Professional Documents

Culture Documents

Jeu d Instructions ΜC 16F84

Jeu d Instructions ΜC 16F84

Uploaded by

abdouzaouiidrissiOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Jeu d Instructions ΜC 16F84

Jeu d Instructions ΜC 16F84

Uploaded by

abdouzaouiidrissiCopyright:

Available Formats

Jeu d'instructions des PIC 16F84A,

16F628A, 16F88, 16F876A et 16F886

Les PIC 16F84A, 16F628A, 16F88, 16F876A, 16F886 (famille mid-range) ont le

même jeu d'instructions, constitué de seulement 35 instructions (architecture RISC

:Reduced Instruction-Set Computer).

Une instruction est codée par un mot de 14 bits.

La mémoire programme (de type Flash) a une taille de :

1792 octets (16F84A)

3584 octets (16F628A)

7168 octets (16F88)

14 336 octets (16F876A - 16F886)

ce qui permet de stocker un programme de :

1024 instructions (16F84A)

2048 instructions (16F628A)

4096 instructions (16F88)

8192 instructions (16F876A - 16F886)

Une instruction nécessite 1 cycle, ou bien 2 cycles dans le cas d'une instruction de

branchement (GOTO, CALL ...).

Avec une horloge à quartz de 20 MHz, un cycle correspond à 4/(20.106) = 200

nanosecondes.

Le microcontrôleur peut donc exécuter jusqu'à 5 millions d'instructions par seconde

(5 MIPS) !

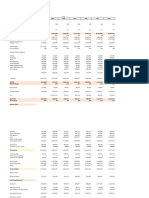

Jeu d'instructions

W : registre de travail (accumulateur), taille 8 bits

k : valeur littérale, taille 8 bits

Mnémonique, bit du registre nombre de

Description

opérande STATUS affecté cycles

MOVLW k k (8 bits) est chargé dans (W) - 1

ADDLW k Additionne k (8 bits) et (W) et

C, DC, Z 1

place le résultat dans (W)

SUBLW k Soustrait W de k (8 bits) et

place le résultat dans (W) C, DC, Z 1

k - (W) -> (W)

ANDLW k Réalise un ET logique entre k

(8 bits) et (W), et place le Z 1

résultat dans (W)

IORLW k Réalise un OU logique

(inclusif) entre k (8 bits) et

Z 1

(W), et place le résultat dans

(W)

XORLW k Réalise un OU exclusif entre k

(8 bits) et (W), et place le Z 1

résultat dans (W)

L : label (étiquette)

Mnémonique, bit du registre nombre de

Description

opérande STATUS affecté cycles

GOTO L Branchement à l'adresse L - 2

CALL L Appelle un sous-programme

(subroutine) situé à l'adresse - 2

L

RETURN Retour de sous-programme - 2

RETLW k Retour de sous-programme,

avec chargement de la valeur - 2

littérale k (8 bits) dans (W)

RETFIE Retour de sous-programme

- 2

d'interruption

CLRWDT Efface le Watchdog /TO, /PD 1

SLEEP Place le microcontrôleur en

/TO, /PD 1

mode sommeil

f : registre (spécial ou d'usage général)

b : position du bit (0 à 7)

Mnémonique, bit du registre nombre

Description

opérande STATUS affecté de cycles

BCF f , b Mise à 0 du bème bit du

- 1

registre f

BSF f , b Mise à 1 du bème bit du

- 1

registre f

BTFSC f , b Si le bème bit du registre f est

égal à 0, alors l'instruction

suivante est ignorée, et une

- 1 ou 2

instruction NOP est

exécutée à la place (soit 2

cycles)

BTFSS f , b Si le bème bit du registre f est

égal à 1, alors l'instruction

suivante est ignorée, et une

- 1 ou 2

instruction NOP est

exécutée à la place (soit 2

cycles)

f : registre (spécial ou d'usage général)

d : registre de destination (on peut choisir entre le registre de travail W et

le registre f).

bit du

registre

Mnémonique, nombre

Description STATU

opérande de cycles

S

affecté

MOVWF f (W) est chargé dans (f) - 1

MOVF f , d (f) (8 bits) est chargé dans (destination) Z 1

ADDWF f , d Additionne le contenu du registre f (8 bits)

C, DC,

et (W), et place le résultat dans 1

Z

(destination)

SUBWF f , d Soustrait (W) de (f) (8 bits) et place le

C, DC,

résultat dans (destination). 1

Z

(f) - (W) ->(destination)

ANDWF f , d Réalise un ET logique entre (f) (8 bits) et

Z 1

(W), et place le résultat dans (destination)

IORWF f , d Réalise un OU logique (inclusif) entre (f)

(8 bits) et (W), et place le résultat dans Z 1

(destination)

XORWF f , d Réalise un OU exclusif entre (f) (8 bits) et

Z 1

(W), et place le résultat dans (destination)

COMF f , d Réalise le complément logique de (f) (8

bits), et place le résultat dans (destination) Z 1

DECF f, d Décrémente (f) et place le résultat dans

(destination). Z 1

(f) - 1 -> (destination)

DECFSZ f, d Décrémente (f) et place le résultat dans

(destination).

Si le résultat est 0, alors l'instruction - 1 ou 2

suivante est ignorée, et une instruction

NOP est exécutée à la place (soit 2 cycles)

INCF f, d Incrémente (f) et place le résultat dans

(destination). Z 1

(f) + 1 -> (destination)

INCFSZ f, d Incrémente (f) et place le résultat dans

(destination).

Si le résultat est 0, alors l'instruction - 1 ou 2

suivante est ignorée, et une instruction

NOP est exécutée à la place (soit 2 cycles)

CLRF f Efface le contenu du registre (f).

Z 1

Remarque : le bit Z est donc mis à 1.

CLRW Efface le contenu de l'accumulateur (W).

Z 1

Remarque : le bit Z est donc mis à 1.

RLF f , d Réalise une rotation circulaire à gauche :

C 1

Le résultat est placé dans (destination).

RRF f, d Réalise une rotation circulaire à droite :

C 1

Le résultat est placé dans (destination).

SWAPF f, d Les 4 bits de poids forts et les 4 bits de

poids faibles de (f) sont échangés. - 1

Le résultat est placé dans (destination).

NOP Cette instruction ne fait rien (durée 1

- 1

cycle).

You might also like

- Standalone Kitchen Model WorkingDocument3 pagesStandalone Kitchen Model WorkingSujith psNo ratings yet

- 312-Audi A3 04 - Sistema EléctricoDocument68 pages312-Audi A3 04 - Sistema Eléctricomaxaub8293% (14)

- Science Investigatory Project: Group#3 Banana Peel As Shoe PolishDocument11 pagesScience Investigatory Project: Group#3 Banana Peel As Shoe PolishGMae Lim100% (4)

- Simulation des vibrations mécaniques, 2e édition: par Matlab, Simulink et AnsysFrom EverandSimulation des vibrations mécaniques, 2e édition: par Matlab, Simulink et AnsysNo ratings yet

- Formation 3D par la pratique avec C#5 et WPF: Modeliser des moleculesFrom EverandFormation 3D par la pratique avec C#5 et WPF: Modeliser des moleculesNo ratings yet

- FreeCAD | étape par étape: Apprenez à créer des objets 3D, des assemblages et des dessins techniquesFrom EverandFreeCAD | étape par étape: Apprenez à créer des objets 3D, des assemblages et des dessins techniquesNo ratings yet

- DVB NGHDocument10 pagesDVB NGHKhalil FatehNo ratings yet

- Codes Et TurbocodesDocument408 pagesCodes Et TurbocodesKhalil FatehNo ratings yet

- PHD Dore 26102007 VFDocument216 pagesPHD Dore 26102007 VFKhalil FatehNo ratings yet

- Rapport de StageDocument75 pagesRapport de StageKhalil FatehNo ratings yet

- Astuces de Programmation en Assembleur EN C PDFDocument31 pagesAstuces de Programmation en Assembleur EN C PDFKhalil FatehNo ratings yet

- VHDLDocument16 pagesVHDLKhalil Fateh100% (2)

- Rapport Projet RS232Document9 pagesRapport Projet RS232Khalil Fateh0% (1)

- Audiencia YoshiyamaDocument43 pagesAudiencia YoshiyamaJose LuisNo ratings yet

- Rapport Final PER Volume1 - Octobre 2009Document166 pagesRapport Final PER Volume1 - Octobre 2009Arnaud RAOUMBANo ratings yet

- Ultrasound-Guided Ilioinguinal and Iliohypogastric BlockDocument5 pagesUltrasound-Guided Ilioinguinal and Iliohypogastric BlockaksinuNo ratings yet

- Agriculture4 0-IEEETIIDocument13 pagesAgriculture4 0-IEEETIIAmanda FNo ratings yet

- Infografias Desastres en El PlanetaDocument12 pagesInfografias Desastres en El PlanetagatupanicornioNo ratings yet

- Ricoeur, Paul - para Una Teoría Del Discurso NarrativoDocument71 pagesRicoeur, Paul - para Una Teoría Del Discurso NarrativohurracapepeNo ratings yet

- Emailing Teacher Notes PDFDocument2 pagesEmailing Teacher Notes PDFSylwia WęglewskaNo ratings yet

- Introducing and Exchanging Personal Information: Practice 1Document11 pagesIntroducing and Exchanging Personal Information: Practice 1Riyan RiyanuartzNo ratings yet

- FAQ Cork Fabric Folclore Crafts 2018Document7 pagesFAQ Cork Fabric Folclore Crafts 2018gabrielampNo ratings yet

- Semana 1 - Sesión 01 y 02 - 5A-NDocument71 pagesSemana 1 - Sesión 01 y 02 - 5A-NJoseline Naomi Barrera LopezNo ratings yet

- Trabajo de Analisis PoliticoDocument64 pagesTrabajo de Analisis PoliticoAmarilis AmarilisNo ratings yet

- Datos P6 B013Document7 pagesDatos P6 B013Mario Rodriguez MarmolejoNo ratings yet

- Instrukcja Obslugi Overmax Multipic 2 5Document56 pagesInstrukcja Obslugi Overmax Multipic 2 5Arūnas su ŠNo ratings yet

- Biogeo11!20!21 Teste1 SolucaoDocument2 pagesBiogeo11!20!21 Teste1 Solucaogermano machadoNo ratings yet

- Análisis deflectométrico por etapas y comparación con el tipo de material de cada capa estructural en la obra construcción y mejoramiento de la carretera Matarani - Punta de Bombón tramo Km 2+000 al Km 7+000.pdfDocument376 pagesAnálisis deflectométrico por etapas y comparación con el tipo de material de cada capa estructural en la obra construcción y mejoramiento de la carretera Matarani - Punta de Bombón tramo Km 2+000 al Km 7+000.pdfJéssica ArlidNo ratings yet

- La Misión de La Iglesia MisionologíaDocument24 pagesLa Misión de La Iglesia MisionologíaAngel EspinozaNo ratings yet

- Bioquimica II - Info 3Document3 pagesBioquimica II - Info 3KATTY VERNAZANo ratings yet

- Proteccion para La CabezaDocument2 pagesProteccion para La CabezaLytmerAcuñaNo ratings yet

- MonografiaDocument7 pagesMonografiaFabricio André Contreras Miranda100% (1)

- Professor Manihar THESISDocument183 pagesProfessor Manihar THESISSatyabhama SanasamNo ratings yet

- AAE-03 Enterprise ApplicationDocument44 pagesAAE-03 Enterprise ApplicationAprida P. LestariNo ratings yet

- Autodiagnóstico Res. 0312 Frikaz S.A.SDocument15 pagesAutodiagnóstico Res. 0312 Frikaz S.A.SLilo BernalNo ratings yet

- Manual Anillo AtlanteDocument13 pagesManual Anillo AtlanteChristian Solis Ovando100% (1)

- Exercices Audit General Fsjes 19 20 PDFDocument6 pagesExercices Audit General Fsjes 19 20 PDFroudaniNo ratings yet

- FTP Proceso 17-9-437951 250000001 35556507Document12 pagesFTP Proceso 17-9-437951 250000001 35556507Alexander Guzman VNo ratings yet

- Chapter-4 Newton - S Law of MotionDocument52 pagesChapter-4 Newton - S Law of Motionaditya sureshNo ratings yet

- Actividad Virtual N°2 - Revisión de IntentosDocument26 pagesActividad Virtual N°2 - Revisión de IntentosMIJAIL FRANK RICALDI CARHUARICRANo ratings yet