Professional Documents

Culture Documents

Msi Armor RX470-570 4GB Esquematico V341 - 20

Uploaded by

Alejandro CamposOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Msi Armor RX470-570 4GB Esquematico V341 - 20

Uploaded by

Alejandro CamposCopyright:

Available Formats

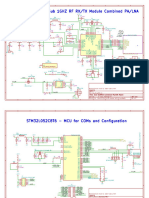

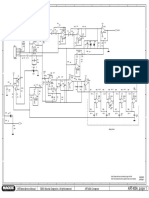

(1) PCI-EXPRESS EDGE CONNECTOR

00 M

+3.3V_BUS

0

RD 17 SI +3.3V_BUS +3.3V_AUX +3.3V_BUS +12V_BUS +12V_BUS +3.3V_BUS +3.3V_BUS

(C 96 C

MPCIE1

Q100 B1 +12V PRSNT1_A1 A1 PRESENCE

1

1

R103 R104 R109 B2 +12V +12V A2 C158

45.3K 45.3K 2 3 10K B3 +12V +12V A3 0.1uF

1% 1% 5% 6.3V

BSH111 B4 GND GND A4 SYSTEM JTAG TDI AND

G_SMBCLK 1 2 5% SMCLK B5 A5

2

IN 8,24 R105 0R SMCLK JTAG2

1

TDO ARE HARD WIRED.

)2 7 ON

JTDIO_LOOP

G_SMBDAT 1 2 5% SMDAT B6 A6 R111

BI 8,24 R106 0R SMDAT JTAG3 C159

B7 GND JTAG4 A7 0.1uF 10K

6.3V 5% U100

2 3 B8 +3.3V JTAG5 A8

B9 A9 3 5

2

Q110 JTAG1 +3.3V 1.8V_EN

0R

A VCC

+3.3V_BUS

B10 A10 1 2 5% 1 42,21,23

IN OUT

PERSTB_BUF

BSH111 3.3Vaux +3.3V R102

20,21

UNNAMED_1_74AUP1G57_I255_B

B Y

WAKEB B11 WAKE_ PERST_ A11 PERSTB 6 GND 2

C

1

Mechanical Key

CLKREQB B12 A12

+12V_BUS IN 7 RSVD_B12 GND 74AUP1G57GM

B13 A13

F

OUT

PCIE_REFCLKP

GND REFCLK+ 2

0

1 2

0R 5% B14 A14 1 2 5%

OUT OUT

PETP0_GFXRP0 2 PCIE_REFCLKN

R110 PETp0 REFCLK- 2 R120 1K

B15 A15

OUT

PETN0_GFXRN0 2

PETn0 GND DNI

+3.3V_BUS

B16 A16

IN

PERP0

GND PERp0 2

+3.3V_BUS 1 2 UNNAMED_1_MOSN_I230_G B17 A17

石 17 jo ID

0R 5%

IN

PERN0

MR110 PRSNT2_B17 PERn0 2

B18 GND GND A18

B19 A19

OUT

PETP1_GFXRP1 2

PETp1 RSVD_A19

Q101

B20 A20

OUT

PETN1_GFXRN1 2

PETn1 GND

1

1

BSH111

B21 A21

IN

PERP1

R107 GND PERp1 2

2.2K 2 3 B22 A22

IN

PERN1

5% GND PERn1 2

B23 A23

OUT

PETP2_GFXRP2 2

PETp2 GND

G_WAKEB 1 2 5% B24 A24

2

OUT OUT

PETN2_GFXRN2 2

7 PETn2 GND

B25 A25

IN

PERP2

R108

阿 09 ne EN

0R GND PERp2 2

B26 A26

IN

PERN2

LIMITED TO OBFF GND PERn2 2

B27 A27

OUT

PETP3_GFXRP3 2

PETp3 GND

B28 A28

OUT

PETN3_GFXRN3 2

PETn3 GND

B29 A29

IN

PERP3

GND PERp3 2

B30 A30

IN

PERN3

RSVD_B30 PERn3 2

B31 PRSNT2_B31 GND A31

B32 GND RSVD_A32 A32

B33 A33

OUT

PETP4_GFXRP4 2

PETp4 RSVD_A33

鋒 19 pe TI

B34 A34

OUT

PETN4_GFXRN4 2

PETn4 GND

B35 A35

IN

PERP4

GND PERp4 2

PLACE THESE CAPS AS CLOSE TO B36 A36

IN

PERN4

GND PERn4 2

PCIE CONNECTOR AS POSSIBLE B37 A37

OUT

PETP5_GFXRP5 2

PETp5 GND

B38 A38

OUT

PETN5_GFXRN5 2

PETn5 GND

B39 A39

IN

PERP5

GND PERp5 2

B40 A40

IN

PERN5

GND PERn5 2

+12V_BUS

B41 A41

OUT

PETP6_GFXRP6 2

PETp6 GND

02 i( AL

B42 A42

OUT

PETN6_GFXRN6 2

PETn6 GND

B43 A43

IN

PERP6

GND PERp6 2

B44 A44

IN

PERN6

GND PERn6 2

B45 A45

OUT

PETP7_GFXRP7 2

C157 C151 C152 PETp7 GND

10uF 0.15uF 0.15uF B46 A46

OUT

PETN7_GFXRN7 2

16V 16V 16V PETn7 GND

B47 A47

IN

PERP7

GND PERp7 2

B48 A48

IN

PERN7

PRSNT2_B48 PERn7 2

B49 GND GND A49

B50 A50

OUT

PETP8_GFXRP8 2

PETp8 RSVD_A50

(0

B51 A51

OUT

PETN8_GFXRN8 2

PETn8 GND

B52 A52

IN

PERP8

裴

GND PERp8 2

B53 A53

IN

PERN8

GND PERn8 2

+3.3V_BUS +3.3V_BUS

B54 A54

OUT

PETP9_GFXRP9 2

PETp9 GND

B55 A55

OUT

PETN9_GFXRN9 2

PETn9 GND

B56 A56

IN

PERP9

GND PERp9 2

B57 A57

IN

PERN9

GND PERn9 2

B58 A58

OUT

PETP10_GFXRP10

C153 C154 C155 C156 C165 2 PETp10 GND

00 RM 亮

10uF 0.1uF 1uF 0.01uF 10uF B59 A59

OUT

PETN10_GFXRN10

6.3V 6.3V 6.3V 10V 6.3V

2 PETn10 GND

B60 A60

IN

PERP10

GND PERp10 2

B61 A61

IN

PERN10

GND PERn10 2

B62 A62

OUT

PETP11_GFXRP11

2 PETp11 GND

B63 A63

OUT

PETN11_GFXRN11

2 PETn11 GND

B64 A64

IN

PERP11

GND PERp11 2

B65 A65

IN

PERN11

GND PERn11 2

B66 A66

OUT

PETP12_GFXRP12

2 PETp12 GND

B67 A67

68 A工 樂

OUT

PETN12_GFXRN12

2 PETn12 GND

B68 A68

IN

PERP12

GND PERp12 2

B69 A69

IN

PERN12

GND PERn12 2

B70 A70

OUT

PETP13_GFXRP13

2 PETp13 GND

B71 A71

OUT

PETN13_GFXRN13

2 PETn13 GND

B72 A72

IN

PERP13

GND PERp13 2

B73 A73

IN

PERN13

GND PERn13 2

B74 A74

OUT

PETP14_GFXRP14

2 PETp14 GND

B75 A75

OUT

PETN14_GFXRN14

2 PETn14 GND

76

B76 A76 SYMBOL LEGEND

IN

PERP14

GND PERp14 2

B77 A77

)

IN

PERN14

GND PERn14 2

B78 A78

OUT

PETP15_GFXRP15

2 PETp15 GND DNI DO NOT

B79 A79

OUT

PETN15_GFXRN15

程

2 PETn15 GND INSTALL

B80 A80

IN

PERP15

GND PERp15 2

PRESENCE B81 A81

IN

PERN15

1 PRSNT2_B81 PERn15 2 b or # ACTIVE

B82 RSVD_B82 GND A82 LOW

0)

x16 PCIe BUO BRING UP

ONLY

DIGITAL

課

GROUND

ANALOG

GROUND

MICRO-STAR INT'L CO.,LTD

MS-V341

MSI

Size Document Description Rev

Custom 0001 PCIE EDGE CONNECTOR 2.0

Date: Monday, June 27, 2016 Sheet 1 of 26

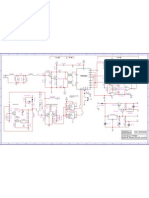

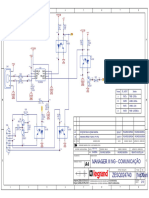

(2) ELLESMERE PCIE INTERFACE

00 M

0

RD 17 SI IN

IN

IN

TP101

1

1

TP102

1

PETP0_GFXRP0

PETN0_GFXRN0

PETP1_GFXRP1

AN42

AN43

AN41

AM41

PCIE_RX0P

PCIE_RX0N

PCIE_RX1P

U1B

PART 2 OF 18

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

AR38

AR39

AR37

AN37

PCIE_TX0P

PCIE_TX0N

PCIE_TX1P

PCIE_TX1N

C100

C101

C102

0.22uF

1

0.22uF

1

0.22uF

1

6.3V

6.3V

6.3V

PERP0

PERN0

PERP1

OUT

OUT

OUT

(C 96 C

IN OUT

PETN1_GFXRN1 PERN1

1 PCIE_RX1N PCIE_TX1N C103 0.22uF

1 6.3V

PCIE_TX2P

AM43 AN39

IN OUT

PETP2_GFXRP2 PERP2

1 PCIE_RX2P PCIE_TX2P PCIE_TX2N

C104 0.22uF

1 6.3V

AM42 AN38

IN OUT

PETN2_GFXRN2 PERN2

1 PCIE_RX2N PCIE_TX2N C105 0.22uF

1 6.3V

PCIE_TX3P

AK43 AM39

IN OUT

PETP3_GFXRP3 PERP3

1 PCIE_RX3P PCIE_TX3P PCIE_TX3N

C106 0.22uF

1 6.3V

AK42 AM38

IN OUT

PETN3_GFXRN3 PERN3

1 PCIE_RX3N PCIE_TX3N C107 0.22uF

1 6.3V

)2 7 ON

PCIE_TX4P

AJ42 AK38

IN OUT

PETP4_GFXRP4 PERP4

1 PCIE_RX4P PCIE_TX4P PCIE_TX4N

C108 0.22uF

1 6.3V

AJ43 AK39

IN OUT

PETN4_GFXRN4 PERN4

1 PCIE_RX4N PCIE_TX4N C109 0.22uF

1 6.3V

PCIE_TX5P

AJ41 AK37

IN OUT

PETP5_GFXRP5 PERP5

1 PCIE_RX5P PCIE_TX5P PCIE_TX5N

C111 0.22uF

1 6.3V

AG41 AJ37

IN OUT

PETN5_GFXRN5 PERN5

1 PCIE_RX5N PCIE_TX5N C110 0.22uF

1 6.3V

PCIE_TX6P

AG43 AJ39

IN OUT

PETP6_GFXRP6 PERP6

1 PCIE_RX6P PCIE_TX6P PCIE_TX6N

C112 0.22uF

1 6.3V

AG42 AJ38

IN OUT

PETN6_GFXRN6 PERN6

1 PCIE_RX6N PCIE_TX6N C113 0.22uF

1 6.3V

0 F

PCIE_TX7P

AF43 AG39

IN OUT

PETP7_GFXRP7 PERP7

1 PCIE_RX7P PCIE_TX7P PCIE_TX7N

C114 0.22uF

1 6.3V

AF42 AG38

IN OUT

PETN7_GFXRN7 PERN7

1 PCIE_RX7N PCIE_TX7N C115 0.22uF

1 6.3V

PCIE_TX8P

AE42 AF38

石 17 jo ID

IN OUT

PETP8_GFXRP8 PERP8

1 PCIE_RX8P PCIE_TX8P PCIE_TX8N

C116 0.22uF

1 6.3V

AE43 AF39

IN OUT

PETN8_GFXRN8 PERN8

1 PCIE_RX8N PCIE_TX8N C117 0.22uF

1 6.3V

PCIE_TX9P

AE41 AF37

IN OUT

PETP9_GFXRP9 PERP9

1 PCIE_RX9P PCIE_TX9P PCIE_TX9N

C118 0.22uF

1 6.3V

AD41 AE37

IN OUT

PETN9_GFXRN9 PERN9

1 PCIE_RX9N PCIE_TX9N C119 0.22uF

1 6.3V

P

PCIE_TX10P

AD43 AE39

IN OUT

PETP10_GFXRP10 PERP10

1 PCIE_RX10P PCIE_TX10P C120 0.22uF

1 6.3V

AD42 C AE38

PCIE_TX10N

IN OUT

PETN10_GFXRN10 PERN10

PCIE_RX10N

I PCIE_TX10N 0.22uF 6.3V

1 C121 1

阿 09 ne EN

PCIE_TX11P

X

TP117

AC43 AD39

IN OUT

PETP11_GFXRP11 PERP11

1 PCIE_RX11P PCIE_TX11P C122 0.22uF

1 6.3V

P

PCIE_TX11N

AC42 AD38

IN OUT

PETN11_GFXRN11 PERN11

1 PCIE_RX11N PCIE_TX11N C123 0.22uF

1 6.3V

R

TP118 E PCIE_TX12P

AA42 S AC38

IN OUT

PETP12_GFXRP12 PERP12

1 PCIE_RX12P PCIE_TX12P PCIE_TX12N

C124 0.22uF

1 6.3V

AA43 S AC39

IN OUT

PETN12_GFXRN12 PERN12

1 PCIE_RX12N PCIE_TX12N C125 0.22uF

1 6.3V

PCIE_TX13P

AA41 AC37

IN OUT

PETP13_GFXRP13 PERP13

1 PCIE_RX13P PCIE_TX13P PCIE_TX13N

C126 0.22uF

1 6.3V

Y41 AA37

IN OUT

PETN13_GFXRN13 PERN13

1 PCIE_RX13N PCIE_TX13N C127 0.22uF

1 6.3V

鋒 19 pe TI

PCIE_TX14P

Y43 AA39

IN OUT

PETP14_GFXRP14 PERP14

1 PCIE_RX14P PCIE_TX14P PCIE_TX14N

C128 0.22uF

1 6.3V

Y42 AA38

IN OUT

PETN14_GFXRN14 PERN14

1 PCIE_RX14N PCIE_TX14N C129 0.22uF

1 6.3V

PCIE_TX15P

W42 Y38

IN OUT

PETP15_GFXRP15 PERP15

1 PCIE_RX15P PCIE_TX15P PCIE_TX15N

C130 0.22uF

1 6.3V

W43 Y39

IN OUT

PETN15_GFXRN15 PERN15

1 PCIE_RX15N PCIE_TX15N C131 0.22uF

1 6.3V

02 i( AL

AR42

IN

PCIE_REFCLKP 1 PCIE_REFCLKP

AR43

IN

PCIE_REFCLKN 1 PCIE_REFCLKN PCIE_ZVSS

PCIE_ZVSS AK30 R155 1 2 200R 1%

PX_EN

V40 R156 1 2 0R 5%

PX_EN 21,23,24 OUT

UNNAMED_2_ELLESMEREL4_I197_PXEN

(0 裴

R150

1K C258

5% 0.1uF

6.3V

AV42

DNI

IN

PERSTB_BUF 1,21,23 PERSTB

+1.8V +0.8V

00 RM 亮

AM25 VDD_18

AN25 VDD_18

C1700 C1701 C1702 C1738 C176 C177 C172 C173 AN26 VDD_18

1uF 1uF 1uF 1uF 1uF 1uF 1uF 1uF AP26 VDD_18

6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V 6.3V

AP27 VDD_18

+1.8V

AR27 VDD_18

OVERLAP

C1703 C1704 C1705 C1719

0.1uF 0.1uF 0.1uF 0.1uF

68 A工 樂

6.3V 6.3V 6.3V 6.3V

MC141 C141 C136 C139 C140

10uF 4.7uF 1uF 0.1uF 0.01uF

6.3V 6.3V 6.3V 6.3V 6.3V

+0.8V

C1706 MC1707 C1707 C1708 C1709

4.7uF 22uF 4.7uF 4.7uF 4.7uF

6.3V 4V 6.3V 6.3V 6.3V

C137 C138 C142 C30

1uF 1uF 1uF 1uF

VDD_08 AJ30

6.3V 6.3V 6.3V 6.3V

OVERLAP

76

+0.8V

)

R4301 0R

EVDDQ_G

AJ29 1 2 5% EVDDQ

VSS 24 IN

AA34 AK29

程

VDD_08 VSS

AA35 VDD_08

1

+0.8V

C133 C145 C146 AD36 VDD_08 R4302

1uF 1uF 1uF AE35 VDD_08

1K

6.3V 6.3V 6.3V 5%

AF35 VDD_08

0)

AG36

2

VDD_08

C1711 AJ35 VDD_08

1uF

C147 C150 C1284 C1319 AK35 VDD_08

6.3V

1uF 1uF 1uF 1uF AM36 VDD_08

課

6.3V 6.3V 6.3V 6.3V

AN35 VDD_08

10u

C1713 C1714

0.1uF 0.1uF

6.3V 6.3V C161 C162 C160 C148 MC148

0.1uF 0.1uF 10uF 4.7uF 22uF REV 0.90

6.3V 6.3V 4V 6.3V 4V

ellesmere_l4

MC1717 C1717

22uF 4.7uF

4V 6.3V

OVERLAP

Check BOM for more detail

MICRO-STAR INT'L CO.,LTD

MS-V341

MSI

Size Document Description Rev

Custom 0002 ELLESMERE PCIE INTERFACE 2.0

Date: Monday, June 27, 2016 Sheet 2 of 26

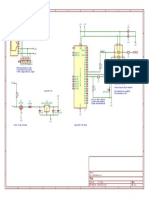

(3) ELLESMERE MEM INTERFACE CH A/B

00 M

0

U1C U1D

RD 17 SI

PART 3 OF 18 PART 4 OF 18

DQA0_<0> U43 A41 DQA1_<0> DQB0_<0> K26 G18 DQB1_<0>

DQA0_<0> DQA0_<1> 5 5 DQA1_<1> DQA1_<0> DQB0_<0> 5

DQB0_<1> 5

DQB1_<1> DQB1_<0>

DQA0_0 DQA1_0 DQB0_0 DQB1_0

U41 B40 E25 H18

DQA0_<1> DQA0_<2> 5 5 DQA1_<2> DQA1_<1> DQB0_<1> 5

DQB0_<2> 5

DQB1_<2> DQB1_<1>

DQA0_1 DQA1_1 DQB0_1 DQB1_1

U40 A39 F25 F17

DQA0_<2> DQA0_<3> 5 5 DQA1_<3> DQA1_<2> DQB0_<2> 5

DQB0_<3> 5

DQB1_<3> DQB1_<2>

DQA0_2 DQA1_2 DQB0_2 DQB1_2

R42 C38 H25 G17

DQA0_<3> DQA0_<4> 5 5 DQA1_<4> DQA1_<3> DQB0_<3> 5

DQB0_<4> 5

DQB1_<4> DQB1_<3>

DQA0_3 DQA1_3 DQB0_3 DQB1_3

P42 C36 J24 F15

DQA0_<4> DQA0_<5> 5 5 DQA1_<5> DQA1_<4> DQB0_<4> 5

DQB0_<5> 5

DQB1_<5> DQB1_<4>

DQA0_4 DQA1_4 DQB0_4 DQB1_4

M43 A36 D23 H15

DQA0_<5> DQA0_<6> 5 5 DQA1_<6> DQA1_<5> DQB0_<5> 5

DQB0_<6> 5

DQB1_<6> DQB1_<5>

DQA0_5 DQA1_5 DQB0_5 DQB1_5

M41 B35 E23 D14

DQA0_<6> DQA0_<7> 5 5 DQA1_<6> DQB0_<6> 5 5 DQB1_<6>

(C 96 C

DQA1_<7> DQB0_<7> DQB1_<7>

DQA0_6 DQA1_6 DQB0_6 DQB1_6

M40 A35 G23 E14

DQA0_<7> DQA0_<8> 5 5 DQA1_<8> DQA1_<7> DQB0_<7> 5

DQB0_<8> 5

DQB1_<8> DQB1_<7>

DQA0_7 DQA1_7 DQB0_7 DQB1_7

J43 A32 E21 J12

DQA0_<8> DQA0_<9> 5 5 DQA1_<9> DQA1_<8> DQB0_<8> 5

DQB0_<9> 5

DQB1_<9> DQB1_<8>

DQA0_8 DQA1_8 DQB0_8 DQB1_8

J42 C32 J20 E11

DQA0_<9> DQA0_<10>5 5 DQA1_<10> DQA1_<9> DQB0_<9> 5

DQB0_<10> 5

DQB1_<10> DQB1_<9>

DQA0_9 DQA1_9 DQB0_9 DQB1_9

H43 D32 G20 F11

DQA0_<10> DQA0_<11>5 5 DQA1_<11> DQA1_<10> DQB0_<10> 5

DQB0_<11> 5

DQB1_<11> DQB1_<10>

DQA0_10 DQA1_10 DQB0_10 DQB1_10

H41 B30 F20 H11

DQA0_<11> DQA0_<12>5 5 DQA1_<12> DQA1_<11> DQB0_<11> 5

DQB0_<12> 5

DQB1_<12> DQB1_<11>

DQA0_11 DQA1_11 DQB0_11 DQB1_11

F41 B29 E19 E9

DQA0_<12> DQA0_<13>5 5 DQA1_<13> DQA1_<12> DQB0_<12> 5

DQB0_<13> 5

DQB1_<13> DQB1_<12>

DQA0_12 DQA1_12 DQB0_12 DQB1_12

E43 D27 F19 G9

DQA0_<13> DQA0_<14>5 5 DQA1_<14> DQA1_<13> DQB0_<13> 5

DQB0_<14> 5

DQB1_<14> DQB1_<13>

DQA0_13 DQA1_13 DQB0_13 DQB1_13

)2 7 ON

C43 C27 E18 H9

DQA0_<14> DQA0_<15>5 5 DQA1_<15> DQA1_<14> DQB0_<14> 5

DQB0_<15> 5

DQB1_<15> DQB1_<14>

DQA0_14 DQA1_14 DQB0_14 DQB1_14

D42 A27 D18 F8

DQA0_<15> DQA0_<16>5 5 DQA1_<16> DQA1_<15> DQB0_<15> 5

DQB0_<16> 5

DQB1_<16> DQB1_<15>

DQA0_15 DQA1_15 DQB0_15 DQB1_15

U38 E38 C20 B15

DQA0_<16> DQA0_<17>5 5 DQA1_<17> DQA1_<16> DQB0_<16> 5

DQB0_<17> 5

DQB1_<17> DQB1_<16>

DQA0_16 DQA1_16 DQB0_16 DQB1_16

U37 H36 A20 C15

DQA0_<17> DQA0_<18>5 5 DQA1_<18> DQA1_<17> DQB0_<17> 5

DQB0_<18> 5

DQB1_<18> DQB1_<17>

DQA0_17 DQA1_17 DQB0_17 DQB1_17

R38 F36 D20 A14

DQA0_<18> DQA0_<19>5 5 DQA1_<19> DQA1_<18> DQB0_<18> 5

DQB0_<19> 5

DQB1_<19> DQB1_<18>

DQA0_18 DQA1_18 DQB0_18 DQB1_18

R36 G35 B19 B14

DQA0_<19> DQA0_<20>5 5 DQA1_<20> DQA1_<19> DQB0_<19> 5

DQB0_<20> 5

DQB1_<20> DQB1_<19>

DQA0_19 DQA1_19 DQB0_19 DQB1_19

P39 E33 B18 D12

DQA0_<20> DQA0_<21>5 5 DQA1_<21> DQA1_<20> DQB0_<20> 5

DQB0_<21> 5

DQB1_<21> DQB1_<20>

DQA0_20 DQA1_20 DQB0_20 DQB1_20

P37 F33 A17 B11

DQA0_<21> DQA0_<22>5 5 DQA1_<22> DQA1_<21> DQB0_<21> 5

DQB0_<22> 5

DQB1_<22> DQB1_<21>

DQA0_21 DQA1_21 DQB0_21 DQB1_21

M38 F32 C17 C11

F

DQA0_<22> DQA0_<23>5 5 DQA1_<23> DQA1_<22> DQB0_<22> 5

DQB0_<23> 5

DQB1_<23> DQB1_<22>

DQA0_22 DQA1_22 DQB0_22 DQB1_22

0

M37 G32 D17 A9

DQA0_<23> DQA0_<24>5 5 DQA1_<24> DQA1_<23> DQB0_<23> 5

DQB0_<24> 5

DQB1_<24> DQB1_<23>

DQA0_23 DQA1_23 DQB0_23 DQB1_23

L36 G30 A26 C8

DQA0_<24> DQA0_<25>5 5 DQA1_<25> DQA1_<24> DQB0_<24> 5

DQB0_<25> 5

DQB1_<25> DQB1_<24>

DQA0_24 DQA1_24 DQB0_24 DQB1_24

J40 J29 B26 D8

DQA0_<25> DQA0_<26>5 5 DQA1_<26> DQA1_<25> DQB0_<25> 5

DQB0_<26> 5

DQB1_<26> DQB1_<25>

DQA0_25 DQA1_25 DQB0_25 DQB1_25

J39 E29 C25 C6

DQA0_<27>5 5 5 5

石 17 jo ID

DQA0_<26> J37

DQA0_26 DQA1_26

F29 DQA1_<27> DQA1_<26> DQB0_<26> DQB0_<27> B25

DQB0_26 DQB1_26

B6 DQB1_<27> DQB1_<26>

DQA0_<27> DQA0_<28>5 5 DQA1_<28> DQA1_<27> DQB0_<27> 5

DQB0_<28> 5

DQB1_<28> DQB1_<27>

DQA0_27 DQA1_27 DQB0_27 DQB1_27

E40 F27 A24 D5

DQA0_<28> DQA0_<29>5 5 DQA1_<29> DQA1_<28> DQB0_<28> 5

DQB0_<29> 5

DQB1_<29> DQB1_<28>

DQA0_28 DQA1_28 DQB0_28 DQB1_28

E41 D26 A23 C4

DQA0_<29> DQA0_<30>5 5 DQA1_<30> DQA1_<29> DQB0_<29> 5

DQB0_<30> 5

DQB1_<30> DQB1_<29>

DQA0_29 DQA1_29 DQB0_29 DQB1_29

D39 E26 B23 B4

DQA0_<30> DQA0_<31>5 5 DQA1_<31> DQA1_<30> DQB0_<30> 5

DQB0_<31> 5

DQB1_<31> DQB1_<30>

DQA0_30 DQA1_30 DQB0_30 DQB1_30

C39 G26 D21 A3

DQA0_<31> 5 DQA0_31 DQA1_31 5 DQA1_<31> DQB0_<31> 5 DQB0_31 DQB1_31 5 DQB1_<31>

MAA0_<0> U32 H33 MAA1_<0> MAB0_<0> H23 N18 MAB1_<0>

MAA0_<0> MAA0_<1> 5 5 MAA1_<1> MAA1_<0> MAB0_<0> 5

MAB0_<1> 5

MAB1_<1> MAB1_<0>

阿 09 ne EN

MAA0_0 MAA1_0 MAB0_0 MAB1_0

U34 M32 N24 K17

MAA0_<1> MAA0_<2> 5 MAA0_1 MAA1_1 5 MAA1_<2> MAA1_<1> MAB0_<1> 5

MAB0_<2>

MAB0_1 MAB1_1 5

MAB1_<2> MAB1_<1>

V31 J32 K24 N17

MAA0_<2> MAA0_<3> 5 MAA0_2 M MAA1_2 5 MAA1_<3> MAA1_<2> MAB0_<2> 5

MAB0_<3>

MAB0_2 M MAB1_2 5

MAB1_<3> MAB1_<2>

U35 E K32 M24 E M17

MAA0_<3> MAA0_<4> 5 MAA0_3

M

MAA1_3 5 MAA1_<4> MAA1_<3> MAB0_<3> 5

MAB0_<4>

MAB0_3

M

MAB1_3 5

MAB1_<4> MAB1_<3>

V36 K30 L25 L15

MAA0_<4> MAA0_<5> 5 MAA0_4

O

MAA1_4 5 MAA1_<5> MAA1_<4> MAB0_<4> 5

MAB0_<5>

MAB0_4

O

MAB1_4 5

MAB1_<5> MAB1_<4>

V33 L30 M25 J15

MAA0_<5> MAA0_<6> 5 MAA0_5

R MAA1_5 5 MAA1_<6> MAA1_<5> MAB0_<5> 5

MAB0_<6>

MAB0_5

R MAB1_5 5

MAB1_<6> MAB1_<5>

R33 H35 N23 P19

MAA0_<6> MAA0_<7> 5 MAA0_6 Y MAA1_6 5 MAA1_<7> MAA1_<6> MAB0_<6> 5

MAB0_<7>

MAB0_6 Y MAB1_6 5

MAB1_<7> MAB1_<6>

R35 L33 L23 K18

MAA0_<7> MAA0_<8> 5 MAA0_7

I

MAA1_7 5 MAA1_<8> MAA1_<7> MAB0_<7> 5

MAB0_<8>

MAB0_7

I

MAB1_7 5

MAB1_<8> MAB1_<7>

U31 J33 K23 L18

MAA0_<8> 5 MAA0_8

N

MAA1_8 5 MAA1_<8> MAB0_<8> 5 MAB0_8

N

MAB1_8 5 MAB1_<8>

鋒 19 pe TI

W35 N27 J27 K14

MAA0_9

T MAA1_9 MAB0_9

T MAB1_9

E E

BI

WCKA0_0 5 L42 WCKA0_0 R WCKA1_0

5 B33 WCKA1_0

BI BI

WCKB0_0 5 G21 WCKB0_0 R WCKB1_0

5 F12 WCKB1_0

BI

WCKA0B_0 L41 F C33 WCKA1B_0 WCKB0B_0 H21 F G12 WCKB1B_0

BI 5 WCKA0B_0

A

WCKA1B_0

5

BI BI 5 WCKB0B_0

A

WCKB1B_0

5

BI

C C

WCKA0_1 L39 E D30 WCKA1_1 WCKB0_1 A21 E A8 WCKB1_1

BI 5 WCKA0_1 WCKA1_1

5

BI BI 5 WCKB0_1 WCKB1_1

5

BI

WCKA0B_1 L38 E30 WCKA1B_1 WCKB0B_1 B21 B9 WCKB1B_1

BI 5 WCKA0B_1 WCKA1B_1

5

BI BI 5 WCKB0B_1 WCKB1B_1

5

BI

02 i( AL

EDCA0_0 R41 B38 EDCA1_0 EDCB0_0 F24 E15 EDCB1_0

BI 5 EDCA0_0 EDCA1_0

5

BI BI 5 EDCB0_0 EDCB1_0

5

BI

EDCA0_1 F42 C29 EDCA1_1 EDCB0_1 J19 D9 EDCB1_1

BI 5 EDCA0_1 EDCA1_1

5

BI BI 5 EDCB0_1 EDCB1_1

5

BI

EDCA0_2 R39 D35 EDCA1_2 EDCB0_2 A18 A12 EDCB1_2

BI 5 EDCA0_2 EDCA1_2

5

BI BI 5 EDCB0_2 EDCB1_2

5

BI

EDCA0_3 H38 G27 EDCA1_3 EDCB0_3 D24 B5 EDCB1_3

BI 5 EDCA0_3 EDCA1_3

5

BI BI 5 EDCB0_3 EDCB1_3

5

BI

DDBIA0_0 P43 D36 DDBIA1_0 DDBIB0_0 G24 J17 DDBIB1_0

BI 5 DDBIA0_0 DDBIA1_0

5

BI BI 5 DDBIB0_0 DDBIB1_0

5

BI

DDBIA0_1 H40 B A30 DDBIA1_1 DDBIB0_1 H19 B J11 DDBIB1_1

BI 5 DDBIA0_1

A

DDBIA1_1

5

BI BI 5 DDBIB0_1

A

DDBIB1_1

5

BI

DDBIA0_2 P40 E35 DDBIA1_2 DDBIB0_2 C19 C12 DDBIB1_2

BI 5 DDBIA0_2

N DDBIA1_2

5

BI BI 5 DDBIB0_2

N DDBIB1_2

5

BI

(0

DDBIA0_3 F39 K H29 DDBIA1_3 DDBIB0_3 C24 K A5 DDBIB1_3

BI 5 DDBIA0_3 DDBIA1_3

5

BI BI 5 DDBIB0_3 DDBIB1_3

5

BI

裴

ADBIA0 P36 A J36 ADBIA1 ADBIB0 L21 B L19 ADBIB1

BI 5 ADBIA0 ADBIA1

5

BI BI 5 ADBIB0 ADBIB1

5

BI

Y34 M27 L26 K12

OUT OUT OUT OUT

CSA0B_0 CSA1B_0 CSB0B_0 CSB1B_0

5 CSA0B_0 CSA1B_0

5 5 CSB0B_0 CSB1B_0

5

00 RM 亮

R32 L35 K21 M19

OUT OUT OUT OUT

CASA0B CASA1B CASB0B CASB1B

5 CASA0B CASA1B

5 5 CASB0B CASB1B

5

P33 M35 K20 M20

OUT OUT OUT OUT

RASA0B RASA1B RASB0B RASB1B

5 RASA0B RASA1B

5 5 RASB0B RASB1B

5

V34 H30 J25 M15

OUT OUT OUT OUT

WEA0B WEA1B WEB0B WEB1B

5 WEA0B WEA1B

5 5 WEB0B WEB1B

5

P34 M34 N21 N20

OUT OUT OUT OUT

CKEA0 CKEA1 CKEB0 CKEB1

5 CKEA0 CKEA1

5 5 CKEB0 CKEB1

5

W32 M29 P26 H14

OUT OUT OUT OUT

CLKA0 CLKA1 CLKB0 CLKB1

5 CLKA0 CLKA1

5 5 CLKB0 CLKB1

5

W33 L29 N26 G14

OUT OUT OUT OUT

CLKA0B CLKA1B CLKB0B CLKB1B

5 CLKA0B CLKA1B

5 5 CLKB0B CLKB1B

5

68 A工 樂

+MVDD +MVDD

1%

MEM_CALRA MEM_CALRB

120R 2 1 R3610 Y31 MEM_CALRA 2

R3601 1 120R 1% P15 MEM_CALRB

1

1

R3602 R3603

40.2R 40.2R

1% 1%

MVREF_A MVREF_B

P25 P20

2

2

MVREFDA MVREFDB

76 )

1

1

C3602 R3606 C3603 R3607

1uF 100R 1uF 100R

程

6.3V 1% 6.3V 1%

2

2

0)

W30 M14

OUT

DRAM_RSTA 21 DRAM_RSTA DRAM_RSTB

DRAM_RST1_RR DRAM_RST1_R

2

5 R3630 1 49.9R 1% 2

R3615 1 10R 1%

OUT

DRAM_RST1

課

MVREFD/S = 0.7 * VDDR1

REV 0.90 REV 0.90

1

MVREFD/S = 0.7 * VDDR1

ellesmere_l4 C3607 R3612 ellesmere_l4

120pF 5.1K

50V 1%

2

MICRO-STAR INT'L CO.,LTD

MS-V341

MSI

Size Document Description Rev

Custom 0003 ELLESMERE MEM CH AB 2.0

Date: Monday, June 27, 2016 Sheet 3 of 26

(4) ELLESMERE MEM INTERFACE CH C/D

00 M

0

U1E U1F

RD 17 SI

PART 5 OF 18 PART 6 OF 18

DQC0_<0> C1 AA4 DQC1_<0> DQD0_<0> AF7 AW3 DQD1_<0>

DQC0_<0> 6

DQC0_<1>

DQC0_0 DQC1_0 6 DQC1_<1> DQC1_<0> DQD0_<0> DQD0_<1> 6

DQD0_0 DQD1_0 6 DQD1_<1> DQD1_<0>

D2 AC2 AF5 AW4

DQC0_<1> 6

DQC0_<2>

DQC0_1 DQC1_1 6 DQC1_<2> DQC1_<1> DQD0_<1> DQD0_<2> 6

DQD0_1 DQD1_1 6 DQD1_<2> DQD1_<1>

D3 AC1 AF4 BA5

DQC0_<2> 6

DQC0_<3>

DQC0_2 DQC1_2 6 DQC1_<3> DQC1_<2> DQD0_<2> DQD0_<3> 6

DQD0_2 DQD1_2 6 DQD1_<3> DQD1_<2>

E4 AD1 AG6 AY5

DQC0_<3> 6

DQC0_<4>

DQC0_3 DQC1_3 6 DQC1_<4> DQC1_<3> DQD0_<3> DQD0_<4> 6

DQD0_3 DQD1_3 6 DQD1_<4> DQD1_<3>

F2 AE3 AJ6 AU9

DQC0_<4> 6

DQC0_<5>

DQC0_4 DQC1_4 6 DQC1_<5> DQC1_<4> DQD0_<4> DQD0_<5> 6

DQD0_4 DQD1_4 6 DQD1_<5> DQD1_<4>

F3 AE2 AJ5 AW9

DQC0_<5> 6

DQC0_<6>

DQC0_5 DQC1_5 6 DQC1_<6> DQC1_<5> DQD0_<5> DQD0_<6> 6

DQD0_5 DQD1_5 6 DQD1_<6> DQD1_<5>

H4 AF2 AJ9 AY9

DQC0_<6> 6 6 DQC1_<6> DQD0_<6> DQD0_<7> 6 6 DQD1_<6>

(C 96 C

DQC0_<7> DQC1_<7> DQD1_<7>

DQC0_6 DQC1_6 DQD0_6 DQD1_6

H3 AF1 AK7 AT11

DQC0_<7> 6

DQC0_<8>

DQC0_7 DQC1_7 6 DQC1_<8> DQC1_<7> DQD0_<7> DQD0_<8> 6

DQD0_7 DQD1_7 6 DQD1_<8> DQD1_<7>

J1 U4 AM7 AU12

DQC0_<8> 6

DQC0_<9>

DQC0_8 DQC1_8 6 DQC1_<9> DQC1_<8> DQD0_<8> DQD0_<9> 6

DQD0_8 DQD1_8 6 DQD1_<9> DQD1_<8>

L3 U3 AM6 AV12

DQC0_<9> 6

DQC0_<10>

DQC0_9 DQC1_9 6 DQC1_<10> DQC1_<9> DQD0_<9> DQD0_<10>6

DQD0_9 DQD1_9 6 DQD1_<10> DQD1_<9>

L2 U1 AN6 AU14

DQC0_<10> 6

DQC0_<11>

DQC0_10 DQC1_10 6 DQC1_<11> DQC1_<10> DQD0_<10> DQD0_<11>6

DQD0_10 DQD1_10 6 DQD1_<11> DQD1_<10>

M4 V2 AN5 AW14

DQC0_<11> 6

DQC0_<12>

DQC0_11 DQC1_11 6 DQC1_<12> DQC1_<11> DQD0_<11> DQD0_<12>6

DQD0_11 DQD1_11 6 DQD1_<12> DQD1_<11>

P2 W2 AR7 AT15

DQC0_<12> 6

DQC0_<13>

DQC0_12 DQC1_12 6 DQC1_<13> DQC1_<12> DQD0_<12> DQD0_<13>6

DQD0_12 DQD1_12 6 DQD1_<13> DQD1_<12>

P1 Y4 AT6 AV15

DQC0_<13> 6

DQC0_<14>

DQC0_13 DQC1_13 6 DQC1_<14> DQC1_<13> DQD0_<13> DQD0_<14>6

DQD0_13 DQD1_13 6 DQD1_<14> DQD1_<13>

)2 7 ON

R3 Y1 AT8 AU17

DQC0_<14> 6

DQC0_<15>

DQC0_14 DQC1_14 6 DQC1_<15> DQC1_<14> DQD0_<14> DQD0_<15>6

DQD0_14 DQD1_14 6 DQD1_<15> DQD1_<14>

R2 Y3 AV5 AV17

DQC0_<15> 6

DQC0_<16>

DQC0_15 DQC1_15 6 DQC1_<16> DQC1_<15> DQD0_<15> DQD0_<16>6

DQD0_15 DQD1_15 6 DQD1_<16> DQD1_<15>

H6 V4 AG1 BB4

DQC0_<16> 6

DQC0_<17>

DQC0_16 DQC1_16 6 DQC1_<17> DQC1_<16> DQD0_<16> DQD0_<17>6

DQD0_16 DQD1_16 6 DQD1_<17> DQD1_<16>

J8 V5 AG3 BC3

DQC0_<17> 6

DQC0_<18>

DQC0_17 DQC1_17 6 DQC1_<18> DQC1_<17> DQD0_<17> DQD0_<18>6

DQD0_17 DQD1_17 6 DQD1_<18> DQD1_<17>

J7 W6 AG4 BC5

DQC0_<18> 6

DQC0_<19>

DQC0_18 DQC1_18 6 DQC1_<19> DQC1_<18> DQD0_<18> DQD0_<19>6

DQD0_18 DQD1_18 6 DQD1_<19> DQD1_<18>

J5 W5 AJ2 BA6

DQC0_<19> 6

DQC0_<20>

DQC0_19 DQC1_19 6 DQC1_<20> DQC1_<19> DQD0_<19> DQD0_<20>6

DQD0_19 DQD1_19 6 DQD1_<20> DQD1_<19>

L8 Y6 AK2 BA8

DQC0_<20> 6

DQC0_<21>

DQC0_20 DQC1_20 6 DQC1_<21> DQC1_<20> DQD0_<20> DQD0_<21>6

DQD0_20 DQD1_20 6 DQD1_<21> DQD1_<20>

L6 Y7 AM4 BC8

DQC0_<21> 6

DQC0_<22>

DQC0_21 DQC1_21 6 DQC1_<22> DQC1_<21> DQD0_<21> DQD0_<22>6

DQD0_21 DQD1_21 6 DQD1_<22> DQD1_<21>

L5 Y9 AM3 BB9

F

DQC0_<22> 6

DQC0_<23>

DQC0_22 DQC1_22 6 DQC1_<23> DQC1_<22> DQD0_<22> DQD0_<23>6

DQD0_22 DQD1_22 6 DQD1_<23> DQD1_<22>

0

M9 AA5 AM1 BC9

DQC0_<23> 6

DQC0_<24>

DQC0_23 DQC1_23 6 DQC1_<24> DQC1_<23> DQD0_<23> DQD0_<24>6

DQD0_23 DQD1_23 6 DQD1_<24> DQD1_<23>

P5 AC7 AR1 AY12

DQC0_<24> 6

DQC0_<25>

DQC0_24 DQC1_24 6 DQC1_<25> DQC1_<24> DQD0_<24> DQD0_<25>6

DQD0_24 DQD1_24 6 DQD1_<25> DQD1_<24>

P4 AC5 AR2 BA12

DQC0_<25> 6

DQC0_<26>

DQC0_25 DQC1_25 6 DQC1_<26> DQC1_<25> DQD0_<25> DQD0_<26>6

DQD0_25 DQD1_25 6 DQD1_<26> DQD1_<25>

R8 AC4 AT1 BC12

6 6 DQD0_<27>6 6

石 17 jo ID

DQC0_<26> DQC0_<27> R6

DQC0_26 DQC1_26

AD9 DQC1_<27> DQC1_<26> DQD0_<26> AT3

DQD0_26 DQD1_26

BB14 DQD1_<27> DQD1_<26>

DQC0_<27> 6

DQC0_<28>

DQC0_27 DQC1_27 6 DQC1_<28> DQC1_<27> DQD0_<27> DQD0_<28>6

DQD0_27 DQD1_27 6 DQD1_<28> DQD1_<27>

U7 AE8 AV3 BB15

DQC0_<28> 6

DQC0_<29>

DQC0_28 DQC1_28 6 DQC1_<29> DQC1_<28> DQD0_<28> DQD0_<29>6

DQD0_28 DQD1_28 6 DQD1_<29> DQD1_<28>

U6 AE6 AW1 AY17

DQC0_<29> 6

DQC0_<30>

DQC0_29 DQC1_29 6 DQC1_<30> DQC1_<29> DQD0_<29> DQD0_<30>6

DQD0_29 DQD1_29 6 DQD1_<30> DQD1_<29>

V8 AE5 AY2 BA17

DQC0_<30> 6

DQC0_<31>

DQC0_30 DQC1_30 6 DQC1_<31> DQC1_<30> DQD0_<30> DQD0_<31>6

DQD0_30 DQD1_30 6 DQD1_<31> DQD1_<30>

V7 AF10 BA1 BC17

DQC0_<31> 6 DQC0_31 DQC1_31 6 DQC1_<31> DQD0_<31> 6 DQD0_31 DQD1_31 6 DQD1_<31>

MAC0_<0> V13 AC8 MAC1_<0> MAD0_<0> AN8 AM17 MAD1_<0>

MAC0_<0> 6

MAC0_<1> 6 MAC1_<1> MAC1_<0> MAD0_<0> MAD0_<1> 6 6 MAD1_<1> MAD1_<0>

阿 09 ne EN

MAC0_0 MAC1_0 MAD0_0 MAD1_0

U10 AD13 AM12 AP17

MAC0_<1> 6

MAC0_<2>

MAC0_1 MAC1_1 6 MAC1_<2> MAC1_<1> MAD0_<1> MAD0_<2> 6

MAD0_1 MAD1_1 6 MAD1_<2> MAD1_<1>

U13 AD10 AM9 AL18

MAC0_<2> 6

MAC0_<3>

MAC0_2 M MAC1_2 6 MAC1_<3> MAC1_<2> MAD0_<2> MAD0_<3> 6

MAD0_2 M MAD1_2 6 MAD1_<3> MAD1_<2>

U12 E AD12 AM10 E AR17

MAC0_<3> 6

MAC0_<4>

MAC0_3

M

MAC1_3 6 MAC1_<4> MAC1_<3> MAD0_<3> MAD0_<4> 6

MAD0_3

M

MAD1_3 6 MAD1_<4> MAD1_<3>

R11 AE11 AK10 AT18

MAC0_<4> 6

MAC0_<5>

MAC0_4

O

MAC1_4 6 MAC1_<5> MAC1_<4> MAD0_<4> MAD0_<5> 6

MAD0_4

O

MAD1_4 6 MAD1_<5> MAD1_<4>

R9 AE12 AK11 AN18

MAC0_<5> 6

MAC0_<6>

MAC0_5

R MAC1_5 6 MAC1_<6> MAC1_<5> MAD0_<5> MAD0_<6> 6

MAD0_5

R MAD1_5 6 MAD1_<6> MAD1_<5>

W14 AC13 AR8 AN15

MAC0_<6> 6

MAC0_<7>

MAC0_6 Y MAC1_6 6 MAC1_<7> MAC1_<6> MAD0_<6> MAD0_<7> 6

MAD0_6 Y MAD1_6 6 MAD1_<7> MAD1_<6>

V10 AC11 AN11 AR15

MAC0_<7> 6

MAC0_<8>

MAC0_7

I

MAC1_7 6 MAC1_<8> MAC1_<7> MAD0_<7> MAD0_<8> 6

MAD0_7

I

MAD1_7 6 MAD1_<8> MAD1_<7>

V11 AC10 AN9 AL17

MAC0_<8> 6 MAC0_8

N

MAC1_8 6 MAC1_<8> MAD0_<8> 6 MAD0_8

N

MAD1_8 6 MAD1_<8>

鋒 19 pe TI

P10 AG9 AG13 AR19

MAC0_9

T MAC1_9 MAD0_9

T MAD1_9

E E

BI

WCKC0_0 6 H1 WCKC0_0 R WCKC1_0

6 AA1 WCKC1_0

BI BI

WCKD0_0 6 AK4 WCKD0_0 R WCKD1_0

6 AW11 WCKD1_0

BI

WCKC0B_0 J2 F AA2 WCKC1B_0 WCKD0B_0 AK5 F AV11 WCKD1B_0

BI 6 WCKC0B_0

A

WCKC1B_0

6

BI BI 6 WCKD0B_0

A

WCKD1B_0

6

BI

C C

WCKC0_1 M6 E AA7 WCKC1_1 WCKD0_1 AN2 E BB11 WCKD1_1

BI 6 WCKC0_1 WCKC1_1

6

BI BI 6 WCKD0_1 WCKD1_1

6

BI

WCKC0B_1 M7 AA8 WCKC1B_1 WCKD0B_1 AN3 BA11 WCKD1B_1

BI 6 WCKC0B_1 WCKC1B_1

6

BI BI 6 WCKD0B_1 WCKD1B_1

6

BI

02 i( AL

EDCC0_0 E2 AD4 EDCC1_0 EDCD0_0 AG7 AV8 EDCD1_0

BI 6 EDCC0_0 EDCC1_0

6

BI BI 6 EDCD0_0 EDCD1_0

6

BI

EDCC0_1 M1 V1 EDCC1_1 EDCD0_1 AR4 AW15 EDCD1_1

BI 6 EDCC0_1 EDCC1_1

6

BI BI 6 EDCD0_1 EDCD1_1

6

BI

EDCC0_2 J4 W9 EDCC1_2 EDCD0_2 AJ3 BB6 EDCD1_2

BI 6 EDCC0_2 EDCC1_2

6

BI BI 6 EDCD0_2 EDCD1_2

6

BI

EDCC0_3 R5 AD6 EDCC1_3 EDCD0_3 AV2 BA15 EDCD1_3

BI 6 EDCC0_3 EDCC1_3

6

BI BI 6 EDCD0_3 EDCD1_3

6

BI

DDBIC0_0 E1 AD3 DDBIC1_0 DDBID0_0 AJ8 AW6 DDBID1_0

BI 6 DDBIC0_0 DDBIC1_0

6

BI BI 6 DDBID0_0 DDBID1_0

6

BI

DDBIC0_1 M3 B W3 DDBIC1_1 DDBID0_1 AR5 B AY14 DDBID1_1

BI 6 DDBIC0_1

A

DDBIC1_1

6

BI BI 6 DDBID0_1

A

DDBID1_1

6

BI

DDBIC0_2 L9 W8 DDBIC1_2 DDBID0_2 AK1 AY8 DDBID1_2

BI 6 DDBIC0_2

N DDBIC1_2

6

BI BI 6 DDBID0_2

N DDBID1_2

6

BI

(0

DDBIC0_3 U9 K AD7 DDBIC1_3 DDBID0_3 AT4 K BC14 DDBID1_3

BI 6 DDBIC0_3 DDBIC1_3

6

BI BI 6 DDBID0_3 DDBID1_3

6

BI

裴

ADBIC0 W11 C AA11 ADBIC1 ADBID0 AT9 D AT14 ADBID1

BI 6 ADBIC0 ADBIC1

6

BI BI 6 ADBID0 ADBID1

6

BI

M10 AF11 AG12 AP20

OUT OUT OUT OUT

CSC0B_0 CSC1B_0 CSD0B_0 CSD1B_0

6 CSC0B_0 CSC1B_0

6 6 CSD0B_0 CSD1B_0

6

00 RM 亮

W12 AA10 AR11 AM15

OUT OUT OUT OUT

CASC0B CASC1B CASD0B CASD1B

6 CASC0B CASC1B

6 6 CASD0B CASD1B

6

Y12 Y10 AR12 AN14

OUT OUT OUT OUT

RASC0B RASC1B RASD0B RASD1B

6 RASC0B RASC1B

6 6 RASD0B RASD1B

6

R12 AE9 AK8 AP18

OUT OUT OUT OUT

WEC0B WEC1B WED0B WED1B

6 WEC0B WEC1B

6 6 WED0B WED1B

6

Y13 AA13 AP12 AP14

OUT OUT OUT OUT

CKEC0 CKEC1 CKED0 CKED1

6 CKEC0 CKEC1

6 6 CKED0 CKED1

6

P8 AF14 AJ12 AM19

OUT OUT OUT OUT

CLKC0 CLKC1 CLKD0 CLKD1

6 CLKC0 CLKC1

6 6 CLKD0 CLKD1

6

P7 AF13 AJ11 AN19

OUT OUT OUT OUT

CLKC0B CLKC1B CLKD0B CLKD1B

6 CLKC0B CLKC1B

6 6 CLKD0B CLKD1B

6

68 A工 樂

+MVDD +MVDD

1

1

R3618 R3619

40.2R 1% 40.2R

1% 1%

MEM_CALRC MVREF_C MEM_CALRD MVREF_D

2

R3614 1 120R 1% R14 Y14 2120R 1 R3639 AL20 AE14

2

2

MEM_CALRC MVREFDC VVVV34120 MEM_CALRD MVREFDD VVVV34120

76

R11-402AT12-W08 R11-402AT12-W08

VVVV34120 VVVV34120

)

1

1

R11-0121T12-W08 C3612 R3621

R11-0121T12-W08 C3611 R3620

1uF 100R 1uF 100R

程

6.3V 1% 6.3V 1%

VVVV34120 VVVV34120

2

2

C11-105A312-M09

VVVV34120 C11-105A312-M09

VVVV34120

R11-0101T12-W08 R11-0101T12-W08

0)

P12 DRAM_RSTC AK19 DRAM_RSTD

DRAM_RST2_RR DRAM_RST2_R

2

R3629 1 49.9R 1% 2

R3616 1 10R 1%

OUT

DRAM_RST2 6

課

REV 0.90 MVREFD/S = 0.7 * VDDR1 MVREFD/S = 0.7 * VDDR1

VVVV34120 VVVV34120 REV 0.90

1

R11-499AT12-W08 C3617

R11-0100T12-W08 R3627

ellesmere_l4 ellesmere_l4

VVVV34120 120pF 5.1K VVVV34120

50V 1%

B03-0876105-A08 B03-0876105-A08

VVVV34120

2

C11-1211012-S02 VVVV34120

R11-0512T12-W08

MICRO-STAR INT'L CO.,LTD

MS-V341

MSI

Size Document Description Rev

Custom 0004 ELLESMERE MEM CH CD 2.0

Date: Monday, June 27, 2016 Sheet 4 of 26

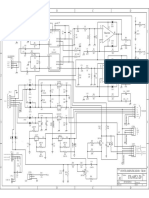

(5) GDDR5 MEMORY CH A/B

00

GDDR 5

+MVDD +MVDD +MVDD +MVDD

23CNOPN001 23CNOPN001 23CNOPN001 23CNOPN001

U2000 U2100 U2200 U2300

DQA0_<0> DQA0_<28> M2 B1 DQA1_<0> DQA1_<5> M2 B1 DQB0_<0> DQB0_<13> M2 B1 DQB1_<0> DQB1_<21> M2 B1

DQA0_<0> 3 DQA1_<0> 3 DQB0_<0> 3 DQB1_<0> 3

28 5 13 21

DQA0_<1> 3 1DQA0_<31> M4 DQA1_<1> DQA1_<6> DQB0_<1> DQB0_<15> DQB1_<1> DQB1_<22>

M

DQ31__DQ7 VDDQ_B1 DQ31__DQ7 VDDQ_B1 DQ31__DQ7 VDDQ_B1 DQ31__DQ7 VDDQ_B1

DQA0_28 DQA1_5 DQB0_13 DQB1_21

B3 M4 B3 M4 B3 M4 B3

DQA0_<1> 3 DQA1_<1> 3 DQB0_<1> 3 DQB1_<1> 3

6 15 22

DQA0_<2> 2 9DQA0_<29> N2 DQA1_<2> DQA1_<4> DQB0_<2> DQB0_<12> DQB1_<2> DQB1_<20>

DQ30__DQ6 VDDQ_B3 DQ30__DQ6 VDDQ_B3 DQ30__DQ6 VDDQ_B3 DQ30__DQ6 VDDQ_B3

DQA0_31 DQA1_6 DQB0_15 DQB1_22

B12 N2 B12 N2 B12 N2 B12

DQA0_<2> 3 DQA1_<2> 3 DQB0_<2> 3 DQB1_<2> 3

4 12 20

DQA0_<3> 3 0DQA0_<30> N4 DQA1_<3> DQA1_<7> DQB0_<3> DQB0_<14> DQB1_<3> DQB1_<23>

DQ29__DQ5 VDDQ_B12 DQ29__DQ5 VDDQ_B12 DQ29__DQ5 VDDQ_B12 DQ29__DQ5 VDDQ_B12

DQA0_29 DQA1_4 DQB0_12 DQB1_20

0

B14 N4 B14 N4 B14 N4 B14

DQA0_<3> 3 DQA1_<3> 3 DQB0_<3> 3 DQB1_<3> 3

7 14 23

DQA0_<4> 2 7DQA0_<27> T2 DQA1_<4> DQA1_<3> DQB0_<4> DQB0_<11> DQB1_<4> DQB1_<19>

DQ28__DQ4 VDDQ_B14 DQ28__DQ4 VDDQ_B14 DQ28__DQ4 VDDQ_B14 DQ28__DQ4 VDDQ_B14

DQA0_30 DQA1_7 DQB0_14 DQB1_23

D1 T2 D1 T2 D1 T2 D1

DQA0_<4> 3 DQA1_<4> 3 DQB0_<4> 3 DQB1_<4> 3

3 11 19

DQA0_<5> 2 6DQA0_<26> T4 DQA1_<5> DQA1_<2> DQB0_<5> DQB0_<8> DQB1_<5> DQB1_<18>

DQ27__DQ3 VDDQ_D1 DQ27__DQ3 VDDQ_D1 DQ27__DQ3 VDDQ_D1 DQ27__DQ3 VDDQ_D1

RD 17 SI

DQA0_27 DQA1_3 DQB0_11 DQB1_19

D3 T4 D3 T4 D3 T4 D3

DQA0_<5> 3 DQA1_<5> 3 DQB0_<5> 3 DQB1_<5> 3

2 8 18

DQA0_<6> 2 4DQA0_<24> V2 DQA1_<6> DQA1_<1> DQB0_<6> DQB0_<10> DQB1_<6> DQB1_<17>

DQ26__DQ2 VDDQ_D3 DQ26__DQ2 VDDQ_D3 DQ26__DQ2 VDDQ_D3 DQ26__DQ2 VDDQ_D3

DQA0_26 DQA1_2 DQB0_8 DQB1_18

D12 V2 D12 V2 D12 V2 D12

DQA0_<6> 3 DQA1_<6> 3 DQB0_<6> 3 DQB1_<6> 3

1 10 17

DQA0_<7> 2 5DQA0_<25> V4 DQA1_<7> DQA1_<0> DQB0_<7> DQB0_<9> DQB1_<7> DQB1_<16>

DQ25__DQ1 VDDQ_D12 DQ25__DQ1 VDDQ_D12 DQ25__DQ1 VDDQ_D12 DQ25__DQ1 VDDQ_D12

DQA0_24 DQA1_1 DQB0_10 DQB1_17

D14 V4 D14 V4 D14 V4 D14

DQA0_<7> 3 DQA1_<7> 3 DQB0_<7> 3 DQB1_<7> 3

0 9 16

DQA0_<8> 1 7DQA0_<17> DQA1_<8> DQA1_<11> DQB0_<8> DQB0_<0> DQB1_<8> DQB1_<26>

DQ24__DQ0 VDDQ_D14 DQ24__DQ0 VDDQ_D14 DQ24__DQ0 VDDQ_D14 DQ24__DQ0 VDDQ_D14

DQA0_25 DQA1_0 DQB0_9 DQB1_16

M13 E5 M13 E5 M13 E5 M13 E5

DQA0_<8> 3 DQA1_<8> 3 DQB0_<8> 3 DQB1_<8> 3

11 0 26

DQA0_<9> 2 3DQA0_<23> DQA1_<9> DQA1_<8> DQB0_<9> DQB0_<7> DQB1_<9> DQB1_<27>

DQ23__DQ15 VDDQ_E5 DQ23__DQ15 VDDQ_E5 DQ23__DQ15 VDDQ_E5 DQ23__DQ15 VDDQ_E5

DQA0_17 DQA1_11 DQB0_0 DQB1_26

M11 E10 M11 E10 M11 E10 M11 E10

DQA0_<9> 3 DQA1_<9> 3 DQB0_<9> 3 DQB1_<9> 3

8 7 27

DQA0_<10> 1 6DQA0_<16>N13 DQA1_<10> DQA1_<10> DQB0_<10> DQB0_<1> DQB1_<10> DQB1_<24>

DQ22__DQ14 VDDQ_E10 DQ22__DQ14 VDDQ_E10 DQ22__DQ14 VDDQ_E10 DQ22__DQ14 VDDQ_E10

DQA0_23 DQA1_8 DQB0_7 DQB1_27

F1 N13 F1 N13 F1 N13 F1

DQA0_<10> 3 DQA1_<10> 3 DQB0_<10> 3 DQB1_<10> 3

10 1 24

DQA0_<11> 2 2DQA0_<22>N11 DQA1_<11> DQA1_<9> DQB0_<11> DQB0_<6> DQB1_<11> DQB1_<25>

DQ21__DQ13 VDDQ_F1 DQ21__DQ13 VDDQ_F1 DQ21__DQ13 VDDQ_F1 DQ21__DQ13 VDDQ_F1

DQA0_16 DQA1_10 DQB0_1 DQB1_24

F3 N11 F3 N11 F3 N11 F3

DQA0_<11> 3 DQA1_<11> 3 DQB0_<11> 3 DQB1_<11> 3

9 6 25

DQA0_<12> 1 8DQA0_<18>T13 DQA1_<12> DQA1_<12> DQB0_<12> DQB0_<3> DQB1_<12> DQB1_<28>

DQ20__DQ12 VDDQ_F3 DQ20__DQ12 VDDQ_F3 DQ20__DQ12 VDDQ_F3 DQ20__DQ12 VDDQ_F3

DQA0_22 DQA1_9 DQB0_6 DQB1_25

F12 T13 F12 T13 F12 T13 F12

DQA0_<12> 3 DQA1_<12> 3 DQB0_<12> 3 DQB1_<12> 3

12 3 28

DQA0_<13> 2 1DQA0_<21>T11 DQA1_<13> DQA1_<13> DQB0_<13> DQB0_<5> DQB1_<13> DQB1_<30>

DQ19__DQ11 VDDQ_F12 DQ19__DQ11 VDDQ_F12 DQ19__DQ11 VDDQ_F12 DQ19__DQ11 VDDQ_F12

DQA0_18 DQA1_12 DQB0_3 DQB1_28

F14 T11 F14 T11 F14 T11 F14

DQA0_<13> 3 DQA1_<13> 3 DQB0_<13> 3 DQB1_<13> 3

(C 96 C

13 5 30

DQA0_<14> 1 9DQA0_<19>V13 DQA1_<14> DQA1_<14> DQB0_<14> DQB0_<2> DQB1_<14> DQB1_<31>

DQ18__DQ10 VDDQ_F14 DQ18__DQ10 VDDQ_F14 DQ18__DQ10 VDDQ_F14 DQ18__DQ10 VDDQ_F14

DQA0_21 DQA1_13 DQB0_5 DQB1_30

G2 V13 G2 V13 G2 V13 G2

DQA0_<14> 3 DQA1_<14> 3 DQB0_<14> 3 DQB1_<14> 3

14 2 31

DQA0_<15> 2 0DQA0_<20>V11 DQA1_<15> DQA1_<15> DQB0_<15> DQB0_<4> DQB1_<15> DQB1_<29>

DQ17__DQ9 VDDQ_G2 DQ17__DQ9 VDDQ_G2 DQ17__DQ9 VDDQ_G2 DQ17__DQ9 VDDQ_G2

DQA0_19 DQA1_14 DQB0_2 DQB1_31

G13 V11 G13 V11 G13 V11 G13

DQA0_<15> 3 DQA1_<15> 3 DQB0_<15> 3 DQB1_<15> 3

15 4 29

DQA0_<16> 5 DQA0_<5> F13 DQA1_<16> DQA1_<31> DQB0_<16> DQB0_<30> DQB1_<16> DQB1_<15>

DQ16__DQ8 VDDQ_G13 DQ16__DQ8 VDDQ_G13 DQ16__DQ8 VDDQ_G13 DQ16__DQ8 VDDQ_G13

DQA0_20 DQA1_15 DQB0_4 DQB1_29

H3 F13 H3 F13 H3 F13 H3

DQA0_<16> 3 DQA1_<16> 3 DQB0_<16> 3 DQB1_<16> 3

31 30 15

DQA0_<17> 6 DQA0_<6> F11 DQA1_<17> DQA1_<24> DQB0_<17> DQB0_<29> DQB1_<17> DQB1_<8>

DQ15__DQ23 VDDQ_H3 DQ15__DQ23 VDDQ_H3 DQ15__DQ23 VDDQ_H3 DQ15__DQ23 VDDQ_H3

DQA0_5 DQA1_31 DQB0_30 DQB1_15

H12 F11 H12 F11 H12 F11 H12

DQA0_<17> 3 DQA1_<17> 3 DQB0_<17> 3 DQB1_<17> 3

24 29 8

DQA0_<18> 4 DQA0_<4> E13 DQA1_<18> DQA1_<29> DQB0_<18> DQB0_<28> DQB1_<18> DQB1_<14>

DQ14__DQ22 VDDQ_H12 DQ14__DQ22 VDDQ_H12 DQ14__DQ22 VDDQ_H12 DQ14__DQ22 VDDQ_H12

DQA0_6 DQA1_24 DQB0_29 DQB1_8

K3 E13 K3 E13 K3 E13 K3

DQA0_<18> 3 DQA1_<18> 3 DQB0_<18> 3 DQB1_<18> 3

29 28 14

DQA0_<19> 7 DQA0_<7> E11 DQA1_<19> DQA1_<25> DQB0_<19> DQB0_<31> DQB1_<19> DQB1_<10>

DQ13__DQ21 VDDQ_K3 DQ13__DQ21 VDDQ_K3 DQ13__DQ21 VDDQ_K3 DQ13__DQ21 VDDQ_K3

DQA0_4 DQA1_29 DQB0_28 DQB1_14

K12 E11 K12 E11 K12 E11 K12

DQA0_<19> 3 DQA1_<19> 3 DQB0_<19> 3 DQB1_<19> 3

25 31 10

DQA0_<20> 3 DQA0_<3> B13 DQA1_<20> DQA1_<28> DQB0_<20> DQB0_<27> DQB1_<20> DQB1_<12>

DQ12__DQ20 VDDQ_K12 DQ12__DQ20 VDDQ_K12 DQ12__DQ20 VDDQ_K12 DQ12__DQ20 VDDQ_K12

DQA0_7 DQA1_25 DQB0_31 DQB1_10

L2 B13 L2 B13 L2 B13 L2

DQA0_<20> 3 DQA1_<20> 3 DQB0_<20> 3 DQB1_<20> 3

28 27 12

DQA0_<21> 2 DQA0_<2> B11 DQA1_<21> DQA1_<26> DQB0_<21> DQB0_<26> DQB1_<21> DQB1_<9>

DQ11__DQ19 VDDQ_L2 DQ11__DQ19 VDDQ_L2 DQ11__DQ19 VDDQ_L2 DQ11__DQ19 VDDQ_L2

DQA0_3 DQA1_28 DQB0_27 DQB1_12

)2 7 ON

L13 B11 L13 B11 L13 B11 L13

DQA0_<21> 3 DQA1_<21> 3 DQB0_<21> 3 DQB1_<21> 3

26 26 9

DQA0_<22> 1 DQA0_<1> A13 DQA1_<22> DQA1_<30> DQB0_<22> DQB0_<24> DQB1_<22> DQB1_<13>

DQ10__DQ18 VDDQ_L13 DQ10__DQ18 VDDQ_L13 DQ10__DQ18 VDDQ_L13 DQ10__DQ18 VDDQ_L13

DQA0_2 DQA1_26 DQB0_26 DQB1_9

M1 A13 M1 A13 M1 A13 M1

DQA0_<22> 3 DQA1_<22> 3 DQB0_<22> 3 DQB1_<22> 3

30 24 13

DQA0_<23> 0 DQA0_<0> A11 DQA1_<23> DQA1_<27> DQB0_<23> DQB0_<25> DQB1_<23> DQB1_<11>

DQ9__DQ17 VDDQ_M1 DQ9__DQ17 VDDQ_M1 DQ9__DQ17 VDDQ_M1 DQ9__DQ17 VDDQ_M1

DQA0_1 DQA1_30 DQB0_24 DQB1_13

M3 A11 M3 A11 M3 A11 M3

DQA0_<23> 3 DQA1_<23> 3 DQB0_<23> 3 DQB1_<23> 3

27 25 11

DQA0_<24> 1 1DQA0_<11> F2 DQA1_<24> DQA1_<18> DQB0_<24> DQB0_<19> DQB1_<24> DQB1_<2>

DQ8__DQ16 VDDQ_M3 DQ8__DQ16 VDDQ_M3 DQ8__DQ16 VDDQ_M3 DQ8__DQ16 VDDQ_M3

DQA0_0 DQA1_27 DQB0_25 DQB1_11

M12 F2 M12 F2 M12 F2 M12

DQA0_<24> 3 DQA1_<24> 3 DQB0_<24> 3 DQB1_<24> 3

18 19 2

DQA0_<25> 1 0DQA0_<10> F4 DQA1_<25> DQA1_<17> DQB0_<25> DQB0_<18> DQB1_<25> DQB1_<0>

DQ7__DQ31 VDDQ_M12 DQ7__DQ31 VDDQ_M12 DQ7__DQ31 VDDQ_M12 DQ7__DQ31 VDDQ_M12

DQA0_11 DQA1_18 DQB0_19 DQB1_2

M14 F4 M14 F4 M14 F4 M14

DQA0_<25> 3 DQA1_<25> 3 DQB0_<25> 3 DQB1_<25> 3

17 18 0

DQA0_<26> 8 DQA0_<8> E2 DQA1_<26> DQA1_<19> DQB0_<26> DQB0_<17> DQB1_<26> DQB1_<3>

DQ6__DQ30 VDDQ_M14 DQ6__DQ30 VDDQ_M14 DQ6__DQ30 VDDQ_M14 DQ6__DQ30 VDDQ_M14

DQA0_10 DQA1_17 DQB0_18 DQB1_0

N5 E2 N5 E2 N5 E2 N5

DQA0_<26> 3 DQA1_<26> 3 DQB0_<26> 3 DQB1_<26> 3

19 17 3

DQA0_<27> 9 DQA0_<9> E4 DQA1_<27> DQA1_<16> DQB0_<27> DQB0_<16> DQB1_<27> DQB1_<1>

DQ5__DQ29 VDDQ_N5 DQ5__DQ29 VDDQ_N5 DQ5__DQ29 VDDQ_N5 DQ5__DQ29 VDDQ_N5

DQA0_8 DQA1_19 DQB0_17 DQB1_3

N10 E4 N10 E4 N10 E4 N10

DQA0_<27> 3 DQA1_<27> 3 DQB0_<27> 3 DQB1_<27> 3

16 16 1

DQA0_<28> 1 2DQA0_<12> B2 DQA1_<28> DQA1_<21> DQB0_<28> DQB0_<20> DQB1_<28> DQB1_<4>

DQ4__DQ28 VDDQ_N10 DQ4__DQ28 VDDQ_N10 DQ4__DQ28 VDDQ_N10 DQ4__DQ28 VDDQ_N10

DQA0_9 DQA1_16 DQB0_16 DQB1_1

P1 B2 P1 B2 P1 B2 P1

DQA0_<28> 3 DQA1_<28> 3 DQB0_<28> 3 DQB1_<28> 3

21 20 4

DQA0_<29> 1 3DQA0_<13> B4 DQA1_<29> DQA1_<23> DQB0_<29> DQB0_<21> DQB1_<29> DQB1_<7>

DQ3__DQ27 VDDQ_P1 DQ3__DQ27 VDDQ_P1 DQ3__DQ27 VDDQ_P1 DQ3__DQ27 VDDQ_P1

DQA0_12 DQA1_21 DQB0_20 DQB1_4

P3 B4 P3 B4 P3 B4 P3

F

DQA0_<29> 3 DQA1_<29> 3 DQB0_<29> 3 DQB1_<29> 3

23 21 7

DQA0_<30> 1 5DQA0_<15> A2 DQA1_<30> DQA1_<20> DQB0_<30> DQB0_<22> DQB1_<30> DQB1_<5>

DQ2__DQ26 VDDQ_P3 DQ2__DQ26 VDDQ_P3 DQ2__DQ26 VDDQ_P3 DQ2__DQ26 VDDQ_P3

DQA0_13 DQA1_23 DQB0_21 DQB1_7

0

P12 A2 P12 A2 P12 A2 P12

DQA0_<30> 3 DQA1_<30> 3 DQB0_<30> 3 DQB1_<30> 3

20 22 5

DQA0_<31> 1 4DQA0_<14> A4 DQA1_<31> DQA1_<22> DQB0_<31> DQB0_<23> DQB1_<31> DQB1_<6>

DQ1__DQ25 VDDQ_P12 DQ1__DQ25 VDDQ_P12 DQ1__DQ25 VDDQ_P12 DQ1__DQ25 VDDQ_P12

DQA0_15 DQA1_20 DQB0_22 DQB1_5

P14 A4 P14 A4 P14 A4 P14

DQA0_<31> 3 DQA1_<31> 3 DQB0_<31> 3 DQB1_<31> 3

22 23 6

DQ0__DQ24 VDDQ_P14 DQ0__DQ24 VDDQ_P14 DQ0__DQ24 VDDQ_P14 DQ0__DQ24 VDDQ_P14

DQA0_14 DQA1_22 DQB0_23 DQB1_6

VDDQ_T1 T1 VDDQ_T1 T1 VDDQ_T1 T1 VDDQ_T1 T1

T3 T3 T3 T3

石 17 jo ID

VDDQ_T3 VDDQ_T3 VDDQ_T3 VDDQ_T3

VDDQ_T12 T12 VDDQ_T12 T12 VDDQ_T12 T12 VDDQ_T12 T12

VDDQ_T14 T14 VDDQ_T14 T14 VDDQ_T14 T14 VDDQ_T14 T14

+MVDD +MVDD +MVDD

MAA0_<0> MAA0_<8> J5 MAA1_<0> MAA1_<8> J5 +MVDD MAB0_<0> MAB0_<8> J5 MAB1_<0> MAB1_<8> J5

MAA0_<0> MAA0_<1> 3 MAA0_<7>

RFU_A12_NC

MAA1_<0> MAA1_<1> 3 MAA1_<0>

RFU_A12_NC

MAB0_<0> MAB0_<1> 3 MAB0_<7>

RFU_A12_NC

MAB1_<0> MAB1_<1> 3MAB1_<0> RFU_A12_NC

K4 C5 K4 C5 K4 C5 K4 C5

8 8 8 8

MAA0_<1> MAA0_<2> 3 MAA0_<6>

A7_A8__A0_A10 VDD_C5

MAA1_<1> MAA1_<2> 3 MAA1_<1>

A7_A8__A0_A10 VDD_C5

MAB0_<1> MAB0_<2> 3 MAB0_<6>

A7_A8__A0_A10 VDD_C5

MAB1_<1> MAB1_<2> 3MAB1_<1> A7_A8__A0_A10 VDD_C5

K5 C10 K5 C10 K5 C10 K5 C10

7 0 7 0

MAA0_<2> MAA0_<3> 3 MAA0_<5>

A6_A11__A1_A9 VDD_C10

MAA1_<2> MAA1_<3> 3 MAA1_<3>

A6_A11__A1_A9 VDD_C10

MAB0_<2> MAB0_<3> 3 MAB0_<5>

A6_A11__A1_A9 VDD_C10

MAB1_<2> MAB1_<3> 3MAB1_<3> A6_A11__A1_A9 VDD_C10

K10 D11 K10 D11 K10 D11 K10 D11

6 1 6 1

MAA0_<3> MAA0_<4> 3 MAA0_<4>

A5_BA1__A3_BA3 VDD_D11

MAA1_<3> MAA1_<4> 3 MAA1_<2>

A5_BA1__A3_BA3 VDD_D11

MAB0_<3> MAB0_<4> 3 MAB0_<4>

A5_BA1__A3_BA3 VDD_D11

MAB1_<3> MAB1_<4> 3MAB1_<2> A5_BA1__A3_BA3 VDD_D11

K11 G1 K11 G1 K11 G1 K11 G1

5 3 5 3

MAA0_<4> MAA0_<5> 3 MAA0_<3> MAA1_<4> MAA1_<5> 3 MAA1_<5> MAB0_<4> MAB0_<5> 3 MAB0_<3> MAB1_<4> MAB1_<5> 3MAB1_<5>

阿 09 ne EN

A4_BA2__A2_BA0 VDD_G1 A4_BA2__A2_BA0 VDD_G1 A4_BA2__A2_BA0 VDD_G1 A4_BA2__A2_BA0 VDD_G1

H10 G4 H10 G4 H10 G4 H10 G4

4 2 4 2

MAA0_<5> MAA0_<6> 3 MAA0_<2>

A3_BA3__A5_BA1 VDD_G4

MAA1_<5> MAA1_<6> 3 MAA1_<4>

A3_BA3__A5_BA1 VDD_G4

MAB0_<5> MAB0_<6> 3 MAB0_<2>

A3_BA3__A5_BA1 VDD_G4

MAB1_<5> MAB1_<6> 3MAB1_<4> A3_BA3__A5_BA1 VDD_G4

H11 G11 H11 G11 H11 G11 H11 G11

3 5 3 5

MAA0_<6> MAA0_<7> 3 MAA0_<1>

A2_BA0__A4_BA2 VDD_G11

MAA1_<6> MAA1_<7> 3 MAA1_<6>

A2_BA0__A4_BA2 VDD_G11

MAB0_<6> MAB0_<7> 3 MAB0_<1>

A2_BA0__A4_BA2 VDD_G11

MAB1_<6> MAB1_<7> 3MAB1_<6> A2_BA0__A4_BA2 VDD_G11

H5 G14 H5 G14 H5 G14 H5 G14

2 4 2 4

MAA0_<7> MAA0_<8> 3 MAA0_<0>

A1_A9__A6_A11 VDD_G14

MAA1_<7> MAA1_<8> 3 MAA1_<7>

A1_A9__A6_A11 VDD_G14

MAB0_<7> MAB0_<8> 3 MAB0_<0>

A1_A9__A6_A11 VDD_G14

MAB1_<7> MAB1_<8> 3MAB1_<7> A1_A9__A6_A11 VDD_G14

H4 L1 H4 L1 H4 L1 H4 L1

1 6 1 6

MAA0_<8> 3 A0_A10__A7_A8 VDD_L1

MAA1_<8> 3 A0_A10__A7_A8 VDD_L1

MAB0_<8> 3 A0_A10__A7_A8 VDD_L1

MAB1_<8> 3 A0_A10__A7_A8 VDD_L1

L4 L4 L4 L4

0 7 0 7

VDD_L4 VDD_L4 VDD_L4 VDD_L4

VDD_L11 L11 VDD_L11 L11 VDD_L11 L11 VDD_L11 L11

VDD_L14 L14 VDD_L14 L14 VDD_L14 L14 VDD_L14 L14

D4 P11 D4 P11 D4 P11 D4 P11

IN IN IN IN

WCKA0_0 WCKA1_1 WCKB0_1 WCKB1_0

3 WCK01__WCK23 VDD_P11 3 WCK01__WCK23 VDD_P11 3 WCK01__WCK23 VDD_P11 3 WCK01__WCK23 VDD_P11

鋒 19 pe TI

D5 R5 D5 R5 D5 R5 D5 R5

IN IN IN IN

WCKA0B_0 WCKA1B_1 WCKB0B_1 WCKB1B_0

3 WCK01#__WCK23# VDD_R5 3 WCK01#__WCK23# VDD_R5 3 WCK01#__WCK23# VDD_R5 3 WCK01#__WCK23# VDD_R5

VDD_R10 R10 VDD_R10 R10 VDD_R10 R10 VDD_R10 R10

P4 P4 P4 P4

IN IN IN IN

WCKA0_1 WCKA1_0 WCKB0_0 WCKB1_1

3 WCK23__WCK01 3 WCK23__WCK01 3 WCK23__WCK01 3 WCK23__WCK01

P5 P5 P5 P5

IN IN IN IN

WCKA0B_1 WCKA1B_0 WCKB0B_0 WCKB1B_1

3 WCK23#__WCK01# 3 WCK23#__WCK01# 3 WCK23#__WCK01# 3 WCK23#__WCK01#

VSSQ_A1 A1 VSSQ_A1 A1 VSSQ_A1 A1 VSSQ_A1 A1

R2 A3 R2 A3 R2 A3 R2 A3

OUT OUT OUT OUT

EDCA0_3 EDCA1_0 EDCB0_1 EDCB1_2

3 EDC3__EDC0 VSSQ_A3 3 EDC3__EDC0 VSSQ_A3 3 EDC3__EDC0 VSSQ_A3 3 EDC3__EDC0 VSSQ_A3

R13 A12 R13 A12 R13 A12 R13 A12

OUT OUT OUT OUT

EDCA0_2 EDCA1_1 EDCB0_0 EDCB1_3

3 EDC2__EDC1 VSSQ_A12 3 EDC2__EDC1 VSSQ_A12 3 EDC2__EDC1 VSSQ_A12 3 EDC2__EDC1 VSSQ_A12

C13 A14 C13 A14 C13 A14 C13 A14

OUT OUT OUT OUT

EDCA0_0 EDCA1_3 EDCB0_3 EDCB1_1

3 EDC1__EDC2 VSSQ_A14 3 EDC1__EDC2 VSSQ_A14 3 EDC1__EDC2 VSSQ_A14 3 EDC1__EDC2 VSSQ_A14

02 i( AL

C2 C1 C2 C1 C2 C1 C2 C1

OUT OUT OUT OUT

EDCA0_1 EDCA1_2 EDCB0_2 EDCB1_0

3 EDC0__EDC3 VSSQ_C1 3 EDC0__EDC3 VSSQ_C1 3 EDC0__EDC3 VSSQ_C1 3 EDC0__EDC3 VSSQ_C1

VSSQ_C3 C3 VSSQ_C3 C3 VSSQ_C3 C3 VSSQ_C3 C3

DDBIA0_3 P2 C4 DDBIA1_0 P2 C4 DDBIB0_1 P2 C4 DDBIB1_2 P2 C4

BI 3 DBI3#__DBI0# VSSQ_C4 BI 3 DBI3#__DBI0# VSSQ_C4 BI 3 DBI3#__DBI0# VSSQ_C4 BI 3 DBI3#__DBI0# VSSQ_C4

DDBIA0_2 P13 C11 DDBIA1_1 P13 C11 DDBIB0_0 P13 C11 DDBIB1_3 P13 C11

BI 3 DBI2#__DBI1# VSSQ_C11 BI 3 DBI2#__DBI1# VSSQ_C11 BI 3 DBI2#__DBI1# VSSQ_C11 BI 3 DBI2#__DBI1# VSSQ_C11

DDBIA0_0 D13 C12 DDBIA1_3 D13 C12 DDBIB0_3 D13 C12 DDBIB1_1 D13 C12

BI 3 DBI1#__DBI2# VSSQ_C12 BI 3 DBI1#__DBI2# VSSQ_C12 BI 3 DBI1#__DBI2# VSSQ_C12 BI 3 DBI1#__DBI2# VSSQ_C12

DDBIA0_1 D2 C14 DDBIA1_2 D2 C14 DDBIB0_2 D2 C14 DDBIB1_0 D2 C14

BI 3 DBI0#__DBI3# VSSQ_C14 BI 3 DBI0#__DBI3# VSSQ_C14 BI 3 DBI0#__DBI3# VSSQ_C14 BI 3 DBI0#__DBI3# VSSQ_C14

VSSQ_E1 E1 VSSQ_E1 E1 VSSQ_E1 E1 VSSQ_E1 E1

VSSQ_E3 E3 VSSQ_E3 E3 VSSQ_E3 E3 VSSQ_E3 E3

VSSQ_E12 E12 VSSQ_E12 E12 VSSQ_E12 E12 VSSQ_E12 E12

+MVDD +MVDD +MVDD +MVDD

(0

G3 E14 G3 E14 G3 E14 G3 E14

IN IN IN IN

RASA0B CASA1B RASB0B CASB1B

3 RAS#__CAS# VSSQ_E14 3 RAS#__CAS# VSSQ_E14 3 RAS#__CAS# VSSQ_E14 3 RAS#__CAS# VSSQ_E14

L3 F5 L3 F5 L3 F5 L3 F5

IN IN IN IN

CASA0B RASA1B CASB0B RASB1B

裴

3 CAS#__RAS# VSSQ_F5 3 CAS#__RAS# VSSQ_F5 3 CAS#__RAS# VSSQ_F5 3 CAS#__RAS# VSSQ_F5

2

R2001 1 60.4R 1% VSSQ_F10 F10 2

R2101 1 60.4R 1% VSSQ_F10 F10 2

R2201 1 60.4R 1% VSSQ_F10 F10 2

R2301 1 60.4R 1% VSSQ_F10 F10

2

R2000 1 60.4R 1% VSSQ_H2 H2 2

R2100 1 60.4R 1% VSSQ_H2 H2 2

R2200 1 60.4R 1% VSSQ_H2 H2 2

R2300 1 60.4R 1% VSSQ_H2 H2

VVVV34110S J3 H13 VVVV34110S J3 H13 VVVV34110S J3 H13 VVVV34110S J3 H13

IN IN IN IN

CKEA0 CKEA1 CKEB0 CKEB1

3 CKE# VSSQ_H13 3 CKE# VSSQ_H13 3 CKE# VSSQ_H13 3 CKE# VSSQ_H13

R11-604AT12-W08

VVVV34110S J11 K2 R11-604AT12-W08

VVVV34110S J11 K2 R11-604AT12-W08

VVVV34110S J11 K2 R11-604AT12-W08

VVVV34110S J11 K2

IN IN IN IN

CLKA0B CLKA1B CLKB0B CLKB1B

3 CK# VSSQ_K2 3 CK# VSSQ_K2 3 CK# VSSQ_K2 3 CK# VSSQ_K2

R11-604AT12-W08 J12 K13 R11-604AT12-W08 J12 K13 R11-604AT12-W08 J12 K13 R11-604AT12-W08 J12 K13

IN IN IN IN

CLKA0 CLKA1 CLKB0 CLKB1

3 CK VSSQ_K13 3 CK VSSQ_K13 3 CK VSSQ_K13 3 CK VSSQ_K13

VSSQ_M5 M5 VSSQ_M5 M5 VSSQ_M5 M5 VSSQ_M5 M5

00 RM 亮

VSSQ_M10 M10 VSSQ_M10 M10 VSSQ_M10 M10 VSSQ_M10 M10

G12 N1 G12 N1 G12 N1 G12 N1

IN IN IN IN

CSA0B_0 WEA1B CSB0B_0 WEB1B

3 CS#__WE# VSSQ_N1 3 CS#__WE# VSSQ_N1 3 CS#__WE# VSSQ_N1 3 CS#__WE# VSSQ_N1

L12 N3 L12 N3 L12 N3 L12 N3

IN IN IN IN

WEA0B CSA1B_0 WEB0B CSB1B_0

3 WE#__CS# VSSQ_N3 3 WE#__CS# VSSQ_N3 3 WE#__CS# VSSQ_N3 3 WE#__CS# VSSQ_N3

VSSQ_N12 N12 VSSQ_N12 N12 VSSQ_N12 N12 VSSQ_N12 N12

VSSQ_N14 N14 VSSQ_N14 N14 VSSQ_N14 N14 VSSQ_N14 N14

ZQ_A0 ZQ_A1 ZQ_B0 ZQ_B1

2

R2002 1 120R 1% J13 ZQ VSSQ_R1 R1 R21021 2

120R 1% J13 ZQ VSSQ_R1 R1 2

R2202 1 120R 1% J13 ZQ VSSQ_R1 R1 R2302 1 2

120R 1% J13 ZQ VSSQ_R1 R1

SEN_A0 SEN_A1 SEN_B0 SEN_B1

R20031 2

1K 5% J10 SEN VSSQ_R3 R3 R21031 2

1K 5% J10 SEN VSSQ_R3 R3 R2203 1 2

1K 5% J10 SEN VSSQ_R3 R3 R2303 1 2

1K 5% J10 SEN VSSQ_R3 R3

VVVV34110S VSSQ_R4 R4 VVVV34110S VSSQ_R4 R4 VVVV34110S VSSQ_R4 R4 VVVV34110S VSSQ_R4 R4

R11-0121T12-W08

VVVV34110S R11 R11-0121T12-W08

VVVV34110S R11 R11-0121T12-W08

VVVV34110S R11 R11-0121T12-W08

VVVV34110S R11

68 A工 樂

IN IN 3,5 IN IN

DRAM_RST1 DRAM_RST1 DRAM_RST1

3,5 VSSQ_R11 VSSQ_R11 3,5 VSSQ_R11 3,5 VSSQ_R11

R11-0102032-W08 R11-0102032-W08 R11-0102032-W08 R11-0102032-W08

DRAM_RST1

J2 RESET# VSSQ_R12 R12 J2 RESET# VSSQ_R12 R12 J2 RESET# VSSQ_R12 R12 J2 RESET# VSSQ_R12 R12

MF_A0 MF_A1 MF_B0 MF_B1

R20041 2

1K 5% J1 MF VSSQ_R14 R14 +MVDD R21041 2

1K 5% J1 MF VSSQ_R14 R14 R2204 1 2

1K 5% J1 MF VSSQ_R14 R14 +MVDD R2304 1 2

1K 5% J1 MF VSSQ_R14 R14

VSSQ_V1 V1 VSSQ_V1 V1 VSSQ_V1 V1 VSSQ_V1 V1

VVVV34110S VSSQ_V3 V3 VVVV34110S VSSQ_V3 V3 VVVV34110S VSSQ_V3 V3 VVVV34110S VSSQ_V3 V3

R11-0102032-W08 VSSQ_V12 V12 R11-0102032-W08 VSSQ_V12 V12 R11-0102032-W08 VSSQ_V12 V12 R11-0102032-W08 VSSQ_V12 V12

VSSQ_V14 V14 VSSQ_V14 V14 VSSQ_V14 V14 VSSQ_V14 V14

A5 Vpp_NC A5 Vpp_NC A5 Vpp_NC A5 Vpp_NC

V5 Vpp_NC1 V5 Vpp_NC1 V5 Vpp_NC1 V5 Vpp_NC1

76

VSS_B5 B5 VSS_B5 B5 VSS_B5 B5 VSS_B5 B5

A10 B10 A10 B10 A10 B10 A10 B10

)

VREFD1 VSS_B10 VREFD1 VSS_B10 VREFD1 VSS_B10 VREFD1 VSS_B10

V10 VREFD2 VSS_D10 D10 V10 VREFD2 VSS_D10 D10 V10 VREFD2 VSS_D10 D10 V10 VREFD2 VSS_D10 D10

G5 G5 G5 G5

程

VSS_G5 VSS_G5 VSS_G5 VSS_G5

VSS_G10 G10 VSS_G10 G10 VSS_G10 G10 VSS_G10 G10

VSS_H1 H1 VSS_H1 H1 VSS_H1 H1 VSS_H1 H1

VSS_H14 H14 VSS_H14 H14 VSS_H14 H14 VSS_H14 H14

+MVDD 2

R2009 1 2.37K 1% VSS_K1 K1 +MVDD 2

R2109 1 2.37K 1% VSS_K1 K1 +MVDD 2

R2209 1 2.37K 1% VSS_K1 K1 +MVDD 2

R2309 1 2.37K 1% VSS_K1 K1

0)

2

R2010 1 5.49K 1% J14 VREFC VSS_K14 K14 2

R2110 1 5.49K 1% J14 VREFC VSS_K14 K14 2

R2210 1 5.49K 1% J14 VREFC VSS_K14 K14 2

R2310 1 5.49K 1% J14 VREFC VSS_K14 K14

VREFC_A0 VREFC_A1 VREFC_B0 VREFC_B1

VVVV34110S

C2005 1uF 6.3V VSS_L5 L5 VVVV34110S

C2105 1uF 6.3V VSS_L5 L5 VVVV34110S

C2205 1uF 6.3V VSS_L5 L5 VVVV34110S

C2305 1uF 6.3V VSS_L5 L5

R11-2371T12-W08

VVVV34110S VSS_L10 L10 R11-2371T12-W08

VVVV34110S VSS_L10 L10 R11-2371T12-W08

VVVV34110S VSS_L10 L10 R11-2371T12-W08

VVVV34110S VSS_L10 L10

R11-5491T22-W08

VVVV34110S VSS_P10 P10 R11-5491T22-W08

VVVV34110S VSS_P10 P10 R11-5491T22-W08

VVVV34110S VSS_P10 P10 R11-5491T22-W08

VVVV34110S VSS_P10 P10

課

C11-105A312-M09 J4 T5 C11-105A312-M09 J4 T5 C11-105A312-M09 J4 T5 C11-105A312-M09 J4 T5

IN IN IN IN

ADBIA0 ADBIA1 ADBIB0 ADBIB1

3 ABI# VSS_T5 3 ABI# VSS_T5 3 ABI# VSS_T5 3 ABI# VSS_T5

VSS_T10 T10 VSS_T10 T10 VSS_T10 T10 VSS_T10 T10

VVVV34110S VVVV34110S VVVV34110S VVVV34110S

M12-5GC4HC5-H2A M12-5GC4HC5-H2A M12-5GC4HC5-H2A M12-5GC4HC5-H2A

+MVDD

Reserved. detail please check BOM

+MVDD +MVDD +MVDD +MVDD

1

1

+ + + +

C2218

C2361 C2362 C2363 C2364

C2117

C2317

470uF 470uF 470uF 470uF

2V 2V 2V 2V

C2007

C2008

C2009

C2010

C2012

C2013

C2014

C2015

C2107

C2108

C2109

C2110

C2112

C2115

C2116

C2206

C2208

C2209

C2211

C2212

C2213

C2214

C2306

C2308

C2309

C2311

C2312

C2314

C2316

XXXV34110SXXXV34110S XXXV34110S XXXV34110S

2

2

<New PN> <New PN> <New PN> <New PN>

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

0.1uF

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

C11-1042312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09 C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-1042312-M09

C11-105A312-M09

C11-1042312-M09 C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-1042312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09 C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-1042312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

+MVDD +MVDD +MVDD +MVDD

MICRO-STAR INT'L CO.,LTD

MS-V341

1

1

C2019

C2020

C2023

C2024

C2025

C2026

C2028

C2029

C2040

C2041

C2118

C2119

C2120

C2121

C2122

C2126

C2127

C2129

C2140

C2141

C2219

C2220

C2223

C2226

C2227

C2228

C2229

C2230

C2240

C2241

C2319

C2321

C2322

C2323

C2324

C2325

C2326

C2328

C2340

C2341

MSI

22uF 22uF 22uF 22uF 22uF 22uF 22uF 22uF

4V 4V 4V 4V 4V 4V 4V 4V

VVVV34110S

VVVV34110S XXXV34110S

VVVV34110S VVVV34110SXXXV34110S VVVV34110S

XXXV34110S Size Document Description Rev

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

1uF

0005 GDDR5 MEM CH AB

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

VVVV34110S

2

C11-226A224-M09

C11-226A224-M09 <New PN>C11-226A224-M09 C11-226A224-M09

<New PN> C11-226A224-M09

<New PN>

C11-1042312-M09

C11-1042312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09 C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-1042312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09 C11-1042312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-1042312-M09

C11-105A312-M09

C11-105A312-M09 C11-1042312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09

C11-1042312-M09

C11-105A312-M09

C11-105A312-M09

C11-105A312-M09 Custom 2.0

Date: Tuesday, June 28, 2016 Sheet 5 of 26

(6) GDDR5 MEMORY CH C/D

00

+MVDD +MVDD +MVDD +MVDD

23CNOPN001 23CNOPN001 23CNOPN001 23CNOPN001

U2400 U2500 U2600 U2700

DQC0_<0> DQC0_<29> M2 B1 DQC1_<0> DQC1_<12> M2 B1 DQD0_<0> DQD0_<13> M2 B1 DQD1_<0> DQD1_<20> M2 B1

DQC0_<0> 4 DQC1_<0> 4 DQD0_<0> 4 DQD1_<0> 4

29 12 13 20

DQC0_<1> DQC0_<31> DQC1_<1> DQC1_<13> DQD0_<1> DQD0_<15> DQD1_<1> DQD1_<21>

DQ31__DQ7 VDDQ_B1 DQ31__DQ7 VDDQ_B1 DQ31__DQ7 VDDQ_B1 DQ31__DQ7 VDDQ_B1

DQC0_29 DQC1_12 DQD0_13 DQD1_20

M4 B3 M4 B3 M4 B3 M4 B3

DQC0_<1> 4 DQC1_<1> 4 DQD0_<1> 4 DQD1_<1> 4

31 13 15 21

DQC0_<2> DQC0_<28> DQC1_<2> DQC1_<14> DQD0_<2> DQD0_<12> DQD1_<2> DQD1_<23>

M

DQ30__DQ6 VDDQ_B3 DQ30__DQ6 VDDQ_B3 DQ30__DQ6 VDDQ_B3 DQ30__DQ6 VDDQ_B3

DQC0_31 DQC1_13 DQD0_15 DQD1_21

N2 B12 N2 B12 N2 B12 N2 B12

DQC0_<2> 4 DQC1_<2> 4 DQD0_<2> 4 DQD1_<2> 4

28 14 12 23

DQC0_<3> DQC0_<30> DQC1_<3> DQC1_<15> DQD0_<3> DQD0_<14> DQD1_<3> DQD1_<22>

DQ29__DQ5 VDDQ_B12 DQ29__DQ5 VDDQ_B12 DQ29__DQ5 VDDQ_B12 DQ29__DQ5 VDDQ_B12

DQC0_28 DQC1_14 DQD0_12 DQD1_23

N4 B14 N4 B14 N4 B14 N4 B14

DQC0_<3> 4 DQC1_<3> 4 DQD0_<3> 4 DQD1_<3> 4

30 15 14 22

DQC0_<4> DQC0_<27> DQC1_<4> DQC1_<11> DQD0_<4> DQD0_<10> DQD1_<4> DQD1_<19>

DQ28__DQ4 VDDQ_B14 DQ28__DQ4 VDDQ_B14 DQ28__DQ4 VDDQ_B14 DQ28__DQ4 VDDQ_B14

DQC0_30 DQC1_15 DQD0_14 DQD1_22

0

T2 D1 T2 D1 T2 D1 T2 D1

DQC0_<4> 4 DQC1_<4> 4 DQD0_<4> 4 DQD1_<4> 4

27 11 10 19

DQC0_<5> DQC0_<24> DQC1_<5> DQC1_<10> DQD0_<5> DQD0_<8> DQD1_<5> DQD1_<18>

DQ27__DQ3 VDDQ_D1 DQ27__DQ3 VDDQ_D1 DQ27__DQ3 VDDQ_D1 DQ27__DQ3 VDDQ_D1

DQC0_27 DQC1_11 DQD0_10 DQD1_19

T4 D3 T4 D3 T4 D3 T4 D3

DQC0_<5> 4 DQC1_<5> 4 DQD0_<5> 4 DQD1_<5> 4

24 10 8 18

DQC0_<6> DQC0_<26> DQC1_<6> DQC1_<9> DQD0_<6> DQD0_<11> DQD1_<6> DQD1_<16>

DQ26__DQ2 VDDQ_D3 DQ26__DQ2 VDDQ_D3 DQ26__DQ2 VDDQ_D3 DQ26__DQ2 VDDQ_D3

RD 17 SI

DQC0_24 DQC1_10 DQD0_8 DQD1_18

V2 D12 V2 D12 V2 D12 V2 D12

DQC0_<6> 4 DQC1_<6> 4 DQD0_<6> 4 DQD1_<6> 4

26 9 11 16

DQC0_<7> DQC0_<25> DQC1_<7> DQC1_<8> DQD0_<7> DQD0_<9> DQD1_<7> DQD1_<17>

DQ25__DQ1 VDDQ_D12 DQ25__DQ1 VDDQ_D12 DQ25__DQ1 VDDQ_D12 DQ25__DQ1 VDDQ_D12

DQC0_26 DQC1_9 DQD0_11 DQD1_16

V4 D14 V4 D14 V4 D14 V4 D14

DQC0_<7> 4 DQC1_<7> 4 DQD0_<7> 4 DQD1_<7> 4

25 8 9 17

DQC0_<8> DQC0_<16> DQC1_<8> DQC1_<1> DQD0_<8> DQD0_<0> DQD1_<8> DQD1_<26>

DQ24__DQ0 VDDQ_D14 DQ24__DQ0 VDDQ_D14 DQ24__DQ0 VDDQ_D14 DQ24__DQ0 VDDQ_D14

DQC0_25 DQC1_8 DQD0_9 DQD1_17

M13 E5 M13 E5 M13 E5 M13 E5

DQC0_<8> 4 DQC1_<8> 4 DQD0_<8> 4 DQD1_<8> 4

16 1 0 26

DQC0_<9> DQC0_<23> DQC1_<9> DQC1_<2> DQD0_<9> DQD0_<7> DQD1_<9> DQD1_<25>

DQ23__DQ15 VDDQ_E5 DQ23__DQ15 VDDQ_E5 DQ23__DQ15 VDDQ_E5 DQ23__DQ15 VDDQ_E5

DQC0_16 DQC1_1 DQD0_0 DQD1_26

M11 E10 M11 E10 M11 E10 M11 E10

DQC0_<9> 4 DQC1_<9> 4 DQD0_<9> 4 DQD1_<9> 4

23 2 7 25

DQC0_<10> DQC0_<17> DQC1_<10> DQC1_<3> DQD0_<10> DQD0_<2> DQD1_<10> DQD1_<27>

DQ22__DQ14 VDDQ_E10 DQ22__DQ14 VDDQ_E10 DQ22__DQ14 VDDQ_E10 DQ22__DQ14 VDDQ_E10

DQC0_23 DQC1_2 DQD0_7 DQD1_25

N13 F1 N13 F1 N13 F1 N13 F1

DQC0_<10> 4 DQC1_<10> 4 DQD0_<10> 4 DQD1_<10> 4

17 3 2 27

DQC0_<11> DQC0_<21> DQC1_<11> DQC1_<0> DQD0_<11> DQD0_<6> DQD1_<11> DQD1_<24>

DQ21__DQ13 VDDQ_F1 DQ21__DQ13 VDDQ_F1 DQ21__DQ13 VDDQ_F1 DQ21__DQ13 VDDQ_F1

DQC0_17 DQC1_3 DQD0_2 DQD1_27

N11 F3 N11 F3 N11 F3 N11 F3

DQC0_<11> 4 DQC1_<11> 4 DQD0_<11> 4 DQD1_<11> 4

21 0 6 24

DQC0_<12> DQC0_<19> DQC1_<12> DQC1_<5> DQD0_<12> DQD0_<3> DQD1_<12> DQD1_<28>

DQ20__DQ12 VDDQ_F3 DQ20__DQ12 VDDQ_F3 DQ20__DQ12 VDDQ_F3 DQ20__DQ12 VDDQ_F3

DQC0_21 DQC1_0 DQD0_6 DQD1_24

T13 F12 T13 F12 T13 F12 T13 F12

DQC0_<12> 4 DQC1_<12> 4 DQD0_<12> 4 DQD1_<12> 4

19 5 3 28

DQC0_<13> DQC0_<22> DQC1_<13> DQC1_<4> DQD0_<13> DQD0_<5> DQD1_<13> DQD1_<29>

DQ19__DQ11 VDDQ_F12 DQ19__DQ11 VDDQ_F12 DQ19__DQ11 VDDQ_F12 DQ19__DQ11 VDDQ_F12

DQC0_19 DQC1_5 DQD0_3 DQD1_28

T11 F14 T11 F14 T11 F14 T11 F14

DQC0_<13> 4 DQC1_<13> 4 DQD0_<13> 4 DQD1_<13> 4

22 4 5 29

DQC0_<14> DQC0_<18> DQC1_<14> DQC1_<7> DQD0_<14> DQD0_<1> DQD1_<14> DQD1_<30>

DQ18__DQ10 VDDQ_F14 DQ18__DQ10 VDDQ_F14 DQ18__DQ10 VDDQ_F14 DQ18__DQ10 VDDQ_F14

DQC0_22 DQC1_4 DQD0_5 DQD1_29

V13 G2 V13 G2 V13 G2 V13 G2

DQC0_<14> 4 DQC1_<14> 4 DQD0_<14> 4 DQD1_<14> 4

(C 96 C

18 7 1 30

DQC0_<15> DQC0_<20> DQC1_<15> DQC1_<6> DQD0_<15> DQD0_<4> DQD1_<15> DQD1_<31>

DQ17__DQ9 VDDQ_G2 DQ17__DQ9 VDDQ_G2 DQ17__DQ9 VDDQ_G2 DQ17__DQ9 VDDQ_G2

DQC0_18 DQC1_7 DQD0_1 DQD1_30

V11 G13 V11 G13 V11 G13 V11 G13

DQC0_<15> 4 DQC1_<15> 4 DQD0_<15> 4 DQD1_<15> 4

20 6 4 31

DQC0_<16> DQC0_<5> DQC1_<16> DQC1_<31> DQD0_<16> DQD0_<20> DQD1_<16> DQD1_<14>

DQ16__DQ8 VDDQ_G13 DQ16__DQ8 VDDQ_G13 DQ16__DQ8 VDDQ_G13 DQ16__DQ8 VDDQ_G13

DQC0_20 DQC1_6 DQD0_4 DQD1_31

F13 H3 F13 H3 F13 H3 F13 H3

DQC0_<16> 4 DQC1_<16> 4 DQD0_<16> 4 DQD1_<16> 4

5 31 20 14

DQC0_<17> DQC0_<4> DQC1_<17> DQC1_<24> DQD0_<17> DQD0_<23> DQD1_<17> DQD1_<8>

DQ15__DQ23 VDDQ_H3 DQ15__DQ23 VDDQ_H3 DQ15__DQ23 VDDQ_H3 DQ15__DQ23 VDDQ_H3

DQC0_5 DQC1_31 DQD0_20 DQD1_14

F11 H12 F11 H12 F11 H12 F11 H12

DQC0_<17> 4 DQC1_<17> 4 DQD0_<17> 4 DQD1_<17> 4

4 24 23 8

DQC0_<18> DQC0_<7> DQC1_<18> DQC1_<30> DQD0_<18> DQD0_<21> DQD1_<18> DQD1_<15>

DQ14__DQ22 VDDQ_H12 DQ14__DQ22 VDDQ_H12 DQ14__DQ22 VDDQ_H12 DQ14__DQ22 VDDQ_H12

DQC0_4 DQC1_24 DQD0_23 DQD1_8

E13 K3 E13 K3 E13 K3 E13 K3

DQC0_<18> 4 DQC1_<18> 4 DQD0_<18> 4 DQD1_<18> 4

7 30 21 15

DQC0_<19> DQC0_<6> DQC1_<19> DQC1_<25> DQD0_<19> DQD0_<22> DQD1_<19> DQD1_<9>

DQ13__DQ21 VDDQ_K3 DQ13__DQ21 VDDQ_K3 DQ13__DQ21 VDDQ_K3 DQ13__DQ21 VDDQ_K3

DQC0_7 DQC1_30 DQD0_21 DQD1_15

E11 K12 E11 K12 E11 K12 E11 K12

DQC0_<19> 4 DQC1_<19> 4 DQD0_<19> 4 DQD1_<19> 4

6 25 22 9

DQC0_<20> DQC0_<3> DQC1_<20> DQC1_<28> DQD0_<20> DQD0_<19> DQD1_<20> DQD1_<13>

DQ12__DQ20 VDDQ_K12 DQ12__DQ20 VDDQ_K12 DQ12__DQ20 VDDQ_K12 DQ12__DQ20 VDDQ_K12

DQC0_6 DQC1_25 DQD0_22 DQD1_9

B13 L2 B13 L2 B13 L2 B13 L2

DQC0_<20> 4 DQC1_<20> 4 DQD0_<20> 4 DQD1_<20> 4

3 28 19 13

DQC0_<21> DQC0_<1> DQC1_<21> DQC1_<26> DQD0_<21> DQD0_<18> DQD1_<21> DQD1_<10>

DQ11__DQ19 VDDQ_L2 DQ11__DQ19 VDDQ_L2 DQ11__DQ19 VDDQ_L2 DQ11__DQ19 VDDQ_L2

DQC0_3 DQC1_28 DQD0_19 DQD1_13

B11 L13 B11 L13 B11 L13 B11 L13

DQC0_<21> 4 DQC1_<21> 4 DQD0_<21> 4 DQD1_<21> 4

1 26 18 10

DQC0_<22> DQC0_<0> DQC1_<22> DQC1_<29> DQD0_<22> DQD0_<17> DQD1_<22> DQD1_<12>

DQ10__DQ18 VDDQ_L13 DQ10__DQ18 VDDQ_L13 DQ10__DQ18 VDDQ_L13 DQ10__DQ18 VDDQ_L13

DQC0_1 DQC1_26 DQD0_18 DQD1_10

)2 7 ON

A13 M1 A13 M1 A13 M1 A13 M1

DQC0_<22> 4 DQC1_<22> 4 DQD0_<22> 4 DQD1_<22> 4

0 29 17 12

DQC0_<23> DQC0_<2> DQC1_<23> DQC1_<27> DQD0_<23> DQD0_<16> DQD1_<23> DQD1_<11>

DQ9__DQ17 VDDQ_M1 DQ9__DQ17 VDDQ_M1 DQ9__DQ17 VDDQ_M1 DQ9__DQ17 VDDQ_M1

DQC0_0 DQC1_29 DQD0_17 DQD1_12

A11 M3 A11 M3 A11 M3 A11 M3

DQC0_<23> 4 DQC1_<23> 4 DQD0_<23> 4 DQD1_<23> 4

2 27 16 11

DQC0_<24> DQC0_<10> DQC1_<24> DQC1_<18> DQD0_<24> DQD0_<26> DQD1_<24> DQD1_<3>

DQ8__DQ16 VDDQ_M3 DQ8__DQ16 VDDQ_M3 DQ8__DQ16 VDDQ_M3 DQ8__DQ16 VDDQ_M3

DQC0_2 DQC1_27 DQD0_16 DQD1_11

F2 M12 F2 M12 F2 M12 F2 M12

DQC0_<24> 4 DQC1_<24> 4 DQD0_<24> 4 DQD1_<24> 4

10 18 26 3

DQC0_<25> DQC0_<9> DQC1_<25> DQC1_<16> DQD0_<25> DQD0_<25> DQD1_<25> DQD1_<0>

DQ7__DQ31 VDDQ_M12 DQ7__DQ31 VDDQ_M12 DQ7__DQ31 VDDQ_M12 DQ7__DQ31 VDDQ_M12

DQC0_10 DQC1_18 DQD0_26 DQD1_3

F4 M14 F4 M14 F4 M14 F4 M14

DQC0_<25> 4 DQC1_<25> 4 DQD0_<25> 4 DQD1_<25> 4

9 16 25 0

DQC0_<26> DQC0_<11> DQC1_<26> DQC1_<19> DQD0_<26> DQD0_<27> DQD1_<26> DQD1_<2>

DQ6__DQ30 VDDQ_M14 DQ6__DQ30 VDDQ_M14 DQ6__DQ30 VDDQ_M14 DQ6__DQ30 VDDQ_M14

DQC0_9 DQC1_16 DQD0_25 DQD1_0

E2 N5 E2 N5 E2 N5 E2 N5

DQC0_<26> 4 DQC1_<26> 4 DQD0_<26> 4 DQD1_<26> 4

11 19 27 2

DQC0_<27> DQC0_<8> DQC1_<27> DQC1_<17> DQD0_<27> DQD0_<24> DQD1_<27> DQD1_<1>

DQ5__DQ29 VDDQ_N5 DQ5__DQ29 VDDQ_N5 DQ5__DQ29 VDDQ_N5 DQ5__DQ29 VDDQ_N5

DQC0_11 DQC1_19 DQD0_27 DQD1_2

E4 N10 E4 N10 E4 N10 E4 N10

DQC0_<27> 4 DQC1_<27> 4 DQD0_<27> 4 DQD1_<27> 4

8 17 24 1

DQC0_<28> DQC0_<12> DQC1_<28> DQC1_<20> DQD0_<28> DQD0_<28> DQD1_<28> DQD1_<4>

DQ4__DQ28 VDDQ_N10 DQ4__DQ28 VDDQ_N10 DQ4__DQ28 VDDQ_N10 DQ4__DQ28 VDDQ_N10

DQC0_8 DQC1_17 DQD0_24 DQD1_1

B2 P1 B2 P1 B2 P1 B2 P1

DQC0_<28> 4 DQC1_<28> 4 DQD0_<28> 4 DQD1_<28> 4

12 20 28 4

DQC0_<29> DQC0_<13> DQC1_<29> DQC1_<22> DQD0_<29> DQD0_<29> DQD1_<29> DQD1_<5>

DQ3__DQ27 VDDQ_P1 DQ3__DQ27 VDDQ_P1 DQ3__DQ27 VDDQ_P1 DQ3__DQ27 VDDQ_P1

DQC0_12 DQC1_20 DQD0_28 DQD1_4

B4 P3 B4 P3 B4 P3 B4 P3

DQC0_<29> 4 DQC1_<29> 4 DQD0_<29> 4 DQD1_<29> 4

13 22 29 5

DQC0_<30> DQC0_<14> DQC1_<30> DQC1_<21> DQD0_<30> DQD0_<30> DQD1_<30> DQD1_<7>

DQ2__DQ26 VDDQ_P3 DQ2__DQ26 VDDQ_P3 DQ2__DQ26 VDDQ_P3 DQ2__DQ26 VDDQ_P3

DQC0_13 DQC1_22 DQD0_29 DQD1_5

A2 P12 A2 P12 A2 P12 A2 P12

F

DQC0_<30> 4 DQC1_<30> 4 DQD0_<30> 4 DQD1_<30> 4

14 21 30 7

DQC0_<31> DQC0_<15> DQC1_<31> DQC1_<23> DQD0_<31> DQD0_<31> DQD1_<31> DQD1_<6>

DQ1__DQ25 VDDQ_P12 DQ1__DQ25 VDDQ_P12 DQ1__DQ25 VDDQ_P12 DQ1__DQ25 VDDQ_P12

DQC0_14 DQC1_21 DQD0_30 DQD1_7

0

A4 P14 A4 P14 A4 P14 A4 P14

DQC0_<31> 4 DQC1_<31> 4 DQD0_<31> 4 DQD1_<31> 4

15 23 31 6

DQ0__DQ24 VDDQ_P14 DQ0__DQ24 VDDQ_P14 DQ0__DQ24 VDDQ_P14 DQ0__DQ24 VDDQ_P14

DQC0_15 DQC1_23 DQD0_31 DQD1_6

VDDQ_T1 T1 VDDQ_T1 T1 VDDQ_T1 T1 VDDQ_T1 T1

VDDQ_T3 T3 VDDQ_T3 T3 VDDQ_T3 T3 VDDQ_T3 T3

T12 T12 T12 T12

石 17 jo ID

VDDQ_T12 VDDQ_T12 VDDQ_T12 VDDQ_T12

VDDQ_T14 T14 VDDQ_T14 T14 VDDQ_T14 T14 VDDQ_T14 T14

+MVDD +MVDD +MVDD +MVDD

MAC0_<0> MAC0_<8> J5 MAC1_<0> MAC1_<8> J5 MAD0_<0> 8

MAD0_<8> J5 MAD1_<0> 8

MAD1_<8> J5

MAC0_<0> MAC0_<1> 48 MAC0_<7>

RFU_A12_NC

MAC1_<0> MAC1_<1>

8

4 MAC1_<0>

RFU_A12_NC

MAD0_<0> MAD0_<1> 4 MAD0_<7>

RFU_A12_NC

MAD1_<0> MAD1_<1> 4 MAD1_<0>

RFU_A12_NC

K4 C5 K4 C5 K4 C5 K4 C5

7 0

MAC0_<1> MAC0_<2> 47 MAC0_<6>

A7_A8__A0_A10 VDD_C5

MAC1_<1> MAC1_<2>

0

4 MAC1_<1>

A7_A8__A0_A10 VDD_C5

MAD0_<1> MAD0_<2> 4 MAD0_<6>

A7_A8__A0_A10 VDD_C5

MAD1_<1> MAD1_<2> 4 MAD1_<1>

A7_A8__A0_A10 VDD_C5

K5 C10 K5 C10 K5 C10 K5 C10

6 1

MAC0_<2> MAC0_<3> 46 MAC0_<5>

A6_A11__A1_A9 VDD_C10

MAC1_<2> MAC1_<3>

1

4 MAC1_<3>

A6_A11__A1_A9 VDD_C10

MAD0_<2> MAD0_<3> 4 MAD0_<5>

A6_A11__A1_A9 VDD_C10

MAD1_<2> MAD1_<3> 4 MAD1_<3>

A6_A11__A1_A9 VDD_C10

K10 D11 K10 D11 K10 D11 K10 D11

5 3

MAC0_<3> MAC0_<4> 45 MAC0_<4>

A5_BA1__A3_BA3 VDD_D11

MAC1_<3> MAC1_<4>

3

4 MAC1_<2>

A5_BA1__A3_BA3 VDD_D11

MAD0_<3> MAD0_<4> 4 MAD0_<4>

A5_BA1__A3_BA3 VDD_D11

MAD1_<3> MAD1_<4> 4 MAD1_<2>

A5_BA1__A3_BA3 VDD_D11

K11 G1 K11 G1 K11 G1 K11 G1

4 2

MAC0_<4> MAC0_<5> 44 MAC0_<3>

A4_BA2__A2_BA0 VDD_G1

MAC1_<4> MAC1_<5>

2

4 MAC1_<5>

A4_BA2__A2_BA0 VDD_G1

MAD0_<4> MAD0_<5> 4 MAD0_<3>

A4_BA2__A2_BA0 VDD_G1

MAD1_<4> MAD1_<5> 4 MAD1_<5>

A4_BA2__A2_BA0 VDD_G1

H10 G4 H10 G4 H10 G4 H10 G4

3 5

MAC0_<5> MAC0_<6> 43 MAC0_<2> MAC1_<5> MAC1_<6> 4 MAC1_<4> MAD0_<5> MAD0_<6> 4 MAD0_<2> MAD1_<5> MAD1_<6> 4 MAD1_<4>

阿 09 ne EN

A3_BA3__A5_BA1 VDD_G4 5 A3_BA3__A5_BA1 VDD_G4 A3_BA3__A5_BA1 VDD_G4 A3_BA3__A5_BA1 VDD_G4

H11 G11 H11 G11 H11 G11 H11 G11

2 4

MAC0_<6> MAC0_<7> 42 MAC0_<1>

A2_BA0__A4_BA2 VDD_G11

MAC1_<6> MAC1_<7>

4

4 MAC1_<6>

A2_BA0__A4_BA2 VDD_G11

MAD0_<6> MAD0_<7> 4 MAD0_<1>

A2_BA0__A4_BA2 VDD_G11

MAD1_<6> MAD1_<7> 4 MAD1_<6>

A2_BA0__A4_BA2 VDD_G11

H5 G14 H5 G14 H5 G14 H5 G14

1 6

MAC0_<7> MAC0_<8> 41 MAC0_<0>

A1_A9__A6_A11 VDD_G14

MAC1_<7> MAC1_<8>

6

4 MAC1_<7>

A1_A9__A6_A11 VDD_G14

MAD0_<7> MAD0_<8> 4 MAD0_<0>

A1_A9__A6_A11 VDD_G14

MAD1_<7> MAD1_<8> 4 MAD1_<7>

A1_A9__A6_A11 VDD_G14

H4 L1 H4 L1 H4 L1 H4 L1

0 7

MAC0_<8> 40 A0_A10__A7_A8 VDD_L1

MAC1_<8>

7

4 A0_A10__A7_A8 VDD_L1

MAD0_<8> 4 A0_A10__A7_A8 VDD_L1

MAD1_<8> 4 A0_A10__A7_A8 VDD_L1

VDD_L4 L4 VDD_L4 L4 VDD_L4 L4 VDD_L4 L4

VDD_L11 L11 VDD_L11 L11 VDD_L11 L11 VDD_L11 L11

VDD_L14 L14 VDD_L14 L14 VDD_L14 L14 VDD_L14 L14

D4 P11 D4 P11 D4 P11 D4 P11

IN IN IN IN

WCKC0_0 WCKC1_1 WCKD0_1 WCKD1_0

4 WCK01__WCK23 VDD_P11 4 WCK01__WCK23 VDD_P11 4 WCK01__WCK23 VDD_P11 4 WCK01__WCK23 VDD_P11

D5 R5 D5 R5 D5 R5 D5 R5

IN IN IN IN

WCKC0B_0 WCKC1B_1 WCKD0B_1 WCKD1B_0

4 WCK01#__WCK23# VDD_R5 4 WCK01#__WCK23# VDD_R5 4 WCK01#__WCK23# VDD_R5 4 WCK01#__WCK23# VDD_R5

鋒 19 pe TI

VDD_R10 R10 VDD_R10 R10 VDD_R10 R10 VDD_R10 R10

P4 P4 P4 P4

IN IN IN IN

WCKC0_1 WCKC1_0 WCKD0_0 WCKD1_1

4 WCK23__WCK01 4 WCK23__WCK01 4 WCK23__WCK01 4 WCK23__WCK01

P5 P5 P5 P5

IN IN IN IN

WCKC0B_1 WCKC1B_0 WCKD0B_0 WCKD1B_1

4 WCK23#__WCK01# 4 WCK23#__WCK01# 4 WCK23#__WCK01# 4 WCK23#__WCK01#

VSSQ_A1 A1 VSSQ_A1 A1 VSSQ_A1 A1 VSSQ_A1 A1

R2 A3 R2 A3 R2 A3 R2 A3

OUT OUT OUT OUT

EDCC0_3 EDCC1_1 EDCD0_1 EDCD1_2

4 EDC3__EDC0 VSSQ_A3 4 EDC3__EDC0 VSSQ_A3 4 EDC3__EDC0 VSSQ_A3 4 EDC3__EDC0 VSSQ_A3

R13 A12 R13 A12 R13 A12 R13 A12

OUT OUT OUT OUT

EDCC0_2 EDCC1_0 EDCD0_0 EDCD1_3

4 EDC2__EDC1 VSSQ_A12 4 EDC2__EDC1 VSSQ_A12 4 EDC2__EDC1 VSSQ_A12 4 EDC2__EDC1 VSSQ_A12

C13 A14 C13 A14 C13 A14 C13 A14

OUT OUT OUT OUT

EDCC0_0 EDCC1_3 EDCD0_2 EDCD1_1

4 EDC1__EDC2 VSSQ_A14 4 EDC1__EDC2 VSSQ_A14 4 EDC1__EDC2 VSSQ_A14 4 EDC1__EDC2 VSSQ_A14

C2 C1 C2 C1 C2 C1 C2 C1

OUT OUT OUT OUT

EDCC0_1 EDCC1_2 EDCD0_3 EDCD1_0

4 EDC0__EDC3 VSSQ_C1 4 EDC0__EDC3 VSSQ_C1 4 EDC0__EDC3 VSSQ_C1 4 EDC0__EDC3 VSSQ_C1

02 i( AL

VSSQ_C3 C3 VSSQ_C3 C3 VSSQ_C3 C3 VSSQ_C3 C3

DDBIC0_3 P2 C4 DDBIC1_1 P2 C4 DDBID0_1 P2 C4 DDBID1_2 P2 C4

BI 4 DBI3#__DBI0# VSSQ_C4 BI 4 DBI3#__DBI0# VSSQ_C4 BI 4 DBI3#__DBI0# VSSQ_C4 BI 4 DBI3#__DBI0# VSSQ_C4

DDBIC0_2 P13 C11 DDBIC1_0 P13 C11 DDBID0_0 P13 C11 DDBID1_3 P13 C11

BI 4 DBI2#__DBI1# VSSQ_C11 BI 4 DBI2#__DBI1# VSSQ_C11 BI 4 DBI2#__DBI1# VSSQ_C11 BI 4 DBI2#__DBI1# VSSQ_C11

DDBIC0_0 D13 C12 DDBIC1_3 D13 C12 DDBID0_2 D13 C12 DDBID1_1 D13 C12

BI 4 DBI1#__DBI2# VSSQ_C12 BI 4 DBI1#__DBI2# VSSQ_C12 BI 4 DBI1#__DBI2# VSSQ_C12 BI 4 DBI1#__DBI2# VSSQ_C12

DDBIC0_1 D2 C14 DDBIC1_2 D2 C14 DDBID0_3 D2 C14 DDBID1_0 D2 C14

BI 4 DBI0#__DBI3# VSSQ_C14 BI 4 DBI0#__DBI3# VSSQ_C14 BI 4 DBI0#__DBI3# VSSQ_C14 BI 4 DBI0#__DBI3# VSSQ_C14

VSSQ_E1 E1 VSSQ_E1 E1 VSSQ_E1 E1 VSSQ_E1 E1

VSSQ_E3 E3 VSSQ_E3 E3 VSSQ_E3 E3 VSSQ_E3 E3

VSSQ_E12 E12 VSSQ_E12 E12 VSSQ_E12 E12 VSSQ_E12 E12

+MVDD G3 E14 +MVDD G3 E14 +MVDD G3 E14 +MVDD G3 E14

IN IN IN IN

RASC0B CASC1B RASD0B CASD1B

4 RAS#__CAS# VSSQ_E14 4 RAS#__CAS# VSSQ_E14 4 RAS#__CAS# VSSQ_E14 4 RAS#__CAS# VSSQ_E14

(0

L3 F5 L3 F5 L3 F5 L3 F5

IN IN IN IN

CASC0B RASC1B CASD0B RASD1B

4 CAS#__RAS# VSSQ_F5 4 CAS#__RAS# VSSQ_F5 4 CAS#__RAS# VSSQ_F5 4 CAS#__RAS# VSSQ_F5

2

R2401 1 60.4R 1% F10 2

R2501 1 60.4R 1% F10 2

R2601 1 60.4R 1% F10 2

R2701 1 60.4R 1% F10

裴

VSSQ_F10 VSSQ_F10 VSSQ_F10 VSSQ_F10

2

R2400 1 60.4R 1% VSSQ_H2 H2 2

R2500 1 60.4R 1% VSSQ_H2 H2 2

R2600 1 60.4R 1% VSSQ_H2 H2 2

R2700 1 60.4R 1% VSSQ_H2 H2

J3 H13 J3 H13 J3 H13 J3 H13

IN IN IN IN

CKEC0 CKEC1 CKED0 CKED1

4 CKE# VSSQ_H13 4 CKE# VSSQ_H13 4 CKE# VSSQ_H13 4 CKE# VSSQ_H13

J11 K2 J11 K2 J11 K2 J11 K2

IN IN IN IN

CLKC0B CLKC1B CLKD0B CLKD1B

4 CK# VSSQ_K2 4 CK# VSSQ_K2 4 CK# VSSQ_K2 4 CK# VSSQ_K2

J12 K13 J12 K13 J12 K13 J12 K13

IN IN IN IN

CLKC0 CLKC1 CLKD0 CLKD1

4 CK VSSQ_K13 4 CK VSSQ_K13 4 CK VSSQ_K13 4 CK VSSQ_K13

VSSQ_M5 M5 VSSQ_M5 M5 VSSQ_M5 M5 VSSQ_M5 M5

VSSQ_M10 M10 VSSQ_M10 M10 VSSQ_M10 M10 VSSQ_M10 M10

00 RM 亮

G12 N1 G12 N1 G12 N1 G12 N1

IN IN IN IN

CSC0B_0 WEC1B CSD0B_0 WED1B

4 CS#__WE# VSSQ_N1 4 CS#__WE# VSSQ_N1 4 CS#__WE# VSSQ_N1 4 CS#__WE# VSSQ_N1

L12 N3 L12 N3 L12 N3 L12 N3

IN IN IN IN

WEC0B CSC1B_0 WED0B CSD1B_0

4 WE#__CS# VSSQ_N3 4 WE#__CS# VSSQ_N3 4 WE#__CS# VSSQ_N3 4 WE#__CS# VSSQ_N3

VSSQ_N12 N12 VSSQ_N12 N12 VSSQ_N12 N12 VSSQ_N12 N12

VSSQ_N14 N14 VSSQ_N14 N14 VSSQ_N14 N14 VSSQ_N14 N14

ZQ_C0 ZQ_C1 ZQ_D0 ZQ_D1

2

R2402 1 120R 1% J13 ZQ VSSQ_R1 R1 2

R2502 1 120R 1% J13 ZQ VSSQ_R1 R1 2

R2602 1 120R 1% J13 ZQ VSSQ_R1 R1 2

R2702 1 120R 1% J13 ZQ VSSQ_R1 R1

SEN_C0 SEN_C1 SEN_D0 SEN_D1

R24031 2

1K 5% J10 SEN VSSQ_R3 R3 R25031 2

1K 5% J10 SEN VSSQ_R3 R3 R26031 2

1K 5% J10 SEN VSSQ_R3 R3 R27031 2

1K 5% J10 SEN VSSQ_R3 R3