Professional Documents

Culture Documents

Chapter 8 MS

Uploaded by

Rakesh KumarOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Chapter 8 MS

Uploaded by

Rakesh KumarCopyright:

Available Formats

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital to Analog

Digital to Analog

Conversion

Conversion

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Sampling and Quantization

Sampling and Quantization

Pages 390

Pages 390

-

-

391

391

EE4512 Analog and Digital Communications Chapter 8

Traditional

Traditional

analog transmission

analog transmission

(AM, FM and PM) are less

(AM, FM and PM) are less

complex than digital data transmission have been the basis

complex than digital data transmission have been the basis

of broadcasting and communication for 100 years.

of broadcasting and communication for 100 years.

Analog television signal Analog television spectrum

S&M Figure 8

S&M Figure 8

-

-

1a

1a

EE4512 Analog and Digital Communications Chapter 8

Digital data transmission

Digital data transmission

(PAM, ASK, PSK, FSK and QAM)

(PAM, ASK, PSK, FSK and QAM)

is more complex but (perhaps) offers higher performance

is more complex but (perhaps) offers higher performance

with control of accuracy and easier storage, simpler signal

with control of accuracy and easier storage, simpler signal

processing for noise reduction, error detection and

processing for noise reduction, error detection and

correction and encryption.

correction and encryption.

S&M Figure 8

S&M Figure 8

-

-

1b

1b

EE4512 Analog and Digital Communications Chapter 8

Digital data transmission requires analog

Digital data transmission requires analog

-

-

to

to

-

-

digital (ADC)

digital (ADC)

and digital

and digital

-

-

to

to

-

-

analog (DAC) converters. The ADC process

analog (DAC) converters. The ADC process

utilizes sampling and quantization of the continuous analog

utilizes sampling and quantization of the continuous analog

signal.

signal.

ADC

ADC

DAC

DAC

S&M Figure 8

S&M Figure 8

-

-

1b

1b

EE4512 Analog and Digital Communications Chapter 8

ADC sampling occurs at a uniform rate (the

ADC sampling occurs at a uniform rate (the

sampling rate

sampling rate

)

)

and has a continuous amplitude.

and has a continuous amplitude.

Continuous

amplitude

Uniform

sampling

rate

Analog signal

S&M Figure 8

S&M Figure 8

-

-

2a,b

2a,b

EE4512 Analog and Digital Communications Chapter 8

The continuous amplitude sample is then quantized to

The continuous amplitude sample is then quantized to

n

n

bits or resolution for the

bits or resolution for the

full scale

full scale

input or

input or

2

2

n n

levels

levels

.

.

Continuous

amplitude

Uniform

sampling

rate

Quantized

S&M Figure 8 S&M Figure 8- -2b,c 2b,c

Quantized

amplitude

EE4512 Analog and Digital Communications Chapter 8

Here n =

Here n =

4 and there are 2

4 and there are 2

4 4

= 16

= 16

levels for a full scale input

levels for a full scale input

of 2 V (

of 2 V (

1 V). The

1 V). The

step size

step size

= 2 V / 16 = 0.125 V and the

= 2 V / 16 = 0.125 V and the

quantized value

quantized value

is the

is the

midpoint

midpoint

of the

of the

voltage

voltage

range

range

.

.

S&M Table 8.1

S&M Table 8.1

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Sampling Baseband

Sampling Baseband

Analog Signals

Analog Signals

Pages 392

Pages 392

-

-

399

399

EE4512 Analog and Digital Communications Chapter 8

The analog signal

The analog signal

x(t

x(t

) which is continuously, uniformly

) which is continuously, uniformly

sampled is represented by:

sampled is represented by:

Multiplication in the temporal domain is convolution in the

Multiplication in the temporal domain is convolution in the

frequency domain and the frequency domain representation

frequency domain and the frequency domain representation

is:

is:

=

s

k =

x (t) x(t) (t k )

S

T

S&M Eq. 8.1

S&M Eq. 8.1

=

`

)

=

`

)

=

s

k =

s

k =

s

k =

X (f) X(f) (t k )

X (f) X(f) (f k )

X (f) X(f k )

S

S S

S S

T

f f

f f

F

S&M Eq. 8.2

S&M Eq. 8.2

EE4512 Analog and Digital Communications Chapter 8

Temporal and spectral representation of the continuous

Temporal and spectral representation of the continuous

sampling process for a sum of three sinusoids.

sampling process for a sum of three sinusoids.

k =

(t k )

S

T

=

s

k =

x (t) x(t) (t k )

S

T

=

s

k =

X (f) X(f k )

S S

f f

k =

(f k )

S

f

S&M Figure 8

S&M Figure 8

-

-

3

3

EE4512 Analog and Digital Communications Chapter 8

2 V, 20

2 V, 20

initial

initial

phase,

phase,

500 Hz

500 Hz

sinusoid

sinusoid

sampled at

sampled at

5 k samples/sec

5 k samples/sec

S&M Figure 8

S&M Figure 8

-

-

4a,b

4a,b

EE4512 Analog and Digital Communications Chapter 8

Aliased samples

Aliased samples

can be

can be

reconstructed

reconstructed

for a 4500 Hz

for a 4500 Hz

and a 5500 Hz

and a 5500 Hz

sinusoid that

sinusoid that

appears to be

appears to be

a 500 Hz

a 500 Hz

sinusoid

sinusoid

S&M

S&M

Figure 8

Figure 8

-

-

4a,c,d

4a,c,d

EE4512 Analog and Digital Communications Chapter 8

The

The

aliasing

aliasing

of

of

the signal can

the signal can

be predicted by

be predicted by

the magnitude

the magnitude

spectrum of the

spectrum of the

original 500 Hz

original 500 Hz

sampled signal.

sampled signal.

If the 4500 Hz

If the 4500 Hz

and 5500 Hz

and 5500 Hz

signals are then

signals are then

sampled at

sampled at

5 k samples/sec

5 k samples/sec

aliasing at occurs at | 4500

aliasing at occurs at | 4500

5000 | and (5500

5000 | and (5500

5000) Hz

5000) Hz

S&M Figure 8

S&M Figure 8

-

-

4a,b

4a,b

EE4512 Analog and Digital Communications Chapter 8

The sum of

The sum of

three sinusoids

three sinusoids

does not have

does not have

any aliased

any aliased

frequencies

frequencies

since the

since the

sampling

sampling

frequency

frequency

f

f

S S

is greater than

is greater than

twice the

twice the

highest

highest

frequency

frequency

f

f

max max

f

f

S S

> 2

> 2

f

f

max max

S&M Figure 8

S&M Figure 8

-

-

4a,c

4a,c

S&M Figure 8

S&M Figure 8

-

-

5

5

EE4512 Analog and Digital Communications Chapter 8

The frequency

The frequency

2

2

f

f

max max

is called

is called

the

the

Nyquist

Nyquist

frequency

frequency

.

.

Harry Nyquist,

Harry Nyquist,

who contributed

who contributed

to the understanding of thermal noise

to the understanding of thermal noise

while at Bell Labs, is also remembered

while at Bell Labs, is also remembered

in electrotechnology for his analysis of

in electrotechnology for his analysis of

sampled data signals.

sampled data signals.

S&M Figure 8

S&M Figure 8

-

-

4a

4a

Harry Nyquist

Harry Nyquist

1889

1889

-

-

1976

1976

EE4512 Analog and Digital Communications Chapter 8

The analog signal is

The analog signal is

reconstructed

reconstructed

from the quantized

from the quantized

samples by a DAC and a low pass filter (LFP).

samples by a DAC and a low pass filter (LFP).

S&M Figure 8

S&M Figure 8

-

-

6

6

EE4512 Analog and Digital Communications Chapter 8

For

For

practical signals

practical signals

f

f

S S

> 2

> 2

f

f

max max

using a

using a

guard band

guard band

for

for

LPFs

LPFs

S&M Figure 8

S&M Figure 8

-

-

7

7

f

f

S S

= 2

= 2

f

f

max max

f

f

S S

> 2

> 2

f

f

max max

guard band

guard band

EE4512 Analog and Digital Communications Chapter 8

With

With

out

out

-

-

of

of

-

-

band noise

band noise

and sample signals, aliases of the

and sample signals, aliases of the

noise now appear

noise now appear

in

in

-

-

band

band

and should be filtered before the

and should be filtered before the

sampling process.

sampling process.

S&M Figure 8

S&M Figure 8

-

-

8

8

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Sampling Baseband

Sampling Baseband

Analog Signals

Analog Signals

Pages 149

Pages 149

-

-

182

182

EE4512 Analog and Digital Communications Chapter 8

The periodic baseband

The periodic baseband

signal consisting of

signal consisting of

three sinusoids is

three sinusoids is

impulse sampled

impulse sampled

,

,

sampled

sampled

-

-

and

and

-

-

held

held

,

,

processed by an

processed by an

8

8

-

-

bit ADC

bit ADC

-

-

DAC

DAC

and a

and a

quantizer

quantizer

in

in

Simulink

Simulink

.

.

MS Figure 4.1

MS Figure 4.1

EE4512 Analog and Digital Communications Chapter 8

The periodic baseband signal is the sum of a 1 V 500 Hz, a

The periodic baseband signal is the sum of a 1 V 500 Hz, a

0.5 V 1.5 kHz and a 0.2 V 2.5 kHz sinusoid.

0.5 V 1.5 kHz and a 0.2 V 2.5 kHz sinusoid.

MS Figure 4.2

MS Figure 4.2

EE4512 Analog and Digital Communications Chapter 8

The power spectral density (PSD) of the periodic baseband

The power spectral density (PSD) of the periodic baseband

signal has the expected peaks at 0.5, 1.5 and 2.5 kHz.

signal has the expected peaks at 0.5, 1.5 and 2.5 kHz.

MS Figure 4.3

MS Figure 4.3 Three sinusoids

Three sinusoids

EE4512 Analog and Digital Communications Chapter 8

The periodic baseband signal is overlaid with the continuous

The periodic baseband signal is overlaid with the continuous

amplitude sample

amplitude sample

-

-

and

and

-

-

hold signal with

hold signal with

f

f

S S

= 8 kHz.

= 8 kHz.

MS Figure 4.4

MS Figure 4.4

0.125 msec

0.125 msec

EE4512 Analog and Digital Communications Chapter 8

The analog signal

The analog signal

x(t

x(t

) here is sampled and held rather than

) here is sampled and held rather than

impulse sampled:

impulse sampled:

The power spectral density (PSD

The power spectral density (PSD

s s- -h h

) of the sample and hold

) of the sample and hold

operation is:

operation is:

= =

=

s-h

n

y (t) x(n ) h(t n ) h(t) 1 0 t

h(t) 0

S S S

T T T

otherwise

MS Eq. 4.3

MS Eq. 4.3

( )

( )

=

=

2 2 2 2

s-h S

k =

2 2

s-h

k =

PSD | X(f k ) | T sinc 2 f

PSD | X(f k ) | sinc 2 f

S S S

S S

f f T

f T

MS Eq. 4.4

MS Eq. 4.4

EE4512 Analog and Digital Communications Chapter 8

However, if the analog signal

However, if the analog signal

x(t

x(t

) is impulse sampled:

) is impulse sampled:

Then the power spectral density (PSD) does not have a

Then the power spectral density (PSD) does not have a

sinc

sinc

2 2

term:

term:

The PSD

The PSD

s s- -h h

does have the sinc

does have the sinc

2 2

term:

term:

MS Eq. 4.1

MS Eq. 4.1

( )

=

=

2 2

k =

2 2

s-h

k =

PSD | X(f k ) |

PSD | X(f k ) | sinc 2 f

S S

S S

f f

f T

MS Eq. 4.4

MS Eq. 4.4

=

n

x(n ) x(t) (t n )

S S

T T

MS Eq. 4.2

MS Eq. 4.2

EE4512 Analog and Digital Communications Chapter 8

The PSD of the impulse sampled sum of three sinusoid

The PSD of the impulse sampled sum of three sinusoid

signal with

signal with

f

f

S S

= 8 kHz is:

= 8 kHz is:

MS Figure 4.5

MS Figure 4.5 8 kHz

8 kHz

16 kHz

16 kHz

No sinc

No sinc

2 2

term

term

2 2

k =

PSD | X(f k ) |

S S

f f

MS Eq. 4.2

MS Eq. 4.2

EE4512 Analog and Digital Communications Chapter 8

The PSD of the continuous amplitude sample and hold

The PSD of the continuous amplitude sample and hold

sum of three sinusoid signal with

sum of three sinusoid signal with

f

f

S S

= 8 kHz is:

= 8 kHz is:

MS Figure 4.6

MS Figure 4.6

8 kHz

8 kHz

16 kHz

16 kHz

sinc

sinc

2 2

term

term

( )

( )

=

=

2 2 2 2

s-h

k =

2 2

s-h

k =

PSD | X(f k ) | sinc 2 f

PSD | X(f k ) | sinc 2 f

S S S S

S S

f f T T

f T

MS Eq. 4.4

MS Eq. 4.4

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Sampling Bandpass

Sampling Bandpass

Analog Signals

Analog Signals

Pages 399

Pages 399

-

-

400

400

EE4512 Analog and Digital Communications Chapter 8

A bandpass signal does not need to be sampled at 2

A bandpass signal does not need to be sampled at 2

f

f

2 2

.

.

Nyquist

Nyquist

s bandpass sampling theory states that the

s bandpass sampling theory states that the

sampling rate

sampling rate

f

f

S S

> 2(

> 2(

f

f

2 2

f

f

1 1

) which is substantially less than

) which is substantially less than

2

2

f

f

2 2

S&M Figure 8

S&M Figure 8

-

-

9

9

f f

1 1

f f

2 2

f f

S S

= 20 ksamples/sec = 20 ksamples/sec

f f

S S

= 7 ksamples/sec = 7 ksamples/sec

LPF 10 kHz LPF 10 kHz

BPF 8 BPF 8- -10 kHz 10 kHz

8 10 kHz 8 10 kHz

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Sampling Bandpass

Sampling Bandpass

Analog Signals

Analog Signals

Pages 180

Pages 180

-

-

181

181

EE4512 Analog and Digital Communications Chapter 8

The

The

Simulink

Simulink

simulation uses the DSB AM modulation

simulation uses the DSB AM modulation

block and the sum of three sinusoids source.

block and the sum of three sinusoids source.

MS Figure 4

MS Figure 4

-

-

32

32

MS Figure 4

MS Figure 4

-

-

33

33

EE4512 Analog and Digital Communications Chapter 8

The

The

Simulink

Simulink

simulation initially uses a sampling rate of

simulation initially uses a sampling rate of

5 MHz and results in 4 194 304 = 2

5 MHz and results in 4 194 304 = 2

22 22

sampling points. The

sampling points. The

PSD shows the DSB

PSD shows the DSB

-

-

LC AM signal with the LSB and USB.

LC AM signal with the LSB and USB.

MS Figure 4

MS Figure 4

-

-

33

33

LSB USB

LSB USB

f

f

C C

Scaled PSD

Scaled PSD

f

f

max max

= 50 kHz

= 50 kHz

EE4512 Analog and Digital Communications Chapter 8

The bandwidth of the bandpass signal is

The bandwidth of the bandpass signal is

f

f

2 2

f

f

1 1

= 22.5

= 22.5

17.5 = 5 kHz and the

17.5 = 5 kHz and the

Simulink

Simulink

sampling rate is set to

sampling rate is set to

50 kHz

50 kHz

and results in only 32 768 = 2

and results in only 32 768 = 2

15 15

sampling points.

sampling points.

MS Figure 4

MS Figure 4

-

-

34

34

LSB USB

LSB USB

f

f

C C

Scaled PSD

Scaled PSD

f

f

max max

= 50 kHz

= 50 kHz

Aliased frequency range > 25 kHz

Aliased frequency range > 25 kHz

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Quantizing Process:

Quantizing Process:

Uniform Quantization

Uniform Quantization

Pages 400

Pages 400

-

-

404

404

EE4512 Analog and Digital Communications Chapter 8

The

The

quantizing process

quantizing process

divides the

divides the

range

range

(

(

full scale) into

full scale) into

2

2

n n

(n = 4 here) regions which are assigned an n

(n = 4 here) regions which are assigned an n

-

-

bit binary

bit binary

code.

code.

S&M Figure 8

S&M Figure 8

-

-

10

10

EE4512 Analog and Digital Communications Chapter 8

The

The

error

error

associated with the quantizing process is

associated with the quantizing process is

assumed to have a uniform probability density function.

assumed to have a uniform probability density function.

The maximum error for uniform quantization is:

The maximum error for uniform quantization is:

The quantizer range is

The quantizer range is

V

V

max max

and the uniform quantizer

and the uniform quantizer

voltage step size is:

voltage step size is:

The mean square quantizing E

The mean square quantizing E

q q

is the normalized

is the normalized

quantizing noise power:

quantizing noise power:

S&M Figure 8

S&M Figure 8

-

-

11

11

| |

= =

|

\ .

max max

n n

2 V V

q 0.5

2 2

= =

max max

n n-1

2 V V

2 2

( )

( )

/ 2

/ 2

= = = =

2 2 2

2

max max

q

2

2n

n

V V 1

E q dq

12

3 2

3 2

MS Eq. 4.7

MS Eq. 4.7

MS Eq. 4.6

MS Eq. 4.6

EE4512 Analog and Digital Communications Chapter 8

The

The

signal to quantizing noise power

signal to quantizing noise power

(SNR

(SNR

q q

) is:

) is:

P

P

S S

is the normalized power of the signal that is quantized.

is the normalized power of the signal that is quantized.

For the ADC here

For the ADC here

= 10 mV and n = 8. The sum of three

= 10 mV and n = 8. The sum of three

sinusoids as the input signal has a peak amplitude of 1.1 V

sinusoids as the input signal has a peak amplitude of 1.1 V

and the quantizing noise has a peak amplitude of 10 mV.

and the quantizing noise has a peak amplitude of 10 mV.

MS Figure 4.7

MS Figure 4.7

MS Eq. 4.8

MS Eq. 4.8

( )

= =

2n

S S

q

2 2

max

12 P P

SNR 3 2

V

10 mV

10 mV

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Quantizing Process:

Quantizing Process:

Nonuniform Quantization

Nonuniform Quantization

Pages 400

Pages 400

-

-

404

404

EE4512 Analog and Digital Communications Chapter 6

Nonuniform quantization divides the dynamic range of an

Nonuniform quantization divides the dynamic range of an

analog signal into nonuniform quantization regions. Lower

analog signal into nonuniform quantization regions. Lower

magnitudes have smaller quantization regions than high

magnitudes have smaller quantization regions than high

magnitudes.

magnitudes.

The quantization of speech benefits from nonuniform

The quantization of speech benefits from nonuniform

quantization since the perception of hearing is

quantization since the perception of hearing is

logarithmical

logarithmical

rather than linear.

rather than linear.

EE4512 Analog and Digital Communications Chapter 8

Uniform

Uniform

quantization

quantization

(top) results in

(top) results in

a large amount

a large amount

of error for

of error for

small sample

small sample

amplitude.

amplitude.

Non

Non

-

-

uniform

uniform

quantization

quantization

(bottom)

(bottom)

reduces the

reduces the

error for small

error for small

sample

sample

amplitudes.

amplitudes.

S&M Figure 8

S&M Figure 8

-

-

13

13

Uniform quantization Uniform quantization

Nonuniform quantization Nonuniform quantization

EE4512 Analog and Digital Communications Chapter 6

Uniform quantization is simpler to implement so a

Uniform quantization is simpler to implement so a

compressor

compressor

(a non

(a non

-

-

linear transfer function) is used before

linear transfer function) is used before

the quantizer.

the quantizer.

The

The

-

-

Law

Law

compressor

compressor

is used in

is used in

telephony

telephony

with MS Eq. 4.9

with MS Eq. 4.9

= 255. At the receiver

= 255. At the receiver

an expander has the

an expander has the

inverse non

inverse non

-

-

linear

linear

transfer function and

transfer function and

results in

results in

companding

companding

(

(

COMpressing

COMpressing

and

and

exPANDING

exPANDING

).

).

( )

| |

|

|

\ .

in

max

in

out max

max

V

ln 1+

V

V

V = V 0 1

ln 1+ V

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Companding

Companding

Pages 157

Pages 157

-

-

159

159

EE4512 Analog and Digital Communications Chapter 8

The

The

-

-

Law compander concept can be simulated in

Law compander concept can be simulated in

Simulink

Simulink

with the

with the

-

-

Law Compressor and

Law Compressor and

-

-

Law Expander

Law Expander

blocks. The A

blocks. The A

-

-

Law Compressor and A

Law Compressor and A

-

-

Law Expander

Law Expander

blocks are included for comparison.

blocks are included for comparison.

MS Figure 4.13

MS Figure 4.13

EE4512 Analog and Digital Communications Chapter 8

The

The

-

-

Law compressor voltage transfer function is

Law compressor voltage transfer function is

sigmoidal

sigmoidal

(S

(S

-

-

shaped).

shaped).

MS Figure 4.14

MS Figure 4.14

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Pulse Code Modulation

Pulse Code Modulation

Pages 171

Pages 171

-

-

175

175

EE4512 Analog and Digital Communications Chapter 8

The

The

pulse code modulator (PCM) transmitter utilizes a

pulse code modulator (PCM) transmitter utilizes a

Simulink

Simulink

-

-

Law compressor block, an 8

Law compressor block, an 8

-

-

bit ADC subsystem,

bit ADC subsystem,

an 8

an 8

-

-

bit DAC subsystem and a

bit DAC subsystem and a

-

-

Law expander block.

Law expander block.

MS Figure 4.21

MS Figure 4.21

EE4512 Analog and Digital Communications Chapter 8

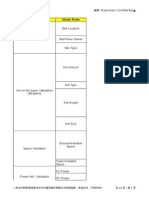

The

The

Simulink

Simulink

8

8

-

-

bit ADC subsystem has a sample

bit ADC subsystem has a sample

-

-

and

and

-

-

hold

hold

block controlled by a

block controlled by a

sampling

sampling

pulse generator, an 8

pulse generator, an 8

-

-

bit

bit

encoder block, an integer

encoder block, an integer

-

-

to

to

-

-

bit converter block which

bit converter block which

provides an 8

provides an 8

-

-

bit

bit

vector

vector

to a demultiplexer block and a

to a demultiplexer block and a

multiport switch.

multiport switch.

An 8

An 8

-

-

level

level

staircase

staircase

subsystem

subsystem

sequences the multiport switch to select 1 of the 8 inputs for

sequences the multiport switch to select 1 of the 8 inputs for

bit serial output.

bit serial output.

MS Figure 4.22

MS Figure 4.22

EE4512 Analog and Digital Communications Chapter 8

The 8

The 8

-

-

level

level

staircase Simulink

staircase Simulink

subsystem sequences the

subsystem sequences the

multiport switch with a 3

multiport switch with a 3

-

-

bit counter and a 3

bit counter and a 3

-

-

bit DAC for the

bit DAC for the

output.

output.

MS Figure 4.22

MS Figure 4.22

3

3

-

-

bit DAC

bit DAC

3

3

-

-

bit counter

bit counter

EE4512 Analog and Digital Communications Chapter 8

The 8

The 8

-

-

bit DAC

bit DAC

Simulink

Simulink

subsystem for the PCM system

subsystem for the PCM system

uses a 8

uses a 8

-

-

bit

bit

shift register

shift register

and an 8

and an 8

-

-

bit DAC.

bit DAC.

MS Figure 4.24

MS Figure 4.24

8

8

-

-

bit DAC

bit DAC

8

8

-

-

bit shift

bit shift

register

register

EE4512 Analog and Digital Communications Chapter 8

The 8

The 8

-

-

bit DAC

bit DAC

Simulink

Simulink

subsystem for the PCM system

subsystem for the PCM system

uses a 8

uses a 8

-

-

bit

bit

shift register

shift register

and an 8

and an 8

-

-

bit DAC.

bit DAC.

MS Figure 4.24

MS Figure 4.24

8

8

-

-

bit DAC

bit DAC

8

8

-

-

bit shift

bit shift

register

register

EE4512 Analog and Digital Communications Chapter 8

Analog input signal to the PCM system

Analog input signal to the PCM system

MS Figure 4.25

MS Figure 4.25

MS Figure 4.21

MS Figure 4.21

EE4512 Analog and Digital Communications Chapter 8

8

8

-

-

bit DAC output after 8

bit DAC output after 8

-

-

bit ADC and

bit ADC and

-

-

Law Compressor

Law Compressor

MS Figure 4.25

MS Figure 4.25

MS Figure 4.21

MS Figure 4.21

EE4512 Analog and Digital Communications Chapter 8

-

-

Law Expander block

Law Expander block

output of the PCM system

output of the PCM system

MS Figure 4.25

MS Figure 4.25

MS Figure 4.21

MS Figure 4.21

EE4512 Analog and Digital Communications Chapter 8

LPF

LPF

output of the PCM system

output of the PCM system

MS Figure 4.25

MS Figure 4.25

MS Figure 4.21

MS Figure 4.21

EE4512 Analog and Digital Communications Chapter 8

Analog input signal to the PCM system

Analog input signal to the PCM system

MS Figure 4.25

MS Figure 4.25

LPF output of the PCM system

LPF output of the PCM system

startup

startup

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Differential Pulse Code

Differential Pulse Code

Modulation

Modulation

Pages 407

Pages 407

-

-

411

411

EE4512 Analog and Digital Communications Chapter 6

Sampled speech data are

Sampled speech data are

highly correlated

highly correlated

and

and

differential

differential

pulse code modulation

pulse code modulation

(DPCM) exploits this to lower the

(DPCM) exploits this to lower the

overall data

overall data

rate.

rate.

DPCM

DPCM

uses a

uses a

predictor

predictor

to subtract

to subtract

a predicted

a predicted

value from

value from

the input.

the input.

The

The

error

error

difference

difference

is sent.

is sent.

S&M Figure 8

S&M Figure 8

-

-

15

15

EE4512 Analog and Digital Communications Chapter 6

The predictor is a recursive equation, for example:

The predictor is a recursive equation, for example:

S

S

(n

(n

) = 0.75 s(n

) = 0.75 s(n

1) + 0.2 s(n

1) + 0.2 s(n

2) +0.05 s(n

2) +0.05 s(n

3)

3)

where

where

S

S

(n

(n

)

)

is the

is the

predicted

predicted

value of the

value of the

n

n

th

th

sample

sample

and

and

s(n

s(n

-

-

i)

i)

is the

is the

n

n

-

-

i

i

th

th

sample.

sample.

The error

The error

signal is

signal is

s(n

s(n

)

)

S

S

(n

(n

)

)

S&M Figure 8

S&M Figure 8

-

-

15

15

EE4512 Analog and Digital Communications Chapter 6

A typical continuous analog signal is sampled and results in

A typical continuous analog signal is sampled and results in

a discrete signal

a discrete signal

s(n

s(n

), The discrete predicted signal

), The discrete predicted signal

S

S

(n

(n

) is

) is

recursively computed. The discrete error signal is

recursively computed. The discrete error signal is

transmitted and has less quantizing bits than the actual

transmitted and has less quantizing bits than the actual

discrete signal.

discrete signal.

S&M Figure 8

S&M Figure 8

-

-

16b

16b

EE4512 Analog and Digital Communications Chapter 6

A DPCM example of actual discrete values, predicted

A DPCM example of actual discrete values, predicted

values and the error terms:

values and the error terms:

S&M Table 8

S&M Table 8

-

-

3

3

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Differential Pulse Code

Differential Pulse Code

Modulation

Modulation

Pages 175

Pages 175

-

-

180

180

EE4512 Analog and Digital Communications Chapter 6

A 4

A 4

-

-

bit first order

bit first order

differential pulse code modulator

differential pulse code modulator

(DPCM)

(DPCM)

can be simulated in

can be simulated in

Simulink.

Simulink.

MS Figure 4.26

MS Figure 4.26

EE4512 Analog and Digital Communications Chapter 6

The first order linear predictor MetaSystem determines the

The first order linear predictor MetaSystem determines the

error signal:

error signal:

e(n

e(n

) = s(n+1)

) = s(n+1)

2

2

s(n

s(n

) + s(n

) + s(n

-

-

1)

1)

MS Figure 4.27

MS Figure 4.27

error signal

error signal

input

input

ADC conversion command

ADC conversion command

EE4512 Analog and Digital Communications Chapter 6

The

The

Simulink

Simulink

4

4

-

-

bit ADC subsystem of the DPCM system is

bit ADC subsystem of the DPCM system is

similar to the 8

similar to the 8

-

-

bit ADC of the PCM system and illustrates

bit ADC of the PCM system and illustrates

design reuse.

design reuse.

MS Figure 4.28

MS Figure 4.28

EE4512 Analog and Digital Communications Chapter 6

The

The

Simulink

Simulink

4

4

-

-

bit DAC subsystem of the DPCM system is

bit DAC subsystem of the DPCM system is

also similar to the 8

also similar to the 8

-

-

bit DAC of the PCM system and

bit DAC of the PCM system and

again illustrates

again illustrates

design reuse.

design reuse.

MS Figure 4.29

MS Figure 4.29

4

4

-

-

bit DAC

bit DAC

4

4

-

-

bit shift

bit shift

register

register

EE4512 Analog and Digital Communications Chapter 6

The first order linear predictor

The first order linear predictor

Simulink

Simulink

subsystem

subsystem

reconstructs an estimate of the signal

reconstructs an estimate of the signal

s

s

e e

(n

(n

) from the error

) from the error

signal

signal

e(n

e(n

) received and past estimates:

) received and past estimates:

s

s

e e

(n+1) = e(n+1) + 2

(n+1) = e(n+1) + 2

s

s

e e

(n

(n

)

)

s

s

e e

(n

(n

1)

1)

MS Figure 4.30

MS Figure 4.30

reconstructed

reconstructed

signal

signal

input

input

EE4512 Analog and Digital Communications Chapter 8

Analog in

Analog in

put signal of the DPCM system

put signal of the DPCM system

MS Figure 4.31

MS Figure 4.31

MS Figure 4.31

MS Figure 4.31

EE4512 Analog and Digital Communications Chapter 8

Output of the 4

Output of the 4

-

-

bit first order

bit first order

DPCM system

DPCM system

MS Figure 4.31

MS Figure 4.31

MS Figure 4.31

MS Figure 4.31

EE4512 Analog and Digital Communications Chapter 8

Analog input signal to the DPCM system

Analog input signal to the DPCM system

MS Figure 4.31

MS Figure 4.31

Output of the 4

Output of the 4

-

-

bit first order DPCM system

bit first order DPCM system

startup

startup

EE4512 Analog and Digital Communications Chapter 8

Output of the 8

Output of the 8

-

-

bit PCM system

bit PCM system

MS Figure 4.31

MS Figure 4.31

Output of the 4

Output of the 4

-

-

bit first order DPCM system

bit first order DPCM system

startup

startup

startup

startup

MS Figure 4.25

MS Figure 4.25

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Delta Modulation

Delta Modulation

Pages 411

Pages 411

-

-

415

415

EE4512 Analog and Digital Communications Chapter 6

Delta modulation

Delta modulation

is an extreme example of DPCM

is an extreme example of DPCM

using

using

1

1

-

-

bit data representing

bit data representing

:

:

S

S

(n

(n

) =

) =

S

S

(n

(n

1) +

1) +

b

b

i i

= 1 if

= 1 if

S

S

(n

(n

1)

1)

s(n

s(n

1)

1)

S

S

(n

(n

) =

) =

S

S

(n

(n

1)

1)

b

b

i i

= 0 if

= 0 if

S

S

(n

(n

1) >

1) >

s(n

s(n

1)

1)

S&M Eq. 8.10

S&M Eq. 8.10

S&M Figure 8

S&M Figure 8

-

-

18

18

DM transmitter DM transmitter

DM receiver DM receiver

EE4512 Analog and Digital Communications Chapter 6

The reconstructed signal increments

The reconstructed signal increments

on each

on each

transmitted bit.

transmitted bit.

b

b

i i

= 1

= 1

S

S

(n

(n

) =

) =

S

S

(n

(n

1) +

1) +

b

b

i i

= 0

= 0

S

S

(n

(n

) =

) =

S

S

(n

(n

1)

1)

S&M Figure 8

S&M Figure 8

-

-

19

19

4 1s 4 0s 4 1s 4 0s

EE4512 Analog and Digital Communications Chapter 8

Chapter 8

Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

Delta Modulation

Delta Modulation

Pages 72

Pages 72

-

-

75

75

EE4512 Analog and Digital Communications Chapter 6

Delta modulation (DM) can be simulated in

Delta modulation (DM) can be simulated in

Simulink

Simulink

. The

. The

DM receiver utilizes a sample and hold token as an

DM receiver utilizes a sample and hold token as an

accumulator and the step size

accumulator and the step size

= 20 mV.

= 20 mV.

MS Figure 2.61

MS Figure 2.61

DM transmitter

DM transmitter

DM receiver

DM receiver

f = 2 Hz

f = 2 Hz

A = 1 V

A = 1 V

f

f

S S

= 2 kHz

= 2 kHz

T

T

S S

= 0.5 msec

= 0.5 msec

EE4512 Analog and Digital Communications Chapter 6

DM can be subject to

DM can be subject to

slope overload

slope overload

which occurs when:

which occurs when:

/

/

T

T

S S

< max | d

< max | d

m(t

m(t

) /

) /

dt

dt

| SVU Eq. 2.61 modified

| SVU Eq. 2.61 modified

Here the sinusoid has A = 1 but f = 10 Hz and:

Here the sinusoid has A = 1 but f = 10 Hz and:

/

/

T

T

S S

= 20 mV / 0.5 msec = 40 < max | d

= 20 mV / 0.5 msec = 40 < max | d

m(t

m(t

) /

) /

dt

dt

| = 80

| = 80

and slope overload occurs.

and slope overload occurs.

MS Figure 2.63

MS Figure 2.63

sinusoidal

sinusoidal

input signal

input signal

EE4512 Analog and Digital Communications Chapter 6

Granular noise

Granular noise

occurs

occurs

in

in

DM because if the input

DM because if the input

m(t

m(t

) is

) is

constant the received signal

constant the received signal

oscillates

oscillates

by

by

because there

because there

is no

is no

0

0

possible.

possible.

Clocking

Clocking

occurs at the DM symbol interval

occurs at the DM symbol interval

T

T

S S

= 0.5 msec.

= 0.5 msec.

MS Figure 2.64

MS Figure 2.64

= 20 mV

= 20 mV

=

=

20 mV

20 mV

T

T

S S

= 0.5 msec

= 0.5 msec

EE4512 Analog and Digital Communications Chapter 6

The tradeoff between slope overload and granular noise is

The tradeoff between slope overload and granular noise is

that a large value of

that a large value of

(to avoid slope overload) would

(to avoid slope overload) would

increase granular noise. A decrease in

increase granular noise. A decrease in

T

T

s s

(again to avoid

(again to avoid

slope overload) would increase the data rate

slope overload) would increase the data rate

r

r

S S

.

.

The step size

The step size

= 20 mV and

= 20 mV and

T

T

S S

= 0.5 msec (

= 0.5 msec (

r

r

S S

= 2 kb/sec)

= 2 kb/sec)

here.

here.

EE4512 Analog and Digital Communications Chapter 6

For a 10 Hz sinusoidal input signal to a DM:

For a 10 Hz sinusoidal input signal to a DM:

m(t

m(t

) = sin (2

) = sin (2

10t)

10t)

max | d

max | d

m(t

m(t

) /

) /

dt

dt

|

|

= 20

= 20

If step size

If step size

= 20 mV and

= 20 mV and

T

T

S S

= 0.5 msec then

= 0.5 msec then

/ T

/ T

S S

= 40 < max | d

= 40 < max | d

m(t

m(t

) /

) /

dt

dt

| = 20

| = 20

so

so

slope overload is

slope overload is

predicted to occur

predicted to occur

.

.

EE4512 Analog and Digital Communications Chapter 6

For the 10 Hz sinusoidal input signal to a DM

For the 10 Hz sinusoidal input signal to a DM

m(t

m(t

) = sin (2

) = sin (2

10t)

10t)

max | d

max | d

m(t

m(t

) /

) /

dt

dt

|

|

= 20

= 20

and the step size remains

and the step size remains

= 20 mV but

= 20 mV but

T

T

S S

= 0.25 m

= 0.25 m

sec

sec

then

then

/ T

/ T

S S

= 80 > max | d

= 80 > max | d

m(t

m(t

) /

) /

dt

dt

| and slope overload is

| and slope overload is

mitigated but

mitigated but

r

r

S S

= 4 kb/sec.

= 4 kb/sec.

EE4512 Analog and Digital Communications Chapter 6

In comparison, an 8

In comparison, an 8

-

-

bit PCM system sampling a 10 Hz

bit PCM system sampling a 10 Hz

sinusoid at a reasonable sampling rate of 500 Hz (50

sinusoid at a reasonable sampling rate of 500 Hz (50

sampling points/period) has

sampling points/period) has

r

r

b b

= 8(500) = 4 kb/sec or

= 8(500) = 4 kb/sec or

r

r

b b

= r

= r

S S

but PCM is more complicated than DM.

but PCM is more complicated than DM.

EE4512 Analog and Digital Communications Chapter 8

End of Chapter 8

End of Chapter 8

Analog

Analog

-

-

to

to

-

-

Digital and

Digital and

Digital

Digital

-

-

to

to

-

-

Analog

Analog

Conversion

Conversion

You might also like

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (344)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (73)

- Aviat's WTM 4800: A Unique Single Box Multi-Band SolutionDocument33 pagesAviat's WTM 4800: A Unique Single Box Multi-Band SolutionAlmamata Ghsa99set100% (1)

- Paper - Comparison Study of Partial Discharge Detection Methods For SwitchgearsDocument5 pagesPaper - Comparison Study of Partial Discharge Detection Methods For SwitchgearsNguyen Vu Nhat HaNo ratings yet

- TQBM D609017 Q172717DEI 65FT2v02Document1 pageTQBM D609017 Q172717DEI 65FT2v02karen0% (1)

- Spectral DecompositionDocument165 pagesSpectral DecompositionaryoNo ratings yet

- ZTE - ZXSDR BS8900A Product DiscriptionDocument51 pagesZTE - ZXSDR BS8900A Product Discriptionkhurrambilal0193% (15)

- Survey On Anti-Drone Systems Components Designs AnDocument25 pagesSurvey On Anti-Drone Systems Components Designs AnORLANDO CASTILLONo ratings yet

- 15 PoeDocument11 pages15 Poejdwhite9No ratings yet

- WSNDocument12 pagesWSNzeemadevaksathaNo ratings yet

- Rahul Kumar 1015340078 Vivek Kumar 1015340117 Yashwantkumar 1015340119 Yogesh Kumar 1015340120Document13 pagesRahul Kumar 1015340078 Vivek Kumar 1015340117 Yashwantkumar 1015340119 Yogesh Kumar 1015340120Anonymous ytZsBOVNo ratings yet

- Chapter 4 Angle ModulationDocument18 pagesChapter 4 Angle ModulationAbdullah MasoodNo ratings yet

- El Centro Earthquake Data AnalysisDocument4 pagesEl Centro Earthquake Data AnalysisQueren SurianoNo ratings yet

- DB750X UserManualDocument46 pagesDB750X UserManualBob GageNo ratings yet

- ECEN689: Special Topics in High-Speed Links Circuits and Systems Spring 2010Document23 pagesECEN689: Special Topics in High-Speed Links Circuits and Systems Spring 2010Phoebe MensahNo ratings yet

- GMDSS Operator Reference Book Key4mateDocument36 pagesGMDSS Operator Reference Book Key4mateДенис КузаконьNo ratings yet

- Digital Communications - Viva Voce QuestionsDocument3 pagesDigital Communications - Viva Voce QuestionsAllanki Sanyasi Rao100% (1)

- Voice Procedure HandbookDocument15 pagesVoice Procedure HandbookJohn BradburyNo ratings yet

- XDM-100 GD A02 03 enDocument98 pagesXDM-100 GD A02 03 enrahulNo ratings yet

- Frenzel Q and ADocument15 pagesFrenzel Q and AJeffrey BernardoNo ratings yet

- A Security Framework in Rfid Based License PlateDocument3 pagesA Security Framework in Rfid Based License PlateJawahar BNo ratings yet

- USBee Air-Gap Covert-Channel Via Electromagnetic Emission From USBDocument5 pagesUSBee Air-Gap Covert-Channel Via Electromagnetic Emission From USBRanim JaafarNo ratings yet

- Attenuator CatalogDocument12 pagesAttenuator Catalogعبدالله الشهاريNo ratings yet

- SB6 W71CDDocument2 pagesSB6 W71CDIvan José Campos MadridNo ratings yet

- Link Planner Release Notes v5.2.0Document86 pagesLink Planner Release Notes v5.2.0Sukri AnsarNo ratings yet

- Carrier Phase Measurements GNSSDocument12 pagesCarrier Phase Measurements GNSSms050506dNo ratings yet

- Site validation checklist for ZTE confidential documentDocument10 pagesSite validation checklist for ZTE confidential documentJily RainNo ratings yet

- Structure of The Convolutional CodesDocument19 pagesStructure of The Convolutional CodesMathiNo ratings yet

- Parabolic Reflector BasicsDocument3 pagesParabolic Reflector BasicsShailaja UdtewarNo ratings yet

- Cadence Lab ReportDocument12 pagesCadence Lab ReportAnkur MorNo ratings yet

- MTI G09RRH-43 LTE RRH Band 8 Datasheet V1.0Document2 pagesMTI G09RRH-43 LTE RRH Band 8 Datasheet V1.0mohsin881No ratings yet

- Differences Between Routers, Switches and HubsDocument2 pagesDifferences Between Routers, Switches and HubsPappu KhanNo ratings yet