Professional Documents

Culture Documents

Chapitre 1

Chapitre 1

Uploaded by

القرآن الكريم0 ratings0% found this document useful (0 votes)

7 views19 pagesOriginal Title

chapitre1

Copyright

© © All Rights Reserved

Available Formats

PDF or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

0 ratings0% found this document useful (0 votes)

7 views19 pagesChapitre 1

Chapitre 1

Uploaded by

القرآن الكريمCopyright:

© All Rights Reserved

Available Formats

Download as PDF or read online from Scribd

You are on page 1of 19

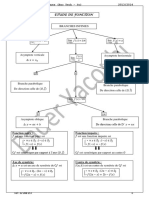

CQFS 25 Les éléments de grafcet

Définitions

Le grafcet est I'abréviation de l'expression GRAphe Fonctionnel de Commande

Etape Transition. C'est un outil qui permet de représenter des systtmes séquentiels &

événements discrets

Les principaux éléments du grafcet sont les suivants :

© Les étapes: elles sont représentées par des carrés. L’étape initiale active est

représentée par un carré double. On peut associer une variable logique a T’état de

chaque étape. En général, lorsqu’une étape est active, une action est exécutée par le

systéme commandé.

© Les transitions : elles représentent des conditions logiques & satisfaire pour faire

évoluer le grafcet. Elles sont représentées sous forme des traits horizontaux.

© Les réceptivités : En général, elles représentent des fonctions combinatoires dont les

variables peuvent étre :

© des variables logiques associées aux ¢tats des étapes,

o état d’un capteur,

© des variables logiques de temporisation.

© une réceptivité simplement et toujours vraie dans certains cas.

© Les ares orientés : ils permettent de relier les étapes et les transitions et déterminent

par la suite l’évolution du systéme.

Exemple a étape initiale

Le grafcet (Cf. Figure réceptivité

37) 2 3 étapes donne la “

signification des différents

léments. + abte

Dans cet exemple, C; est action

une variable logique qui “

représente la réceptivits de 1a 2 Haenont

transition liant les étapes 1 et 2.

On note aussi que C) est are

fonction d'autres variables +S -

logique (a, b et c). L’étape 1

est T'étape initiale active a

(représentée par un carré 3 L| Action 2 si condition

double). evape

‘A chacune des étapes 2 ee ha ea

et 3, on a associé des actions SG transition

qui sont exécutées par le

systéme commandé lorsque

T’étape correspondante est

active.

Figure 37 Exemple d'un grafcet

IT Systémes séquentiels 35

CQFS 26 Les cing régles du grafcet

Régle 1 : L’état initial du grafcet (étapes actives au départ) doit correspondre au début

du fonctionnement du syst#me.

Régle 2:

Une transition est validée si toutes les étapes qui la précédent sont actives. Dans le

cas contrare, elle est non validée. Le franchissement d’une transition se produit lorsque sa

réceptivité est vraie et elle est validée. Le franchissement se déclenche dés que ces deux

conditions sont réunies.

Regle 3 : Le franchissement d'une transition conduit & l’activation des étapes suivantes et

‘en méme temps 2 la désactivation des tapes qui la précédent.

Dans la figure ci-

contre, onillustre ! 1

Jadeuxitme et la | 1 2 a

troisitme régles. ° e

Pout franchir une

transition, deux ono oat

conditions sont uae

nécessaires : a

validité de cette 2 s fe é

transition et une 1 1 T T

Recep mamas 1 etcte enace 1

gil

Regle4: ‘| 2

Lorsque plusieurs

transitions sont Cost i qe

simultanément —

franchissables, alors )

elles sont simultanément ‘ 2 ‘

franchies. Cette régle est } ° .

illustrée dans exemple I T

de la igure suivante. Geaete4 ordi!

Régle 5: Si une méme étape doit étre

simultanément activée et désactivée,

alors elle reste active.

Une illustration de cette régle est

donnée dans la figure suivante. Dans cet

exemple, lorsque l'étape 2 est active et

C=0, cette méme étape est concemée

par la régle et en conséquence, elle reste

active. Le grafeet peut étre simplifié

sous une forme linéaire comme le

‘montre la figure ci-contre.

36 Ce quiil faut savoir

CQFS 27 Les structures de base ET et OU

Divergence en Ou : 1

Cotte structure illustre le choix entre deux évolutions

possibles. Le grafeet (Cf. Figure 38) illustre cette structure. En

effet, si ’étape I est active, on a le choix de passer par I’étape 2

ou par I’étape 3 selon les réceptivités C; et Co, Cette structure est

utile pour m¢ iser la notion de ’aiguillage. Toutefois, ce choix,

erée dans certains cas un probleme d'indéterminisme. On

considére Te cas oit Tes deux réceptivités C; et C2 sont vraies avant bend

aque I'éape I sactive Lindstetminisme se pose done des que “Swe 58 Divergence OU

Yon active I’étape I car 2 et 3 sont franchissables. D’aprés la rgle

4, les apes 2 et 3 sont simultanément activées et ceci sera

avcompagne de la désactivation de I'étape 1.

A Véchelle pratique, cela n'est pas ie rales

toujours commode et des conséquences [ | ’

indésirables peuvent en découler. Pour

remédier & un tel probléme, on doit établir

certaines priorités pour avoir un

fonctionnement déterministe du grafcet. © ae me, pom

Dans la figure ci-contre, on propose deux [ i [ 7 | 5 <

solutions. La premiére solution consiste &

rendre activation de I’étape 2 prioritaire.

En effet, si Ci=1, Pétape 2 sactive indépendamment de Cs. En revanche, I'activation de

Vétape 3 est conditionnée par la réceptivité C,. La deuxitme solution ne donne pas de

priorité & aucune de deux étapes et évite I'indéterminisme, mais génére un probléme de

blocage (si C; et Cz sont vraies avant I'activation de I’étape 1, le grafcet se blogue).

Divergence en Et : Cette structure traduit l’exécution simultanée de deux actions, On

parle de parallélisme (Cf. Figure 39). Le franchissement de la transition C entraine la

désactivation de I’étape 1 et Pactivation simultanée de I étape 2 et de V'étape 3.

Convergence en Ou:: Dans ce cas, une étape peut étre activée par plusieurs voies

possibles. Le grafcet (Cf. Figure 40) montre que I'étape 3 peut étre activée soit par la voie

de l’étape 1 soit par Mintermédiaire de V étape 2.

Convergence en Et: Dans ce cas, plusieurs processus en paralléle doivent s’achever

pour réaliser la suite, Ce type de structure peut étre utile pour modéliser les opérations

d'assemblage et la notion d’attente (Ct. Figure 41).

1 2 1 2

c

2 3 3 3

Figure 39 Divergence en Figure 40 Convergence en OU Figure 41 Convergence en

ET ET

CQFS 28 Sources, puits et partage de ressource

Sources et puits

Une éiape est dite

source si aucune transition

ne la précéde

étape source

immédiatement. Une étape

puits est une étape qui n’est

suecédée par aucune

transition.

Une transition est dite

source si aucune étape ne la

précéde — immeédiatement.

Elle est dite puits si elle

n'est suecédée par aucune

étape. (Cf. Figure 42).

Partage de ressource

Cette notion —est

importante car elle est souvent

rencontrée. Par exemple, dans

le cas de Ia gestion d’une

ressource qui peut étre

sollicitée par deux processus en

méme temps. La ressource ne

pouvant réaliser qu’une seule

t€che a la fois, son service doit

@tre altermé entre les deux

processus.

La figure ci-contre

montre un cas de partage d’une

ressource & deux processus.

L’exemple illustre le

fonctionnement d’un robot

(4ape 33) qui réalise

Popération de pergage de deux

types de pices A et B sur deux

chaines différentes. de

production. Cette opération est

transition puits

Figure 42 Sources e

transition source

étape puits

t puits

10 [asl

Gq

nf

pereage

Fin de percage

21 | percage

Fin de pergage

v v

Figure 43 Partage de ressource

nécessaire & la réalisation des autres opérations dans les deux processus. La notion de

partage de ressource fait elle aussi apparaitre le probléme d’indéterminisme qu’on a dja

précédemment évoqué et nécessite par Ia suite de prévoir des solutions afin d’éviter les

conséquences non désirées.

CQFS 29 Les synchronisations des grafcets

Synchronisation

unilatérale 10. || commencer A

Cette notion permet de

gérer certains aspects :

conflictuels et de —_ faire i

paralléle en ne donnant ul 20 | [eommencer B

communiquer deux processus en

50 |

Vautorisation 2 un processus

au’aprés avoir déclenché le plus

prioritaire, Dans Je grafeet (Cf.

Figure 44), deux tiches, A et B,

sont en paralléle. La

synchronisation ne permet de

démarrer la tache B qu’aprés

avoir commencé la tache A (le i

plus prioritaire). En effet, pour

commences Ia tiche 2, on a Figure 44 Synchronisation unilatérale

besoin @activer les étapes 50 et

20.

Or l'activation de I'étape 50 nécessite I’activation préalable de I’étape 10 ce qui signifie

que l'on a besoin de commencer préalablement la tache A.

Synchronisation bilatérale CQ = &

Cette structure permet aussi de 10 20

faire communiquer plusieurs processus

en paralléle en les bloquant pour les

reprendre plus tard en méme temps.

Dans le grafeet (Cf. Figure 45),

deux processus sont mis en paralléle. 00

L’éape 10 appartient au premier

processus et I’étape 20 appartient au

deuxigme processus. Pour passer de

Vétape 10 A V'étape 11, le premier

processus doit attendre Vactivation de u 21

Pétape 20 dans le deuxime processus.

Réciproquement, le_—_deuxiéme

processus peut commencer I’étape 21 &

condition que T’étape 10 ait dg été

validée. Figure 45 Synchronisation bilatérale

Ce type de structure peut étre

utile dans la synchronisation de

plusieurs processus pendant une étape

précise.

CQFS 30 Grafcet et hiérarchisation

Pour réaliser des solutions efficaces, l'outil de grafcet permet de construire

plusieurs graphes pour un méme systéme et offre la possibilité de les faire communiquer

par plusieurs voies.

Ss 7 a Gt G2

Le dialogue étape-transition | ze

Tl permet de = coordonner_— le ii Pi

fonctionnement de plusieurs parties dans un ou

plusieurs grafcets en associant des variables

logiques (X) aux tats des étapes. Ces

variables peuvent étre utilisées dans les

réceptivités associées aux transitions.

CG

Par exemple, dans le grafcet (Cf. Figure

46), la variable X;1 indique P’état logique de

Vétape 11. C’est-2-dire, Xi,=1 si l’étape 11 est

active et X;;=0 sinon. Par la suite, l’activation

de Pétape 22 ne dépend pas que de Xo1 et de

Cz mais également de l'état de I’étape 11 qui

doit étre inactive.

Figure 46 Dialogue étape-transition

les macro-étapes

‘Une macro-étape est une

étape qui représente une partie

d'un grafcet.

Ce mode de

représentation a pour objectif

de simplifier le grafcet et

éviter de Valourdir par les

détails annexes.

La représentation d’une

cro-étape obéit A une regle

précise. Dans le grafcet (Cf.

Figure 47) montre un exemple

@une macro-tape 15 notée

ME. On peut remarquer que

Téape 15 a été représentée

dans un carré avec deux traits :

horizontaux pour indiquer qu’il Figure 47 Exemple d'une macro-étape

s’agit d’ une macro-étape.

DYautre part, ce type de structure peut étre trés utile lorsque les actions

correspondantes la macro-étape doivent étre exécutées plusieurs fois. Dans ce cas, il

suffit de faire appel & la macro- Microprocesseur

> Mémoire constructeur (ROM)

> Mémoire ut (RAM)

Modules de communication

“Modules dlentrées et sorties

Figure 50 Architecture API Figure 51 Gamme d’API

Les API monoblocs ou modulaires

On distingue les API de bas de gamme, monobloes (Cf. Figure 51), qui integrent,

dans un seul module, la carte mére, nommée Unité Centrale (UC ou CPU), et les cartes

Pentrées et de sorties pour le dialogue avec la partie opérative. Les API de haute gamme

sont, en général, modulaires, les modules de communication, d’entrées et de sorts,

nécessaires & T’application, sont connectés au bus interne de I’ API.

L’immunité des API

Un APIest trs robuste ; il peut travailler dans des milieux trés hostiles. Un API est

protégé contre les effets néfastes des champs électromagnétiques produits par des

moteurs, des bobines ou des transformateurs. Un API est protégé, aussi, contre les

curtensions sur ses entrées ou les surintensités au niveau de ses sorties. Ceci néduit

fortement les codts de maintenance, d’un point de vue temps et matériel.

Principaux constructeurs d@'APL

Les principaux constructeurs d’ API sont allemands, américains, frangais, japonais et

suédois. Par exemple : ABB, ALLEN BRADLEY, BOSCH-REXROTH, FESTO, GE-

FANUC, HONEWELL, MITSHUBISHL, OMRON, SCHNEIDER-ELECTIC, SIEMENS,

VIPA.

CQFS 33 Le choix de I’Unité Centrale d'API

Le choix de l'unité centrale (UC) d’un API est conditionné par son prix, ses

performances ou son temps de réponse, ses possibilités de connexion & des réseaux, ses

capacités de calcul et de la taille de sa mémoire

Le prix de ?UC

Le prix de 'UC varie entre 200 € et 1500 € en fonction des capacités qu'elle

posséde. Le prix intervient dans le choix de I’ API, mais il reste trés faible en comparaison

avec T'ensemble du projet. Dans un méme projet, Ie coiit est celui de Pétude, de la

réalisation, des services offerts au client et du profit dégagé par le projet. La plupart du

temps le prix de I’ API complet représente seulement un vingtitme du prix de la machine

compltte, Dans Ie cas d'une machine unitaire, pour abaisser les coats de l'étude, il faut

privilégier des logiciels offrant une grande facilité de programmation..

Le temps de réponse

Le temps de réponse est fonction de la vitesse du microprocesseur, du temps dacces

ala RAM et de la taille du programme. Le constructeur donne généralement la valeur du

temps de traitement d'un bit ou d’un mot. Par exemple la CPU 215 VIPA posséde un

temps de traitement d'un bit de 0,18us et d’un mot de 0,78s. Le temps de scrutation du

programme se déduit par la multiplication du nombre de traitements de bits et de mots par

le temps de traitement d’un bit et d’un mot.

La connexion a des réseaux

Les API modulaires de haute gamme ont la possibilité d’étre

connectés & des réseaux. Des cartes additionnelles, coupleurs de

communication, assurent le dialogue avec d'autres équipements

branchés & des réseaux PROFIBUS, ETHERNET, JBUS, etc. La

photo (Cf. Figure 52) montre un module ETHERNET d'un API.

Certaines UC sont dotées d’un réseau local & ’API tels que le

PROFIBUS DP. La tendance actuelle est 1a connexion au réseau fjeure 52 Module

ETHERNET directement sur ?'UC. “ETHERNET

Les possibilités de calculs des UC

Les API de bas de gamme intégrent des fonctions de calcul simples. Les API de

haute gamme offrent la possibilité de faire des calculs complexes sur des variables réelles,

de traiter des chaines de caractéres, d’utiliser des fonctions de régulation (PID), de

dialoguer avec d'autres équipements, etc.

La taille mémoire des UC

La mémoire des API est encore trés chére. Elle doit étre nécessaire et suffisante

pour accepter le programme. En général, la taille mémoire, utilisée pour le programme

utilisateur, évolue de 48 KB a 512 KB. Certaines UC sont dotées de mémoire flash. Cette

mémoire sauvegarde le programme. A Ja mise sous tension de I’API, le programme,

résidant dans la mémoire flash, est transféré dans la RAM de I’ API. Elle peut aussi servir

a stocker des données de production.

CQFS 34 Le temps de réponse d’un API

Le temps de réponse est Je retard entre Vapparition d'un signal dentrée et

apparition du signal de sortie, on parle de causalité. Le temps de réponse d’un API

dépend de la période de scrutation qui peut étre facilement mesurée.

La période de scrutation (Ps)

Le temps de réponse est lié & la rapidité du microprocesseur, au temps de filtrage

des entrées, 8 la taille du programme et au retard des sorties. Toutes les équations décrites

dans le programme sont lues et effectuées, au cours d'un cycle de scrutation. La période

de sorutation (Ps) est la somme des temps mis pour effectuer les opérations du systéme

d'exploitation, pour la lecture des entrées, pour le traitement du programme et pour le

forcage des sorties.

© Opérations systéme d’exploitation (Tos): Temps de °

traitement des tiches propres au fonctionnement de 2,8 \ge|8

l'API, traitement des blocs d’ organisation (OB) 2s DSlES 98

© Lecture des entrées (Te): Temps de forcage des bits S28 22 5f 85

images des entrées selon I’état des entrées physiques. eo" 8 Fale

© Traitement du programme (71) : Temps pour effectuer wae Cn

les équations décrites dans le programme utilisateur. pe ae ae

© Forgage des sorties (7s) : Temps de forcage des sorties «« Pétiode de sorutation

physiques selon I’état des bits images des sorties. Figure 53 Cycle API

a

La période de scrutation (Ps = Tos + Te + Tt + Ts) est comprise entre quelques

millisecondes et quelques dixigmes de secondes. Un bit interme nommé chien de garde

passe A Iétat 1 lorsque le temps d’un cycle dépasse le temps maximal de scrutation. Dans

ce cas on considére que I’ API n'a plus le contrdle, I’ API passe en mode STOP.

La cansalité est Je temps entre V'apparition d'une

entrée et apparition d'une sortie. Si un Générateur Basse,

Fréquence (GBF) est branché sur une entrée Tout Ou Rien 5

(TOR) d’un API, et si le programme demande la mise a

Vétat haut d’une sortie $ lorsque entrée E est al,le

déphasage entre le signal de entrée et celui de la sortie

‘peut étre mesuré par un oscilloscope (CE. Figure 54).

“lat

Figure 54 Déphasage E/S

La mesure de la période de scrutation

La mesure de la période de scrutation peut étre facilement effectuée en comptant les

permutations d’un bit mis en oscillation, pendant un laps de temps fini, Les permutations

dun bit mis en oscillation, pendant un laps de temps fini.

Le réseau (Cf, Figure 55), fait osciller le bit Keres"! ‘itd

MIO.1. Ce bit passe A ’état 1 au cours d'une scrutation "| ©)

et passe a 0 au cours de la scrutation suivante. A chaque péseay 9

front montant du bit M101, le mot MW100

Sania i = MI0.1 M10 _

s‘inerémente. Deux scrutations sont nécessaires pour) j (py ADD_I }-

que le bit M10.1 passe de 0 a 1. La fréquence de MWi00 |

scrutation est la valeur de MW100 au bout d’une 11 MW100

seconde, multipliée par 2. Figure 55 Mesure de Ps

CQFS 35 Les cartes d’entrées TOR

Les cartes d’entrées Tout Ou Rien (TOR) sont utilisées pour I'acquisition des

signaux binaires. Un bit interne dit «d’entrée » passe & I’état 1, lorsque la tension sur

Ventrée est supérieure & un seuil. Les cartes d’entrées TOR acceptent des composants

fournissant une tension, comme des boutons poussoirs, interrupteurs, roues codeuses,

capteurs de fin de course, etc.

La compatibilité des composants

La plupart des entrées TOR, des API, sont PNP, clest-2-dire par établissement du

+24V. Attention, certains capteurs sont & sortie NPN, par éiablissement de masse. Bien

que l’alimentation de I’ API puisse convenir, il est préférable d’alimenter les entrées par

une alimentation externe avec sa masse reliée & celle de ’API. Le choix du 24V pour les

cartes d’ entrées, ouvre un éventail important de composants industriels.

La protection des entrées d’un API

Les entrées d'un API sont protégées grace & un opto-coupleur qui isole I'électronique

de I'API avec l'extéricur. Une tension, sur l’entrée de API, entraine une différence de

potentiel sur la diode de l'opto-coupleur, la lumigre émise par sa diode commute le

phototransistor. Une erreur de cablage (ou de tension) ne peut entrainer, au pire, que la

degradation de 'opto-coupleur.

Le filtrage des entrées d’un API

Un parasite sur une ligne d’entrées ne doit pas étre considéré comme une entrée

effective. La plupart des cartes d’entrées TOR ne force les bits images des entrées qu'au

bout d'un certain temps Te. Un parasite de durée plus faible ne sera pas pris en compte.

Mais ce filtrage crée un retard (Te) entre apparition de I’entrée et son bit image.

24y

La quantification des besoins ‘ yi

m

Le nombre d’entrées TOR, a prévoir doit, Vs eae

au minimum, couvrir les besoins de +2 BOL

application, Par exemple, une machine spéciale dat #02 8

est constituée d’un pupitre de commande | BHO E03

possédant 2 boutons poussoirs (m et a), 1 : ee

interrupteurs (0) et une roue codeuse 1 digit (bit + bal m4 &

4 bit2). La partie opérative posséde deux vérins bid Hos

dotés, chacun, de deux fins de course (a0, al, b0 86 SP

et bl). Un capteur inductif PNP (pp) détecte la os eee te

présence d’une pice. On dénombre un besoin de sal E07 &%

11 entrées TOR. Le cablage et I’attribution aux | Inia @

bits d’entrées de la carte d’entrées TOR peuvent oi ar

@tre faits comme lindique le croquis ci-contre 4 ea

(Cf. Figure 56). Noter que la carte doit étre Lg? ta

connectée al’ alimentation 24V. “an

Figure 56 Carte d’entrées TOR

CQFS 36 Les cartes de sorties TOR

Les cartes de sorties TOR commandent des actionneurs Tout Ou Rien. Das le

forcage d’un bit de sortie, la carte fournit une tension, & 1 ou & 0, sur la sortie. Des

composants, comme des contacteurs, des électrovannes, des voyants, peuvent étre

commandés par ces sorties,

Le temps de réponse d’une sortie

Le temps de réponse d’une sortie (Ts), est le temps entre l'apparition du bit image

de la sortie et la présence de tension sur cette sortie API. Une sortie & relais est assez

lente, le retard de commutation (7) dun relais peut étre supérieur & 30ms. Par conséquent

il ne sera pas possible de faire clignoter une sortie de ce type & une fréquence supérieure

15H2z, Les sorties a transistors sont plus rapides, le temps (7) peut étre inférieur & 1ms

Les types de sorties API

Les sorties TOR, réalisées avec des relais électromécaniques, offtent une grande

robustesse. Elles possédent un contact sec ayant un pouvoir de coupure de 1A a 5A.

suivant les modéles. Ce dernier est protégé par un fusible. Les sorties TOR peuvent étre

aussi réalisées avec des transistors ou des triacs. Les premitres sont utilisées pour les

actionneurs dont la tension d'alimentation est & courant continu, les secondes pour ceux &

courant alternatifs,

L’alimentation des sorties API

Alors que pour les entrées API il est possible d’utiliser ’alimentation de API, pour

les sorties une alimentation externe est indispensable. Elle doit fournir un courant

suffisant pour alimenter tous les actionneurs. La tension fournie par les sorties, doit étre

compatible avec celle des différents actionneurs 4 commander.

Le nombre de sorties TOR, a prévoir 2a « 2av

doit, au minimum, couvrir les besoins. Par om E00

exemple, le pupitre de commande, d'une a der

machine spéciale posstde trois yoyants (V7,

V2 et V3) 24V / 5W. Le voyant V2 doit ot oS

clignoter & la fréquence de 40 Hz. La partie bia

opérative comprend un vérin (4) commandé far ese

par une électrovanne10W bistable 24 V= et un rage &

moteur commandé par deux contacteurs (AV et bid mos &

AR) 24V, 8W. La fréquence de 40 Hz interdit +20 mos &

des sorties & relais. La tension des composants i aaa.

conduit au choix d’un module de sorties & . a

transistors TOR 24Vcc/1A. La carte, pour + 0 BLO

chaque sortie, doit fournir un courant de 0,42 ~ 1 bl Ell

A (lOW/24v). On dénombre un total de 9 Pp

sorties TOR (Cf. Figure 57). r8 EL2.

Figure 57 Carte de sorties TOR

CQES 37 La carte d’entrées analogiques

La carte d’entrées analogiques est constituge d’un Convertisseur Analogique

Numérique (CAN). Elle est utilisée pour l'acquisition d'une tension (OV a 10V ou -5V a

+5V) ou d'un courant (4 mA & 20 mA) qui varie entre deux bornes sans discontinuité. Un

mot interne d’entrée est image de la tension ou du courant deentrée. Tous les capteurs

analogiques (potentiometres, par exemple) peuvent y étre cablés. La résolution est

directement lige au nombre de bits du CAN.

Le Convertisseur Analogique Numérique (CAN)

Le circuit ADCO804 (Cf. Figure 58) est un Vin (+) [6 G]__ DT

CAN 8 bis. Ses sorties (D0 @ D7), raccordées au Vin (-) 17 12-— D6

bus de données, donnent un mot de 8 bits image Masse Ana (8 13 D5

de la tension Vin. Les masses sont séparées, cect Vref/2 9 apcosot i4-— D4

CLK OUT—19 CAN is —D3

évite l'absorption des parasites éventuels. Deux E

CLEIN-14 ght 16— D2

signaux dhorloge peuvent étre utilisés, celui du

micro processeur ou bien un signal exteme, Avec /CS , age

tune horloge de 606Hz, la durée de la conversion ‘yz 5 as

s’effectue en 100 ps. Il est possible de donner Een

une tension de référence Vref, pour modifier la __ Masse numérique

plage de la tension d’entrée mesurée. ‘Wie e erereiic

igure

Le mot image d’entrée analogique

La valeur image de la mesure est stockée

dans un mot de 16 bits d'entrées : EWn, (n = 2047 t

adresse de octet d’entrée). Comme une entrée :

TOR ce mot peut étre lu & tout moment. La LA

courbe, (Cf. Figure 59) montre la variation du oF SmV

mot image en fonction de la valeur analogique |

entrée. Si le Convertisseur Analogique 2048

Numérique (CAN) posséde 12 bits et si la “lV OV +10

tension varie de -10 & 10V, le mot image Figure 59 Courbe CAN

évolue entre -2048 et 2047.

La résolution d’un CAN

La résolution est Je plus petit écart de tension mesurable. Le mot image est un

entier, la courbe liant la valeur du mot et [entrée analogique n’est donc pas continue,

comme le montre le zoom sur la courbe (Cf. Figure 59), La résolution est la division de la

plage mesurée par la plage du mot image : R = Plage/Mot. Nota: Certains API

convertissent ces 12 bits en un mot de 16 bits évoluant, dans ce cas, entre -32768 A

+32767, la résolution n’en est pas améliorée pour autant, Par exemple, un capteur LVDT

donne, pour un déplacement de son palpeur de 0 & 8,19 mm, une tension évoluant entre 0

et 10 V. La sortie analogique de ce capteur est relige A l’entrée d’une carte CAN 12 bits

qui donnent un mot image compris entre 0 et 4095. La résolution est de 10/4095, soit

environ 0,25 mV et correspond & un déplacement de 0,002 mm du palpeur.

CQFS 38 Les cartes de sorties analogiques

Les cartes, de sorties analogiques, sont constituées d’un Convertisseur Numérique

Analogique (CNA). Ses sorties fournissent une tension proportionnelle & un mot de sortie

image, interne & la carte, pour commander un actionneur (ou un pré actionneur) acceptant

tune consigne de tension. Elles conviennent & la commande des variateurs de moteurs. La

résolution de tension obtenue est dépendante du nombre de bits du CNA.

Le Convertisseur Numérique Analogique (CNA)

Un Convertisseur Numérique Analogique CNA (Cf. Figure 60) peut étre construit

avec un réseau R/2R de base qui n'utilise que des résistances de méme valeur.

La tension de sortie” Vref

Vsortie est dépendante du

mot noté B, codé en 1 i 2R

binaire, dont ses bits sont 2k] eR 2R QR’

BO, BI, B2et B3etdela _?R | R, LR Bi Lk ., LVsortie

tension d’entrée Vref. A a

BO Bl BD BB

Figure 60 Schéma d’un CNA RR

Le mot image de sortie analogique

Comme une sortie TOR, un mot interne de sortie AWn, TOV

avec n adresse de l’octet de sortie de la carte, est foreé A une

valeur par le programme. Par exemple, si ce mot est codé sur gy

16 bits, si AWn est forcé & la valeur 0 Ia sortie de la CNA

prend la valeur nulle, si ce mot est forcé & la valeur +32767, la

sortie prend la valeur maximale (10 V). La courbe (Cf. Figure ~10V «

61) montre la variation de la sortie analogique en fonction de 768 OO sei!

la valeur du mot AWn. Figure 1 Comite GNA

La résolution d’un CNA.

Le nombre de bits d’un CNA peut varier entre 8 et 16, un grand nombre de bits

donne une variation fine de la tension de sortie. Si le CNA posstde 16 bits et fournit une

tension de -10V 4 +10V, la résolution est de 20 V divisée par 65535, c’est-a-dire environ

0,3 mV pour un point. Le croquis (Cf. Figure 62) représente le cablage d’un moteur avec

son variateur (V). Une carte CNA envoie une tension de consigne proportionnelle & la

vitesse du moteur (M) désirée.

Par exemple, une carte CAN, de 12 bits, est

affectée de l’adresse 30. Le mot AW30, interme & la

CAN évolue done entre -2047 & +2047. Il peut moduler

Ja tension, envoyée a la consigne d’entrée du variateur,

entre -10 V et +10 V. Si la plage de vitesse du moteur

est de -2000 & +2000 min, la résolution est de 0.976

min. (4000/4096).

Figure 62 Commande d'un

moteur

You might also like

- Exercice 1Document11 pagesExercice 1القرآن الكريمNo ratings yet

- TD 4Document4 pagesTD 4القرآن الكريمNo ratings yet

- TD1 Partie2Document4 pagesTD1 Partie2القرآن الكريمNo ratings yet

- TD 1Document2 pagesTD 1القرآن الكريمNo ratings yet

- Lecture 5-1Document22 pagesLecture 5-1القرآن الكريمNo ratings yet

- Lecture 2Document18 pagesLecture 2القرآن الكريمNo ratings yet

- TD 2: Transistor À Effect de Champ (TEC) À Junction (Ou JFET)Document4 pagesTD 2: Transistor À Effect de Champ (TEC) À Junction (Ou JFET)القرآن الكريمNo ratings yet

- TD4 CorrectionDocument4 pagesTD4 Correctionالقرآن الكريمNo ratings yet

- Lecture 1Document48 pagesLecture 1القرآن الكريمNo ratings yet

- Chapitre 2Document31 pagesChapitre 2القرآن الكريمNo ratings yet

- Chapitre5 LMD SuiteDocument20 pagesChapitre5 LMD Suiteالقرآن الكريمNo ratings yet

- Chapitre 1Document26 pagesChapitre 1القرآن الكريمNo ratings yet

- Cours Transmission de Donnees Ch1Document45 pagesCours Transmission de Donnees Ch1القرآن الكريمNo ratings yet

- Chapitre 3 NormalisationDocument38 pagesChapitre 3 Normalisationالقرآن الكريمNo ratings yet

- Chapitre 1 Introduction Et HistoriqueDocument29 pagesChapitre 1 Introduction Et Historiqueالقرآن الكريمNo ratings yet

- Chapitre 5 LMDDocument28 pagesChapitre 5 LMDالقرآن الكريمNo ratings yet

- Exam1 (Rattrapage)Document2 pagesExam1 (Rattrapage)القرآن الكريمNo ratings yet

- Chapitre 2 Système de Numération Et CodageDocument11 pagesChapitre 2 Système de Numération Et Codageالقرآن الكريمNo ratings yet

- Exam1 (Principale)Document2 pagesExam1 (Principale)القرآن الكريمNo ratings yet

- TP1 Réfraction de La Lumière 1Document6 pagesTP1 Réfraction de La Lumière 1القرآن الكريمNo ratings yet

- tp4 HTMLDocument4 pagestp4 HTMLالقرآن الكريمNo ratings yet

- CM2 Vision Et CouleursDocument9 pagesCM2 Vision Et Couleursالقرآن الكريمNo ratings yet

- FX FX FX A: Fonction Paire: Fonction ImpaireDocument3 pagesFX FX FX A: Fonction Paire: Fonction Impaireالقرآن الكريمNo ratings yet

- tp2 Web1Document3 pagestp2 Web1القرآن الكريمNo ratings yet