Professional Documents

Culture Documents

Presentación Semana 6

Uploaded by

Alejandra ZunigaOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Presentación Semana 6

Uploaded by

Alejandra ZunigaCopyright:

Available Formats

Agenda

Saludos.

Lista de asistencia.

Avisos.

Video de Memorias Flash.

Clase.

Fin de clases.

Tema.

Qu es la memoria cach?.

Tipos de memoria.

Funcionamiento.

Estructura de la memoria cach.

Estructura de la memoria principal.

Diseo de cach.

Objetivo:

Analizar el funcionamiento y caractersticas de las

memorias cach.

Qu es la memoria Cach?

Bsicamente, la memoria cach de un

procesador es un tipo de memoria voltil (del

tipo RAM), pero de una gran velocidad.

Es un tipo especial de memoria, que permite

a la CPU acceder a las direcciones y datos que

se encuentran contenidos en sta de manera

mucho ms rpida que su acceso a la memoria

principal (de 3 a 5 veces ms rpido).

Figura 4.3 Memoria cach y principal.

Cont

En la actualidad esta memoria est integrada en el

procesador, y su cometido es almacenar una serie de

instrucciones y datos a los que el procesador accede

continuamente, con la finalidad de que estos accesos

sean instantneos.

Estas instrucciones y datos son aquellas a lasque el

procesador necesita estar accediendo de forma

continua, por lo que para el rendimiento del

procesador es imprescindible que este acceso sea lo

ms rpido y fluido posible.

Tipos de Memoria.

Los diferentes tipos de cach se organizan por

niveles, formando una jerarqua. En general se

cumple que, a mayor cercana al CPU, se presenta

mayor velocidad de acceso y menor capacidad de

almacenamiento.

Cach de 1er nivel (L1):

Esta cach est integrada en el ncleo del procesador,

trabajando a la misma velocidad que este. La cantidad

de memoria cach L1 vara de un procesador a otro,

estando normalmente entra los 64KB y los 256KB.

Esta memoria suele a su vez estar dividida en dos

partes:

L1 DC: Level 1 data cache, cach de datos : se encarga de

almacenar datos usados frecuentemente y cuando sea

necesario volver a utilizarlos, inmediatamente los utiliza, por

lo que se agiliza los procesos.

L1 IC: Level 1 instruction cache, cach de instrucciones: se

encarga de almacenar instrucciones usadas frecuentemente

y cuando sea necesario volver a utilizarlas, inmediatamente

las recupere, por lo que se agilizan los procesos.

Cont

Cach de 2 nivel (L2):

Conocido como cache externa, inicialmente se instalaba

en la placa base (en el exterior de la CPU).

A partir de los procesadores Pentium 4 viene

incorporado en el procesador (no precisamente en el

ncleo).

El nivel L2 apareci con el procesador Pentium Pro, es

una memoria ms lenta que L1, pero de mayor

capacidad.

Los tamaos tpicos de la memoria cache L2 oscilan en la

actualidad entre 256KB y 4 MB.

Cont

Cach de 3er nivel (L3):

Se encuentra en algunas placas base, procesadores y

tarjetas de interfaz.

El procesador de Intel Itanium trae contenida en su

cartucho al nivel L3 que soporta un tamao hasta de 4

MB, y el Itanium 2 tolera hasta 6MB de cache L3.

Cache de 4er nivel (L4):

Se encuentra ubicado en los perifricos y en algunos

procesadores como el Itanium.

Cont

Elementos que componen el

procesador (distribucin fsica.)

Funcionamiento.

CPU realiza un requerimiento de acceso a una

direccin de memoria.

Revisa el cach por estos datos.

Si existe en el cach, tomar los datos.

Si no existe, leer el bloque requerido de

memoria principal y guardarlo en el cach.

Enviar los datos del cach al CPU.

Organizacin tpica de cach.

Estructura de memoria cach.

.

.

.

Bloque Etiqueta

Nmero de lnea

0

1

2

C -1

Longitud

De bloque

(K palabras)

Estructura de memoria principal.

.

.

.

.

.

Direccin de memoria

0

1

2

3

2

n

- 1

Longitud de

palabra

Bloque

(K palabra)

Bloque

Diseo de cach

Tamao.

Funcin de correspondencia.

Algoritmo de reemplazo.

Poltica de escritura.

Tamao de Cach

Costo:

Mayor tamao, mas caro.

Rapidez:

Las memorias cachs ms grandes tienden a ser

ligeramente ms lentas que las pequeas.

Funcin de correspondencia o polticas

de ubicacin

Algoritmos que permiten hacer corresponder

bloques de memorias principal a lneas de

memorias cach.

Las funciones de correspondencias son:

Correspondencia directa.

Correspondencia asociativa.

Correspondencia asociativa por conjunto.

Funcin de correspondencia o poltica de

ubicacin.

Elementos de considerar.

La cach puede almacenar 64 Kb.

Los datos se transfieren entre la memoria principal y la

cach en bloques de 4 bytes. Estos significa que la

cach esta organizada en 16KB = 2

14

lneas de 4 bytes

cada una.

La memoria principal es de 16MB, con cada byte

directamente direccionable mediante una direccin de

24 bits (2

24

= 16MB). As pues, al objeto de realizar la

correspondencia, podemos considerar que la memoria

principal consta de 4M bloques de 4 bytes cada uno.

Correspondencia Directa estructura de la

direccin.

Direccin de 24 bits.

Identificador de palabra: 2 bit(bloque de 4 bytes).

Identificador de bloque: 22 bits.

Etiqueta de 8 bits, identifica al bloque de memoria

Lneas de 14 bits, identifica, la lnea de la memoria cach a la

que corresponde el bloque.

Se chequean los contenidos en el cach encontrando la lnea

y verificando la etiqueta.

8 14 2

Direccin de memoria

principal

Etiqueta Lneas Palabra

11223344

24682468

13579246

77777777

11235813

FEDCBA98

12345678

13579246

11235813

FEDCBA98

11223344

12345678

00

16

16

FF

16

0000

0004

FFFC

FFF8

0000

0004

FFFC

339C

0000

0004

FFFC

FFF8

0000

0001

0CEF

3FFE

3FFF

Datos

Lnea + palabra

00

16

FF

Etiqueta

Etiqueta

Nmero

de lnea

Cach de 16 K lneas

8 bit

32 bits

32 bits

MP de 16 MB

Correspondencia Directa.

Ventajas:

Simple.

Poco costoso de implementar.

Desventaja:

Posicin fija para un bloque.

Si un programa accede a dos bloques, que les

corresponde una misma lnea de cach de forma

repetida se producirn varios fallos (miss) de cach.

Correspondencia Asociativa.

Un bloque de memoria principal puede ser

almacenado en cualquier lnea de la memoria

cache.

La direccin de memoria es interpretada como

una etiqueta (22 bits) y una palabra (2 bits).

La etiqueta identifica de forma nica el bloque

de memoria.

Cada etiqueta en cada lnea es examinada. La

bsqueda en el cach se vuelve cara.

Correspondencia asociativa estructura

de la direccin.

La etiqueta de 22 bits, se almacena con el

bloque de datos de 32 bits en cada lnea de la

memoria cach.

Se compara el campo etiqueta de la direccin,

con la etiqueta en el cach para encontrar un

acierto (hit) del cach.

2 22

Direccin de memoria

principal.

Etiqueta Palabra

13579246

FEDCBA98

33333333

11223344

24682468

11223344

FEDCBA98

33333333

13579246

24682468

3FFFFE

058CE7

3FFFFD

000000

3FFFFF

000000

000004

163398

16339C

1633A0

FFFCFF

FFFFF4

FFFFF8

Direccin Datos

0000

0001

3FFD

3FFE

3FFF

Datos Etiqueta

Nmero

de lnea

Cach de 16 K lneas

22bit

32 bits

32 bits

MP de 16 MB

Correspondencia asociativa.

Ventaja:

La flexibilidad.

Desventaja:

La complejidad de la implementacin.

El costo.

Correspondencia asociativa por

conjunto.

El cach es dividido en un nmero de

conjuntos.

Cada conjunto tiene un nmero fijo de lneas

de cach.

Un bloque puede ser asignado en cualquiera

de las lneas del conjunto, pero le corresponde

un solo conjunto.

Correspondencia asociativa por conjunto

Estructura de la direccin.

Usar el campo de conjunto para determinar el

conjunto de cach, en el cual hay que buscar.

Comparar el campo etiqueta para encontrar un

acierto (hit) del cach.

9 13 2

Direccin de memoria

principal

Etiqueta Lneas Palabra

11223344

24682468

13579246

77777777

11235813

FEDCBA98

12345678

13579246

11235813

FEDCBA98

11223344

12345678

000

02C

02C

1FF

02C

0000

0004

FFFC

FFF8

0000

0004

FFFC

339C

0000

0004

FFFC

FFF8

0000

0001

0CEF

3FFE

3FFF

Datos

000

02C

1FF

Etiqueta

Etiqueta

Nmero de

conjunto

Cach de 16 K lneas

8 bit

32 bits

32 bits

Direccin Datos

77777777

24682468

02C

1FF

8 bit

32 bits

Datos Etiqueta

Polticas de reemplazo algoritmos de

sustitucin.

Aleatoria:

Se escoge un bloque al azar.

First in first out (FIFO). El primero en tratar es el primero en

salir.

Reemplazar el bloque que ha estado en cach por mas tiempo.

Least Recently used (LRU) menos recientemente usado.

Se sustituye el bloque que hace mas tiempo que no ha sido

referenciado.

Least frequently used (LFU) menos frecuentemente usado.

Se sustituye aquel bloque que ha experimentado menos

referencias.

Poltica de escritura.

No se debe reemplazar una lnea de cach al

menos que la memoria principal ya haya sido

actualizada.

Mltiples CPUs tienen cachs individuales.

Los dispositivos de I/O acceden a memoria

principal directamente.

Escritura inmediata.

Todas las escrituras van a la memoria principal

y al cach.

Cuando se tienen varios CPUs, estos pueden

monitorizar el trfico a memoria principal para

tener el contenido de su cach actualizado.

El problema es el trfico.

Post-escritura.

Las actualizaciones se hacen inicialmente solo

en el cach.

Cuando se hace una actualizacin se activa el

bit ACTUALIZAR asociado a la lnea.

El bloque del cach que se va a sustituir es

escrito en memoria principal solo si tiene el

bit ACTUALIZAR activo.

Muchas Gracias.!!!!!!

Feliz Inicio de Semana..!!!!!!

You might also like

- Nicomar Propc 1000Document1 pageNicomar Propc 1000José Luis Gualotuña P.0% (1)

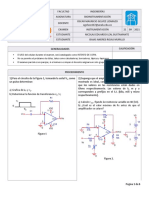

- Examen 02 InstrumentaciónDocument6 pagesExamen 02 InstrumentaciónDario CaphistNo ratings yet

- Subsistemas de Un SatéliteDocument6 pagesSubsistemas de Un SatéliteDenisse MontzeeNo ratings yet

- Practica 6 Antena Parabolica Alimentada Con Un Dipolo de Media Longitud de OndaDocument5 pagesPractica 6 Antena Parabolica Alimentada Con Un Dipolo de Media Longitud de OndaGabriel MartinezNo ratings yet

- DOC268 003 ES A VX680 Installation GuideDocument58 pagesDOC268 003 ES A VX680 Installation GuideE Moy Landa100% (1)

- Electronica en La ActualidadDocument7 pagesElectronica en La ActualidadSebastian MorquechoNo ratings yet

- TroceadoresDocument39 pagesTroceadoresRicardo Odracir100% (6)

- RECTIFICADORDocument5 pagesRECTIFICADORceleste claroNo ratings yet

- Informe Numero 3 - Electronica 1Document6 pagesInforme Numero 3 - Electronica 1Erlyn J. MenjivarNo ratings yet

- TDMy FDMDocument18 pagesTDMy FDMAlain Dorado ArceNo ratings yet

- Catálogo de Productos Jaibita ElectrónicaDocument52 pagesCatálogo de Productos Jaibita ElectrónicaReymondMtzNo ratings yet

- HardwareDocument5 pagesHardwareCin_BambiNo ratings yet

- Ejemplos Manejo de Interrupciones Múltiples - TMR0Document5 pagesEjemplos Manejo de Interrupciones Múltiples - TMR0scorpio19No ratings yet

- Lista Precios-Horacio Herrera-03822 15362285Document92 pagesLista Precios-Horacio Herrera-03822 15362285Dalton HerreraNo ratings yet

- Elt 3890 Automatica I Laboratorio No. 6 Programación de PLC S s7-300 SiemensDocument13 pagesElt 3890 Automatica I Laboratorio No. 6 Programación de PLC S s7-300 SiemensCesar Enrique Rivera BermudezNo ratings yet

- Electrónica Aplicada II - TulicDocument290 pagesElectrónica Aplicada II - Tulicveron31No ratings yet

- Donacion Microfono-Cabina-Impresora 26-12-19Document2 pagesDonacion Microfono-Cabina-Impresora 26-12-19fanyNo ratings yet

- Electronica de PotenciaDocument3 pagesElectronica de PotenciaPaulNo ratings yet

- Microsoft Word - TALLER ELECTRONICA ANALOGA 0301 PDFDocument6 pagesMicrosoft Word - TALLER ELECTRONICA ANALOGA 0301 PDFJhorlin Alvear roaNo ratings yet

- Programa EUCDocument9 pagesPrograma EUCAriel AlbanoNo ratings yet

- Reporte 4Document6 pagesReporte 4Intervita ConsultoriosNo ratings yet

- Informe 5 ADocument12 pagesInforme 5 AAnonymous 5OI0ClBZNo ratings yet

- Análisis de NecesidadesDocument3 pagesAnálisis de NecesidadesCarlos Enrique LopezNo ratings yet

- PR Ctica 2 Circuitos El Ctricos 2 Amplificadores Operacionales PDFDocument4 pagesPR Ctica 2 Circuitos El Ctricos 2 Amplificadores Operacionales PDFMiguel Antonio OrellanaNo ratings yet

- TEMA 7 Osciladores y Circuitos TemporizadoresDocument30 pagesTEMA 7 Osciladores y Circuitos TemporizadoresFrancisco Wilson Bezerra FranciscoNo ratings yet

- Seguridad de La Información Parcial Corte 2 Miguel BeltranDocument6 pagesSeguridad de La Información Parcial Corte 2 Miguel BeltranMiguel BeltránNo ratings yet

- Transmision Digital PAM, PDM, PPM, PCM y Con PortadoraDocument20 pagesTransmision Digital PAM, PDM, PPM, PCM y Con PortadoraLuis Alva FuertesNo ratings yet

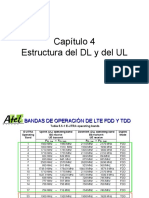

- Capitulo 4 - Estrucura Del DL ULDocument14 pagesCapitulo 4 - Estrucura Del DL ULkats1703No ratings yet

- Discador Telefonico QuasarDocument14 pagesDiscador Telefonico QuasarAlberto AlejandroNo ratings yet

- K-Seminario Ba-5 PDFDocument67 pagesK-Seminario Ba-5 PDFk470rNo ratings yet