Advanced Microprocessors &

Peripherals

Sarju S

Department of Computer Science and

Engineering

�Module I

Study of Interfacing ICs - 8255, 8251,

8279

�8255 Programmable Peripheral Interface(PPI)

1/25/17

�8255 Programmable Peripheral Interface

Widely used, programmable , Parallel I/O

Device

It is flexible, versatile, and economical

It can be used with almost any

microprocessor

4

1/25/17

�8255 Programmable Peripheral Interface

Pin Details

1/25/17

�8255 Programmable Peripheral Interface

24 I/O pins

Grouped into two 8-bit parallel ports(A,B)

Remaining 8-bit as port C

UPPER,

Control Word in Control Register

LOWER

www.lectnote.blogspot.com

Used as individual bits or 4-bits(C

Figure 1.1

1/25/17

�8255 Programmable Peripheral Interface

Modes

Bit Set/Reset(BSR) Mode

Set/Reset bits in Port C

I/O Mode

Mode 0

Mode 1(Handshake mode)

Mode 2

1/25/17

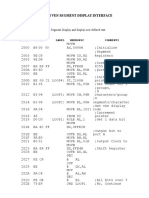

�Block Diagram

8255 Programmable Peripheral Interface

1/25/17

�8255 Programmable Peripheral Interface

Control Logic

RD(Read)

Reads data from I/O Port of 8255 to Microprocessor

WR(Write)

MPU writes into a selected I/O Port or Control

Register

RESET(Reset)

Clears the Control Register&Sets all ports in input

mode

CS, A0, A1

Device select Signals

1/25/17

�8255 Programmable Peripheral Interface

Control Logic Contd

CS signal is the master Chip Select

A0 and A1 specify one of the two I/O Ports

10

CS

A1

A0

Selected

Port A

Port B

Port C

Control

Register

8255 is not

selected

1/25/17

�8255 Programmable Peripheral Interface

Control Word

Contents of Control Register :- Control Word

This register is used to write control word when

A1 & A0 at logic 1

Not accessible for a read operation

D7

D6

D5

D4

D3

D2

D1

D0

Bit D7 specifies either I/O function or BSR

function

D7=1, bits D6-D0 determine I/O functions

D7=0, Port C operates in BSR mode

11

1/25/17

�8255 Programmable Peripheral Interface

Control Word contd.

To communicate with peripherals through

8255

Determine the addresses of Ports A,B and C

and of control register according to the chip

select logic and address lines A0 and A1

Write a control word in the control register

Write I/O instructions to communicate with

peripherals through ports A,B and C

12

1/25/17

�8255 Programmable Peripheral Interface

13

1/25/17

�8255 Programmable Peripheral Interface

Control Word

Control Word

D7 D6 D5 D4 D3 D2 D1 D0

0/1

BSR Mode

(Bit Set/Reset)

I/O Mode

Mode 0

Mode 1

Simple I/O

for ports A,B

and C

Handshake I/O

for ports A and or

B

Port C bits are

used for

handshake

14

Mode 2

Bidirectional data

bus for Port A

Port B: either in

Mode 0 or 1

Port C bits are used

for handshake

1/25/17

�8255 Programmable Peripheral Interface

Modes of operation

I/O Mode

Mode 0: Simple Input or Output

Ports A and B are used as Simple I/O Ports

Port C as two 4-bit ports

Features

Outputs are latched

Inputs are not latched

Ports do not have handshake or interrupt

capability

15

1/25/17

�8255 Programmable Peripheral Interface

Modes of operation

I/O Mode

Mode 1: Input or Output with Handshake

Handshake signals are exchanged between MPU &

Peripherals

Features

Ports

A and B are used as Simple I/O Ports

Each port uses 3 lines from Port C as handshake

signals

Input & Output data are latched

interrupt logic supported

16

1/25/17

�8255 Programmable Peripheral Interface

Modes of operation

I/O Mode

Mode 2: Bidirectional Data Transfer

Used primarily in applications such as data transfer

between two computers

Features

Ports

A can be configured as the bidirectional Port

Port B in Mode 0 or Mode 1.

Port A uses 5 Signals from Port C as handshake

signals for data transfer

Remaining 3 Signals from Port C Used as Simple I/O

or handshake for Port B

17

1/25/17

�8255 Programmable Peripheral Interface

Modes of operation

BSR(Bit Set/Reset) Mode

Concerned only with the 8-bits of Port C.

Set or Reset by control word

Ports A and B are not affected

18

1/25/17

�Serial Data Communication

Serial Data Format

The serial data format includes

one start bit,

five or eight data bits,

one stop bit.

A parity bit and an additional stop bit

might be included in the format as well.

19

1/25/17

�Methods of Data Communication

Modes of data transmission

Simplex

Data is transmitted only in one direction over

a single communication channel.

Duplex

Data may be transferred between two

transivers in both directions simultaneously.

Half Duplex

Data transmission may take place in either

direction, but at a time data may be

transmitted only in one direction

20

1/25/17

�8251 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS RECEIVER

TRANSMITTER (USART)

21

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Programmable chip designed for

synchronous and asynchronous data

transmission

28 pin DIP

Coverts the parallel data into a serial

stream of bits suitable for serial

transmission.

Receives a serial stream of bits and convert

it into parallel data bytes to be read by a

microprocessor.

22

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Block Diagram

23

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Five Sections

Read/Write Control Logic

Interfaces the chip with MPU

Determine the functions according to the control word

Monitors data flow

Transmitter

Converts parallel word received from MPU into serial bits

Transmits serial bits over TXD line to a peripheral.

Receiver

Receives serial bits from peripheral

Converts serial bits into parallel word

Transfers the parallel word to the MPU

Data Bus Buffer

Modem Controller

Used to establish data communication modems over

24

telephone line

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Read/Write Control Logic and Registers

This section includes

R/W Control Logic

Six input signals

Three buffer registers

Data register

Control Register

Status Register

25

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Input Signals

CS Chip Select

When this signal goes low, 8251 is selected

by MPU for communication

C/D Control/Data

When this signal is high, the control register

or status register is addressed

When it is low, the data buffer is addressed

Control and Status register is differentiated

by WR and RD signals, respectively

26

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

WR Write

Either writes in the control register or sends

outputs to the data buffer.

This connected to IOW or MEMW

RD Read

Either reads a status from status register or

accepts data from the data buffer

This is connected to either IOR or MEMR

RESET - Reset

CLK - Clock

Connected to system clock

Necessary for communication with microprocessor.

27

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

28

CS

C/D

RD

WR

Function

MPU writes instruction in the control

register

MPU reads status from the status

register

MPU outputs the data to the Data

Buffer

MPU accepts data from the Data Buffer

USART is not Selected

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Control Register

16-bit register

First byte is called mode instruction

Second byte is called command instruction

This register can be accessed an output port

when the C/D pin is high

Status Register

Checks ready status of a peripheral

Data Buffer

29

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Expanded Block Diagram of Transmitter and Receiver Section

30

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Transmitter Section

Accepts parallel data and converts it into

serial data

Two registers

Buffer Register

To hold eight bits

Output Register

Converts eight bits into a stream of serial bits

Transmits data on TxD pin with appropriate

framing bits(Start and Stop)

31

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Signals Associated with Transmitter Section

TxD Transmit Data

Serial bits are transmitted on this line

TxC Transmitter Clock

Controls the rate at which bits are transmitted

TxRDY Transmitter Ready

When it is high, it indicates that buffer register is empty

Can be used either to interrupt the MPU or indicate the status

This signal is reset when a data byte is loaded into the buffer

TxE Transmitter Empty

Logic 1 on this line indicate that the output register is empty

This signal is reset when byte is transferred from buffer to the

output registers

32

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Receiver Section

Accepts serial data from peripheral and

converts it into parallel data

The section has two registers

Input Register

Buffer Register

33

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Signals Associated with Receiver Section

RxD Receive Data

Bits are received serially on this line and

converted into parallel byte in the receiver

input

RxC Receiver Clock

RxRDY Receiver Ready

It goes high when the USART has a character

in the buffer register and is ready to transfer

it to the MPU

34

1/25/17

�8251 UNIVERSAL SYNCHRONOUS

ASYNCHRONOUS RECEIVER TRANSMITTER

Signals Associated with Modem Control

DSR- Data Set Ready

General purpose one bit inverting input port

Normally used to check if the Data Set is ready when

communicating with a modem

DTR Data Terminal Ready

device is ready to accept data when the 8251 is

communicating with a modem.

RTS Request to send Data

the receiver is ready to receive a data byte from modem

CTS Clear to Send

35

1/25/17

�8279 Programmable Keyboard/Display Interface

36

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

The keyboard display controller chip 8279

provides:

a set of four scan lines and eight return

lines for interfacing keyboards

A set of eight output lines for interfacing

display.

37

1/25/17

�38

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

I/O Control

The I/O control section controls the flow of

data to/from the 8279

Data Buffers

The data buffers interface the external bus of

the system with internal bus of 8279.

The I/O section is enabled only if CS is low.

The pins A0,RD and WR select the

command, status or data read/write

operations carried out by the CPU with

8279.

39

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

Control and Timing Register and Timing

Control

These registers store the keyboard and

display modes and other operating

conditions programmed by CPU

The Timing and control unit controls the

40

basic timings for the operation of the

circuit.

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

Scan Counter

has two modes to scan the key matrix and refresh the

display

Encoded Mode

the counter provides binary count that is to be

externally decoded to provide the scan lines for

keyboard and display

Decoded Mode

the counter internally decodes the least significant 2

bits and provides a decoded 1 out of 4 scan on SL0-SL3

The keyboard and display both are in the same mode

at a time.

41

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

Return Buffers and Keyboard Debounce

and Control

Scans for a key closure row wise

The code of key is directly transferred to the

sensor RAM along with SHIFT and CONTROL key

status.

FIFO/Sensor RAM and Status Logic

8-byte first-in-first -out (FIFO) RAM

Each key code of the pressed key is entered in the

order of the entry

The status logic generates an interrupt after each

FIFO read operation till the FIFO is empty

42

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

Display Address Registers and Display

RAM

holds the address of the word currently being

written or read by the CPU to or from the

display RAM

The contents of the register are

automatically updated by 8279

43

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

44

Modes of Operation of 8279

The modes of operation of 8279 are as

follows :

1. Input (Keyboard) modes.

2. Output (Display) modes.

Input ( Keyboard ) Modes : 8279 provides

three input modes. These modes are as

follows:

1. Scanned Keyboard Mode

2. Scanned Sensor Matrix

3. Strobed input

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

Scanned Keyboard Mode

This mode allows a key matrix to be

interfaced using either encoded or decoded

scans

In encoded scan, an 8*8 keyboard or in

decoded scan, a 4*8 keyboard can be

interfaced

The code of key pressed with SHIFT and

CONTROL status is stored into the FIFO

RAM.

45

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

Scanned Sensor Matrix

In this mode, a sensor array can be interfaced

with 8279 using either encoded or decoded scans

With encoded scan 8*8 sensor matrix or with

decoded scan 4*8 sensor matrix can be

interfaced

The sensor codes are stored in the CPU

addressable sensor RAM

Strobed input

if the control lines goes low, the data on return

lines, is stored in the FIFO byte by byte

46

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

Output (Display) Modes : 8279 provides two

output modes for selecting the display options

Display Scan

In this mode 8279 provides 8 or 16 character

multiplexed displays those can be organized as

dual 4- bit or single 8-bit display units.

Display Entry : ( right entry or left entry mode )

8279 allows options for data entry on the

displays. The display data is entered for display

either from the right side or from the left side.

47

1/25/17

�8279 PROGRAMMABLE KEYBOARD/DISPLAY

INTERFACE

Keyboard Modes

Scanned Keyboard mode with 2 Key

Lockout

Scanned Keyboard with N-Key Rollover

Scanned keyboard special error mode

Sensor matrix mode

Display Modes

Left Entry mode(Type writer mode)

Right Entry mode(Calculator mode)

48

1/25/17

�Module II

Interfacing with 8085 - Interfacing keyboard

Hardware and Software approach

Interfacing seven segment displays Interfacing D/A and A/D converters - Micro

controllers

�Scanned Keyboard mode with 2 Key Lockout

50

1/25/17

�51

1/25/17

�Interfacing Matrix keyboard

Steps

Ground all the rows by sending logic 0

through the output port

Check the columns by reading the input port.

If no key is pressed , all columns remains

high.

When one key is pressed, corresponding

52

column goes low; identify and decode the

key.

1/25/17

�Program

Check whether all keys are open

Necessary to avoid misinterpretation if a key is

held for a long time

Check a key closure

D3-D0 should be 1111

Identify the key

Complex procedure

Grounding one row at a time and checking each

column for zero

Find the binary key code for the key

Counter Procedure

For 5 Rows counter is incremented from 0 to 13H

53

1/25/17

�Interfacing Key Board Hardware Approach

54

1/25/17

�Interfacing circuit of a six seven- segment LED

display using the technique of multiplexing.

55

1/25/17

�4x4 MATRIX KEYBOARD & 4 DIGIT 7 SEGMENT DISPLAY

INTERFACE

56

1/25/17

�FLOWCHARTS

Source Program and Interrupt Service Routine

57

1/25/17

�Source program:

MVI A, 00H : Initialize keyboard/display in

encoded

OUT 81H : scan keyboard 2 key lockout mode

MVI A, 34H

OUT 81H : Initialize prescaler count

MVI A, 0BH : Load mask pattern to enable RST

7.5

SIM : mask other interrupts

EI

: Enable Interrupt

HERE: JMP HERE : Wait for the interrupt

58

1/25/17

�Interrupt service routine

MVI A, 40H : Initialize 8279 in read FIFO RAM

mode

OUT 81H

IN 80H : Get keycode

MVI H, 62H : Initialize memory pointer to point

MOV L, A : 7-Segment code

MVI A, 80H : Initialize 8279 in write display RAM

mode

OUT 81H

MOV A, M : Get the 7 segment code

OUT 80H : Write 7-segment code in display RAM

EI : Enable interrupt

RET : Return to main program

59

1/25/17

�Digital-To-Analog(D/A) Converters

60

1/25/17

�Interfacing AD558 with 8085

61

1/25/17

�Interfacing a 10-bit D/A

Converter

In many D/A converter application 10-bit or

62

12-bit is required.

The 8-bit microprocessor has only 8-bit

data lines.

To transfer 10-bits, the data bus is timeshared by using two output ports: one for

first 8-bit and second for remaining two

bits.

AD7522 is a CMOS 10-bit D/A converter

with an input buffer and a holding register.

The ten bits are loaded into the input

register in two steps using two output

1/25/17

�Interfacing a 10-bit D/A

Converter

The low-order eight bits are loaded with the

control line LBS and the remaining two bits

are loaded with HBS.

Then all ten bits are switched into a holding

register for conversion by enabling the line

LDAC.

63

1/25/17

�Interfacing a 10-bit D/A

Converter

64

1/25/17

�Analog-To-Digital(A/D)

converter

65

1/25/17

�Interfacing 8-bit A/D

Converters

66

1/25/17

�Interfacing 8-bit A/D

Converters

A pulse to START pin begins the conversion

67

process and disables the tri-state output

buffer.

At the end of the conversion period DATA

READY becomes active and the digital

output is made available at the out put

buffer.

To interface an A/D converter with the

microprocessor, the microprocessor should

1. Send a pulse to START pin. This can be

derived from a control signal such as

Write(WR).

1/25/17

�Interfacing 8-bit A/D

Converters

2. Wait until the end of conversion. The end

of conversion period can be verified either

by status checking(Polling) or by interrupt.

3. Read the digital signal at an input port.

68

1/25/17

�69

1/25/17