80% found this document useful (5 votes)

1K views63 pagesCAN Protocol

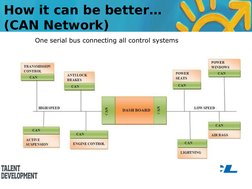

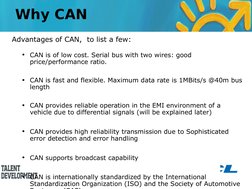

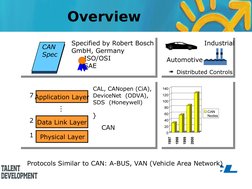

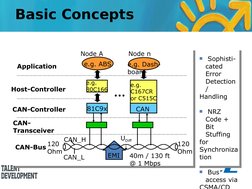

The document discusses the CAN (Controller Area Network) protocol. It covers CAN fundamentals, the physical layer, and data link layer. The physical layer uses differential signaling over two wires and supports bit rates up to 1Mbps for bus lengths of 40m. Error detection and handling is implemented at the data link layer to provide reliable transmission. CAN is used widely in automotive and industrial applications for distributed real-time control.

Uploaded by

Bijaya RanaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPTX, PDF, TXT or read online on Scribd

80% found this document useful (5 votes)

1K views63 pagesCAN Protocol

The document discusses the CAN (Controller Area Network) protocol. It covers CAN fundamentals, the physical layer, and data link layer. The physical layer uses differential signaling over two wires and supports bit rates up to 1Mbps for bus lengths of 40m. Error detection and handling is implemented at the data link layer to provide reliable transmission. CAN is used widely in automotive and industrial applications for distributed real-time control.

Uploaded by

Bijaya RanaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPTX, PDF, TXT or read online on Scribd

- Introduction to CAN Protocol

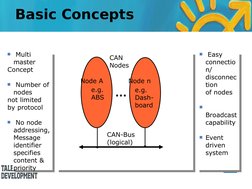

- Basic Concepts of CAN