Professional Documents

Culture Documents

VHDL

Uploaded by

Faby ReveloCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

VHDL

Uploaded by

Faby ReveloCopyright:

Available Formats

VHDL: Máquinas de estado

Máquinas de estado (FSM)

• Definición

Una máquina de estados finita (FSM) es un modelo usado para

diseñar circuitos lógicos secuenciales.

• Características

No puede estar en más de un estado por vez.

El estado en el que se encuentra se denomina estado actual.

El cambio de un estado a otro se denomina transición, y se

dispara con el reloj del circuito

Son muy útiles en el diseño de protocolos de comunicación.

Existen dos tipos de máquinas de estado: Moore y Mealy

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Estructura de una máquina de Moore

Las salidas dependen sólo del estado.

Estado actual

Lógica de Flip-Flops Lógica de Salidas

Entradas próximo estado de estado salida

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Estructura de una máquina de Mealy

Las salidas dependen del estado y de las entradas.

Estado actual

Lógica de Flip-Flops Lógica de Salidas

Entradas próximo estado de estado salida

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Codificación de estados

Existen diferentes tipos de codificación de estados

- Binaria

- One Hot

- Gray

- etc

La codificación de estados puede hacerse manualmente

o de manera automática

- En el mismo código de VHDL se pueden establecer

atributos que indican que tipo de codificación se quiere

- Se puede indicar a la herramienta de síntesis como

codificar los estados.

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Posibles codificaciones para 8 estados

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Mealy: Detector de “101”

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Mealy: Detector de “101”

Consiste en 3 pasos:

- Definición de los estados

- Descripción de los registros de estado

- Descripción de los bloques combinacionales de próximo

estado y de salida

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Mealy: Detector de “101”

Paso 1: Definición de los estados

architecture det_arq of detector is

type tipo_estado is (A, B, C);

signal estado_actual, estado_siguiente: tipo_estado;

begin

…

end;

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Mealy: Detector de “101”

Paso 2: Descripción de los registros de estado

registros: process(clk, rst)

begin

if rst = '1' then

estado_actual <= A;

elsif rising_edge(clk) then

estado_actual <= estado_siguiente;

end if;

end process;

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Mealy: Detector de “101”

Paso 3: Descripción de los bloques combinacionales de

próximo estado y de salida

transiciones: process(estado_actual, secuencia)

begin

case estado_actual is

when A =>

if secuencia = '1' then

estado_siguiente <= B;

det_flag <= '0';

else

estado_siguiente <= A;

det_flag <= '0';

end if;

…

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Mealy: Detector de “101”

...

when B =>

if secuencia = '1' then

estado_siguiente <= B;

det_flag <= '0';

else

estado_siguiente <= C;

det_flag <= '0';

end if;

...

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Mealy: Detector de “101”

...

when C =>

if secuencia = '1' then

estado_siguiente <= B;

det_flag <= '1';

else

estado_siguiente <= A;

det_flag <= ‘0';

end if;

end case;

end process;

end;

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Reporte de síntesis (ISE)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Reporte de síntesis (ISE)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Esquemático (ISE - RTL Schematic)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Esquemático (ISE - RTL Schematic)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Esquemático (ISE - Technology Schematic)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Mealy: Simulación (ISim)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Moore: Detector de “101”

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Moore: Detector de “101”

Consiste en 3 pasos:

- Definición de los estados

- Descripción de los registros de estado

- Descripción de los bloques combinacionales de próximo

estado y de salida

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Moore: Detector de “101”

Paso 1: Definición de los estados

architecture det_arq of detector is

type tipo_estado is (A, B1, B2, C);

signal estado_actual, estado_siguiente: tipo_estado;

begin

…

end;

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Moore: Detector de “101”

Paso 2: Descripción de los registros de estado

registros: process(clk, rst)

begin

if rst = '1' then

estado_actual <= A;

elsif rising_edge(clk) then

estado_actual <= estado_siguiente;

end if;

end process;

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Moore: Detector de “101”

Paso 3: Descripción de los bloques combinacionales de

próximo estado y de salida

transiciones: process(estado_actual, secuencia)

begin

case estado_actual is

when A =>

det_flag <= '0';

if secuencia = '1' then

estado_siguiente <= B1;

else

estado_siguiente <= A;

end if;

…

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Moore: Detector de “101”

...

when B1 =>

if secuencia = '1' then

estado_siguiente <= B1;

else

estado_siguiente <= C;

end if;

when B2 =>

if secuencia = '1' then

estado_siguiente <= B1;

else

estado_siguiente <= C;

end if;

...

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Moore: Detector de “101”

...

when C =>

if secuencia = '1' then

estado_siguiente <= B2;

else

estado_siguiente <= A;

end if;

end case;

end process;

det_flag <= '1' when estado_actual = B2 else '0';

end; -- fin de la arquitectura

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Reporte de síntesis de la máquina de Moore (ISE)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Reporte de síntesis de la máquina de Moore (ISE)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Esquemático de la máquina de Moore (ISE - RTL Schem)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Esquemático de la máquina de Moore (ISE - Tech Schem)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

Máquinas de estado (FSM)

• Diseño de una máquina de Moore: Simulación (ISim)

Sistemas Digitales - FIUBA 2do. Cuatrimestre de 2014

You might also like

- Escalas Valoración Adolescencia PDFDocument292 pagesEscalas Valoración Adolescencia PDFSires OchentayunoNo ratings yet

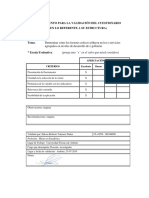

- Formulario. Validacion Estructura Cuestionario3Document1 pageFormulario. Validacion Estructura Cuestionario3Faby Revelo100% (1)

- Tema 2 - Corriente AlternaDocument28 pagesTema 2 - Corriente AlternaFaby ReveloNo ratings yet

- Re Cort AdoresDocument9 pagesRe Cort AdoresFaby ReveloNo ratings yet

- PoemaDocument1 pagePoemaFaby ReveloNo ratings yet

- PropagacionDocument7 pagesPropagacionFaby ReveloNo ratings yet

- MayasDocument3 pagesMayasFaby ReveloNo ratings yet

- Formulario. Validacion Estructura Cuestionario3Document1 pageFormulario. Validacion Estructura Cuestionario3Faby Revelo100% (1)

- Circuitos - Franco Vial GonzálezDocument83 pagesCircuitos - Franco Vial GonzálezJhon Sarmiento FirenzeNo ratings yet

- AMORTIZACIONDocument9 pagesAMORTIZACIONFaby ReveloNo ratings yet

- Tema 2 - Corriente AlternaDocument115 pagesTema 2 - Corriente AlternaFaby Revelo100% (1)

- Tema 2 - Corriente AlternaDocument28 pagesTema 2 - Corriente AlternaFaby ReveloNo ratings yet

- Laptop Guía de Reparación Completa - Garry Romaneo PDFDocument104 pagesLaptop Guía de Reparación Completa - Garry Romaneo PDFFaby Revelo100% (1)

- Diapositivas Redes InalambricasDocument12 pagesDiapositivas Redes InalambricasFaby ReveloNo ratings yet

- ¿Por Qué No Logro Ser Asertivo (7a. Ed.)Document234 pages¿Por Qué No Logro Ser Asertivo (7a. Ed.)Lilia Palos96% (23)

- Trabajo Estadistica Inferencial Aplicada - Prueba de HipotesisDocument15 pagesTrabajo Estadistica Inferencial Aplicada - Prueba de HipotesisFaby ReveloNo ratings yet

- Universidad Tecnica de AmbatoDocument10 pagesUniversidad Tecnica de AmbatoFaby ReveloNo ratings yet

- Microcontroladores PIC (José M Angulo Usategui, Ignacio Angulo Martínez)Document244 pagesMicrocontroladores PIC (José M Angulo Usategui, Ignacio Angulo Martínez)aloso1982100% (1)

- Matematica III " Sucesiones, Series Criterios de Convergencia y Divergencia, Serie de Potencia, Taylor y Maclaurin "Document8 pagesMatematica III " Sucesiones, Series Criterios de Convergencia y Divergencia, Serie de Potencia, Taylor y Maclaurin "Willmer Alfonso Uzcategui Rivas100% (10)

- Desplazador de NombreDocument2 pagesDesplazador de NombreFaby ReveloNo ratings yet

- Vocabulary Improvement PlanDocument16 pagesVocabulary Improvement PlanFaby ReveloNo ratings yet

- Tecnologías InalámbricasDocument5 pagesTecnologías InalámbricasFaby ReveloNo ratings yet

- Banda Ancha DSLDocument31 pagesBanda Ancha DSLFaby ReveloNo ratings yet

- Deber EstadisticaDocument20 pagesDeber EstadisticaFaby ReveloNo ratings yet

- Prblemas de ConexionDocument12 pagesPrblemas de ConexionFaby ReveloNo ratings yet

- Tema 2 - Corriente AlternaDocument115 pagesTema 2 - Corriente AlternaFaby Revelo100% (1)

- Deber Semana 10Document11 pagesDeber Semana 10Faby ReveloNo ratings yet

- Iso 9000Document8 pagesIso 9000Faby ReveloNo ratings yet

- Redes de ComunicacionDocument16 pagesRedes de ComunicacionFaby ReveloNo ratings yet

- Introducción a la Programación - Asistencia y notasDocument21 pagesIntroducción a la Programación - Asistencia y notasPedroNo ratings yet

- Algoritmos GeneticosDocument263 pagesAlgoritmos Geneticosjuvenal100% (1)

- Comandos MongoDBDocument7 pagesComandos MongoDBalexis torresNo ratings yet

- Tarea 2 - Optimizacion (Varias Variable) - 3AM2Document6 pagesTarea 2 - Optimizacion (Varias Variable) - 3AM2Rebeca MoralesNo ratings yet

- Curso Machine Learning 12h para GeólogosDocument2 pagesCurso Machine Learning 12h para GeólogosLuis Fernando ParedesNo ratings yet

- Ucsm - Notas Io1 20162Document4 pagesUcsm - Notas Io1 20162Javier Cari EspinozaNo ratings yet

- Examen parcial de producciónDocument16 pagesExamen parcial de producciónjuanesrm100% (1)

- Metodo NewtonDocument8 pagesMetodo Newtonanon_912754No ratings yet

- Clase 5. Modelos Dinamicos de Inventario 1Document38 pagesClase 5. Modelos Dinamicos de Inventario 1Sofía MartínezNo ratings yet

- Expresiones Algebraicas - IngresoDocument3 pagesExpresiones Algebraicas - IngresoJosefina RodriguezNo ratings yet

- Solución de problemas de correlación en saludDocument8 pagesSolución de problemas de correlación en saludCamilo SanabriaNo ratings yet

- Resumen Ejecutivo de Cadenas de MarcovDocument3 pagesResumen Ejecutivo de Cadenas de MarcovJosua MendezNo ratings yet

- S2-Derivada Parcial-DireccionalDocument59 pagesS2-Derivada Parcial-DireccionalJEAN CARLOS BLAS ALVARADONo ratings yet

- Algoritmos Con RecursividadDocument10 pagesAlgoritmos Con RecursividadCarlos del CampoNo ratings yet

- Exposicion 1 Probabilidad BinomialDocument25 pagesExposicion 1 Probabilidad BinomialMary PerlecheNo ratings yet

- Diagrama de Flujo - Paso A PasoDocument9 pagesDiagrama de Flujo - Paso A PasoGuillermo Franco MalosevichNo ratings yet

- Métodos numéricos: Valores y vectores propiosDocument29 pagesMétodos numéricos: Valores y vectores propiosKattya Enciso QuispeNo ratings yet

- 100000M02C DinamicaDeFluidosComputacionalDocument6 pages100000M02C DinamicaDeFluidosComputacionalAlex ChuquijaNo ratings yet

- Ejercicios - Métodos Abiertos - ExcelDocument16 pagesEjercicios - Métodos Abiertos - ExcelGILENY SILVA LEALNo ratings yet

- PROGRAMACIÓN LINEAL Y MODELOS DE INVESTIGACIÓN DE OPERACIONESDocument10 pagesPROGRAMACIÓN LINEAL Y MODELOS DE INVESTIGACIÓN DE OPERACIONESFabian Andres Diaz MalpikNo ratings yet

- Reporte - Ecuaciones Diferenciales - Fracciones Parciales .Saul HTDocument4 pagesReporte - Ecuaciones Diferenciales - Fracciones Parciales .Saul HTEdgarNo ratings yet

- Artiga Daniela AlgoritmosSelectivosDocument14 pagesArtiga Daniela AlgoritmosSelectivosDaniela ArtigaNo ratings yet

- Calculo de Flujo de PotenciaDocument26 pagesCalculo de Flujo de PotenciaRazi SanchezNo ratings yet

- Final Estadistica 23102016Document4 pagesFinal Estadistica 23102016AlcidesSosa75% (4)

- Que Es La Programacion EnteraDocument4 pagesQue Es La Programacion EnteraKike MoralesNo ratings yet

- Parcial de Ingles TecnicoDocument2 pagesParcial de Ingles TecnicoMarcioSantosNo ratings yet

- Modelos y Analisis AmbientalesDocument8 pagesModelos y Analisis AmbientalesValeria PeredaNo ratings yet

- Unidad III, 4 Problemas - Salvatierra - HuamaniDocument10 pagesUnidad III, 4 Problemas - Salvatierra - HuamaniDAVID BRAYAN SALVATIERRA HUAMANINo ratings yet

- A - Ejemplos InterpolacionDocument22 pagesA - Ejemplos InterpolacionKatherine Zumiko Cadillo BaltazarNo ratings yet