0% found this document useful (0 votes)

153 views41 pagesDigital System Design

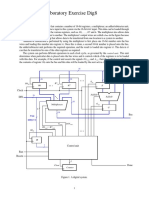

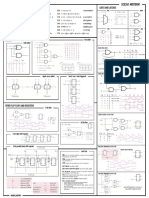

This document describes the implementation of a bus structure using tri-state drivers or multiplexers to connect registers. It provides Verilog code for a register swap module that uses a finite state machine (FSM) and tri-state drivers or multiplexers to swap the contents of three registers (R1, R2, R3) through a common bus. The code defines the FSM states and control signals, instantiates register modules, and specifies the bus wiring based on the FSM state using tri-state drivers or multiplexers.

Uploaded by

Mohit VermaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPTX, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

153 views41 pagesDigital System Design

This document describes the implementation of a bus structure using tri-state drivers or multiplexers to connect registers. It provides Verilog code for a register swap module that uses a finite state machine (FSM) and tri-state drivers or multiplexers to swap the contents of three registers (R1, R2, R3) through a common bus. The code defines the FSM states and control signals, instantiates register modules, and specifies the bus wiring based on the FSM state using tri-state drivers or multiplexers.

Uploaded by

Mohit VermaCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPTX, PDF, TXT or read online on Scribd