0% found this document useful (0 votes)

151 views25 pagesVerilog Combinational Logic Tutorial

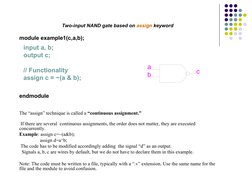

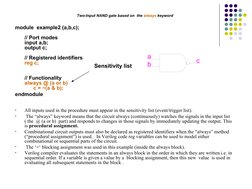

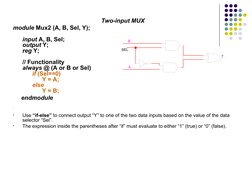

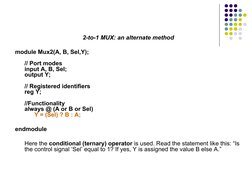

This document provides examples of Verilog code for combinational and sequential logic circuits such as NAND gates, multiplexers, and D flip-flops. It demonstrates the use of continuous assignments with "assign" and procedural assignments with "always" blocks. Blocking and non-blocking assignments as well as case statements are also illustrated. The examples serve as an introduction to basic Verilog concepts for modeling digital logic.

Uploaded by

EurusCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

0% found this document useful (0 votes)

151 views25 pagesVerilog Combinational Logic Tutorial

This document provides examples of Verilog code for combinational and sequential logic circuits such as NAND gates, multiplexers, and D flip-flops. It demonstrates the use of continuous assignments with "assign" and procedural assignments with "always" blocks. Blocking and non-blocking assignments as well as case statements are also illustrated. The examples serve as an introduction to basic Verilog concepts for modeling digital logic.

Uploaded by

EurusCopyright

© © All Rights Reserved

We take content rights seriously. If you suspect this is your content, claim it here.

Available Formats

Download as PPT, PDF, TXT or read online on Scribd

![4-to-1 Multiplexor

module Mux4 (Data, Sel, Y);

//Port modes

input [3:0] Data;

input [1:0] Sel;

output Y;

reg Y;

a](https://screenshots.scribd.com/Scribd/252_100_85/189/521758667/8.jpeg)

![Four-Input MUX: an alternate method

module Mux4 (Data, Sel, Y);

//Port modes

input [3:0] Data;

input [1:0] Sel;

output Y;](https://screenshots.scribd.com/Scribd/252_100_85/189/521758667/9.jpeg)

![4-to1 MUX

module Mux16 (Data, Sel, Y);

parameter DataWidth = 16;

input [DataWidth-1:0] Data;

input [3:0] Sel;

outpu](https://screenshots.scribd.com/Scribd/252_100_85/189/521758667/10.jpeg)