Professional Documents

Culture Documents

Reduction

Uploaded by

Amin NadafOriginal Description:

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Reduction

Uploaded by

Amin NadafCopyright:

Available Formats

CSIS 3510 Computer Organization and Architecture

Topics covered in this lecture: Review of DeMorgans Theorem Using DeMorgans Theorem Building a 2-bit decoder Algebraic Reduction of Boolean Expressions 7-segment decoder

DeMorgans Theorem On of the most useful principles in boolean algebra is DeMorgans Theorem, which allows one to switch between ANDs and NORs and ORs and NANDs. Remember, we want to design circuits using AND and OR, but then implement them using NAND and NOR (AND transistor bleedthrough problem, and manufacturing layering minimization) NOT terms or Inverted terms are represented with a line over the terms

AB = A + B A + B = AB

We demonstrated the validity of DeMorgans by Perfect Induction, using a truth table.

Using DeMorgans Theorem To convert A+B into a form that can be implemented using a NAND gate follow these steps: 1. Double Complement the term A+B = A+B 2. Use DeMorgans to distribute one of the complements A+B = A B The equation is now a NAND of the complemented inputs. To convert AB into a form that can be implemented using a NOR gate follow these steps: 1. Double Complement the term AB = AB 2. Use DeMorgans to distribute one of the complements AB = A + B The equation is now a NOR of the complemented inputs.

Extracting a function from a truth table and converting A 0 0 1 1 B 0 1 0 1 Output 0 1 0 Out = A B 0 DoubleC A B DeM A+B Simplify A + B

Two-Bit Decoder A 0 0 1 1 B 0 1 0 1 F0 1 0 0 0 F1 0 1 0 0 F2 0 0 1 0 F3 0 0 0 1

F0 = A B = A B = A+B = A+B

F1 = A B = A B = A+B = A+B F2 = A B = A B = A+B = A+B F3 = A B = A B = A+B

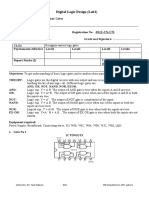

Two-Bit Decoder Diagram

A A B B

F0 F1 F2 F3

Algebraic Reduction of Boolean Functions Algebraic reduction is used to minimize a function extracted from a truth table or other source. Principle is to look for terms where a single variable is present in both complemented and positive form. Those variables can be deleted from those terms. Note: terms can be used over in multiple minimizations. Examples

A B + A B = B, AB+AB=A ABC+ABC=AB ABC+ABC+ABC+ABC AB AB A

7-Segment Display Decoder 7 Segment Display:

0 6 1

5

4 3

Displaying 0, 1, 2, 3

7-Segment Display Truth Table (Displaying values from 0-3 only)

AB 0 0 0 1 1 0 1 1

F0 1 0 1 1

F1 1 1 1 1

F2 1 1 0 1

F3 1 0 1 1

F4 1 0 1 0

F5 1 0 0 0

F6 0 0 1 1

Extracting and Minimizing Segment Functions

F0 = F1 =

F2 =

F3 = F4 = F5 = F6 =

Extracting and Minimizing Segment Functions

F0 = F1 =

F2 =

F3 = F4 = F5 = F6 =

Extracting and Minimizing Segment Functions

F0 = F1 =

F2 =

F3 = F4 = F5 = F6 =

7-Segment Display Decoder Diagram

Conclusion

Topics covered in this lecture: Review of DeMorgans Theorem Using DeMorgans Theorem Building a 2-bit decoder Algebraic Reduction 7-segment decoder Questions?

You might also like

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5795)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (588)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (400)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (838)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (345)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (121)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- DLD Lab 1Document5 pagesDLD Lab 1tm tigerNo ratings yet

- Week 04 Digital Design - 03 Gate Level Minimization 31032020 112339amDocument28 pagesWeek 04 Digital Design - 03 Gate Level Minimization 31032020 112339amKamran WahabNo ratings yet

- Lec-5 Basic Logic GatesDocument20 pagesLec-5 Basic Logic GatesManjare Hassin RaadNo ratings yet

- Logika Gerbang Nand DatasheetDocument4 pagesLogika Gerbang Nand DatasheetNur Indah ArifaniNo ratings yet

- Lecture4 Chapter3 - NAND and NOR ImplementationsDocument25 pagesLecture4 Chapter3 - NAND and NOR ImplementationsAhsan BilalNo ratings yet

- Experiment-1 Logic Gate II 1-1 Object:: Electrical Power Technical Engineering DeptDocument5 pagesExperiment-1 Logic Gate II 1-1 Object:: Electrical Power Technical Engineering DeptMohammed Dyhia AliNo ratings yet

- Topic 2 - Subtopic 2.2Document49 pagesTopic 2 - Subtopic 2.2Navinaash Chanthra SegaranNo ratings yet

- Dte Microproject Report FixedDocument13 pagesDte Microproject Report FixedYash TayadeNo ratings yet

- Answers To Selected Problems On Simplification of Boolean FunctionsDocument4 pagesAnswers To Selected Problems On Simplification of Boolean FunctionsAnushri PathakNo ratings yet

- NAND-NAND and NOR-NOR Implementations: ObjectivesDocument6 pagesNAND-NAND and NOR-NOR Implementations: Objectivesryle34No ratings yet

- Chapter One Number Systems and Codes: ObjectivesDocument35 pagesChapter One Number Systems and Codes: ObjectivesCarloNo ratings yet

- Logic Function and Booleans Algebra: George BooleDocument30 pagesLogic Function and Booleans Algebra: George BoolePrajwol sainjuNo ratings yet

- Comat BoxX Manual PDFDocument109 pagesComat BoxX Manual PDFAntonioBarrientosNo ratings yet

- Lab Report: Submitted ToDocument12 pagesLab Report: Submitted ToMd. Al Amin 201-15-3479No ratings yet

- LAB 3 IC DesignDocument6 pagesLAB 3 IC DesignShaifulIzuwanNo ratings yet

- All Gates Using Universal GatesDocument4 pagesAll Gates Using Universal GatesAli Raza KhanNo ratings yet

- Ringkasan Bab 3Document17 pagesRingkasan Bab 3MHD RasifNo ratings yet

- Boolean and GateDocument69 pagesBoolean and GatevsbistNo ratings yet

- Module-II Logic Gates & Logic FamiliesDocument143 pagesModule-II Logic Gates & Logic Familiesvamshi krishna veerakotiNo ratings yet

- Experiment No. 1: Aim of The ExperimentDocument10 pagesExperiment No. 1: Aim of The ExperimentRabindraMaharana50% (2)

- LAB-4 Analysis of Universal Gates ICs With Truth Tables and Implementation of The Digital CircuitsDocument11 pagesLAB-4 Analysis of Universal Gates ICs With Truth Tables and Implementation of The Digital CircuitsNaeem AtifNo ratings yet

- DLD Lab 2Document4 pagesDLD Lab 2گيدوڙو ماڇيNo ratings yet

- Digital Logic Design Lab Manual Fall 20 Semester Version 4Document78 pagesDigital Logic Design Lab Manual Fall 20 Semester Version 4Abdul HaseebNo ratings yet

- Cmosedu Com Jbaker Courses Ee421L f13 Students Wolvert9 LabDocument15 pagesCmosedu Com Jbaker Courses Ee421L f13 Students Wolvert9 LabPerumal NamasivayamNo ratings yet

- 7420 Datasheet PDFDocument4 pages7420 Datasheet PDFOMAR ALEJANDRO LONGORIA VAZQUEZNo ratings yet

- Innovative Switching & Control: The Internal Qualities CountDocument146 pagesInnovative Switching & Control: The Internal Qualities Countsido bNo ratings yet

- St. Xavier's College: Maitighar, KathmanduDocument9 pagesSt. Xavier's College: Maitighar, Kathmandukripal shresthaNo ratings yet

- Digital Logic Gates Lab 2Document13 pagesDigital Logic Gates Lab 2JordanNo ratings yet

- Low Power VLSI Circuits and Systems Prof. Ajit Pal Department of Computer Science and Engineering Indian Institute of Technology, KharagpurDocument23 pagesLow Power VLSI Circuits and Systems Prof. Ajit Pal Department of Computer Science and Engineering Indian Institute of Technology, KharagpurHimaja DasariNo ratings yet

- Digital Electronics PDFDocument135 pagesDigital Electronics PDFkrish100% (2)