Professional Documents

Culture Documents

Lowpower VLSI QP

Lowpower VLSI QP

Uploaded by

Vigneswaran VigneshOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Lowpower VLSI QP

Lowpower VLSI QP

Uploaded by

Vigneswaran VigneshCopyright:

Available Formats

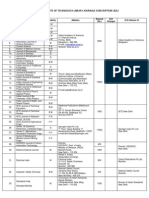

Code No: 54117/MT M.Tech.

I Semester Supplementary Examinations, September, 2008 LOW POWER VLSI DESIGN (Common to Digital Systems & Computer Electronics/ Wireless & Mobile Communication) Time: 3hours Answer any FIVE questions All questions carry equal marks --1.

NR

Max. Marks:60

Discuss about the limitations of various parameters and constraints with respect to low-power low-voltage design of circuits pertaining to VLSI. How graded drawn structures can be produced? Explain with necessary schematic diagrams. How isolation is achieved in B1 CMOS process? Explain. Give the device structure and describe the fabrication process of Low-voltage/Low-power lateral BJT on SOI. Describe the static characteristics MOS transistor with the help of necessary equations for current-voltage relations. Using necessary equations, explain about the Base-Emitter and Base-collector Depletion capacitances. Draw the circuit for conventional B1 CMOS, Two-input NAND gate and describe its characteristics. Give the comparative evaluation of all the B1 CMOS circuits employing lateral parasitic PnP BJTs. Explain about the Full-swing multi drain/multi collector complimenting B1 CMOS buffers. Explain about the need for Low-power latches and Flip-Flops in VLSI design. Explain about the: i) Optimization theme ii) Performance theme and iii) Pipelining theme of latches and Flip-Flops. Contd2

2.a) b) 3. 4.a) b) 5. 6.a) b) 7.a) b)

Code No: 54117/MT 8. Write a) b) c)

::2::

notes on any TWO: Sub-half Micron Devices Design perspectives of latches and Flip-Flops BSIM Model of MOSFET. *****

You might also like

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeFrom EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeRating: 4 out of 5 stars4/5 (5807)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreFrom EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreRating: 4 out of 5 stars4/5 (1091)

- Never Split the Difference: Negotiating As If Your Life Depended On ItFrom EverandNever Split the Difference: Negotiating As If Your Life Depended On ItRating: 4.5 out of 5 stars4.5/5 (842)

- Grit: The Power of Passion and PerseveranceFrom EverandGrit: The Power of Passion and PerseveranceRating: 4 out of 5 stars4/5 (590)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceFrom EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceRating: 4 out of 5 stars4/5 (897)

- Shoe Dog: A Memoir by the Creator of NikeFrom EverandShoe Dog: A Memoir by the Creator of NikeRating: 4.5 out of 5 stars4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersFrom EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersRating: 4.5 out of 5 stars4.5/5 (346)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureFrom EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureRating: 4.5 out of 5 stars4.5/5 (474)

- Her Body and Other Parties: StoriesFrom EverandHer Body and Other Parties: StoriesRating: 4 out of 5 stars4/5 (821)

- The Emperor of All Maladies: A Biography of CancerFrom EverandThe Emperor of All Maladies: A Biography of CancerRating: 4.5 out of 5 stars4.5/5 (271)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)From EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Rating: 4.5 out of 5 stars4.5/5 (122)

- The Little Book of Hygge: Danish Secrets to Happy LivingFrom EverandThe Little Book of Hygge: Danish Secrets to Happy LivingRating: 3.5 out of 5 stars3.5/5 (401)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyFrom EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyRating: 3.5 out of 5 stars3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)From EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Rating: 4 out of 5 stars4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaFrom EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaRating: 4.5 out of 5 stars4.5/5 (266)

- Team of Rivals: The Political Genius of Abraham LincolnFrom EverandTeam of Rivals: The Political Genius of Abraham LincolnRating: 4.5 out of 5 stars4.5/5 (234)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryFrom EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryRating: 3.5 out of 5 stars3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealFrom EverandOn Fire: The (Burning) Case for a Green New DealRating: 4 out of 5 stars4/5 (74)

- The Unwinding: An Inner History of the New AmericaFrom EverandThe Unwinding: An Inner History of the New AmericaRating: 4 out of 5 stars4/5 (45)

- JNTUH Syllabus 2013 M.tech Communication SysDocument26 pagesJNTUH Syllabus 2013 M.tech Communication SysSRINIVASA RAO GANTANo ratings yet

- JNTUH Syllabus 2013 M.Tech EPSDocument23 pagesJNTUH Syllabus 2013 M.Tech EPSSRINIVASA RAO GANTANo ratings yet

- JNTUH Syllabus 2013 M.Tech CSEDocument33 pagesJNTUH Syllabus 2013 M.Tech CSESRINIVASA RAO GANTANo ratings yet

- JNTUH MBA Course Structure and Syllabus 2013Document80 pagesJNTUH MBA Course Structure and Syllabus 2013SRINIVASA RAO GANTANo ratings yet

- JNTUH MCA Syllabus 2013Document107 pagesJNTUH MCA Syllabus 2013SRINIVASA RAO GANTANo ratings yet

- JNTUH M.TECH PEDS 2013 SyllabusDocument24 pagesJNTUH M.TECH PEDS 2013 SyllabusSRINIVASA RAO GANTA100% (1)

- IP Addresses and SubnettingDocument16 pagesIP Addresses and SubnettingHusnainNo ratings yet

- Guidelines For Open Educational Resources (OER) in Higher EducationDocument27 pagesGuidelines For Open Educational Resources (OER) in Higher EducationSRINIVASA RAO GANTANo ratings yet

- JNTUH Syllabus 2013 Civil Engg Course StructureDocument2 pagesJNTUH Syllabus 2013 Civil Engg Course StructureSRINIVASA RAO GANTANo ratings yet

- Kvs Librarypolicy2012Document59 pagesKvs Librarypolicy2012SRINIVASA RAO GANTANo ratings yet

- Vbit Journals 2011-12Document6 pagesVbit Journals 2011-12SRINIVASA RAO GANTANo ratings yet

- Paper-I Set-WDocument16 pagesPaper-I Set-WKaran AggarwalNo ratings yet

- r05011801 Metallurgical AnalysisDocument4 pagesr05011801 Metallurgical AnalysisSRINIVASA RAO GANTANo ratings yet

- Library Quality Criteria For NBA AccreditationDocument3 pagesLibrary Quality Criteria For NBA AccreditationSRINIVASA RAO GANTA100% (6)

- Dspace On WindowsDocument15 pagesDspace On WindowsSRINIVASA RAO GANTANo ratings yet

- Code No: 25079Document8 pagesCode No: 25079SRINIVASA RAO GANTANo ratings yet

- Ready Reckoner Radar EwDocument27 pagesReady Reckoner Radar EwSRINIVASA RAO GANTANo ratings yet

- Code - No: 25042: Freespace Guide CutoffDocument8 pagesCode - No: 25042: Freespace Guide CutoffSRINIVASA RAO GANTANo ratings yet

- Librarian Is Teaching or Non TeachingDocument1 pageLibrarian Is Teaching or Non TeachingSRINIVASA RAO GANTANo ratings yet

- NET EXAM Paper 1Document27 pagesNET EXAM Paper 1shahid ahmed laskar100% (4)

- r05311902 Computer GraphicsDocument4 pagesr05311902 Computer GraphicsSRINIVASA RAO GANTANo ratings yet

- Reg Pay Degree 020110Document16 pagesReg Pay Degree 020110SRINIVASA RAO GANTANo ratings yet

- Code No: 35051Document8 pagesCode No: 35051SRINIVASA RAO GANTANo ratings yet

- Code No: 25056Document8 pagesCode No: 25056SRINIVASA RAO GANTANo ratings yet

- Code No: 25022Document4 pagesCode No: 25022SRINIVASA RAO GANTANo ratings yet

- Rr322105-High Speed AerodynamicsDocument8 pagesRr322105-High Speed AerodynamicsSRINIVASA RAO GANTANo ratings yet

- Code No: 35060Document4 pagesCode No: 35060SRINIVASA RAO GANTANo ratings yet

- Rr322305 ImmunologyDocument4 pagesRr322305 ImmunologySRINIVASA RAO GANTANo ratings yet