Professional Documents

Culture Documents

RS232 Interface

RS232 Interface

Uploaded by

Arun Nath K SCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

RS232 Interface

RS232 Interface

Uploaded by

Arun Nath K SCopyright:

Available Formats

1

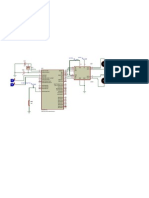

PIC16F84

D VDD R1 16k S1 SW-PB C5 VSS C 4n7 PIC TXD 5V DSR 5V DTR PIC RXD 16 4 17 18 1 2 3 6 VSS IC_PIC1 OSC1/CLKIN OSC2/CLKOUT MCLR RB1 RA0 RB2 RA1 RB3 RA2 RB4 RA3 RB5 RA4/T0CKI RB6 RB0/INT RB7 VSS PIC16F84-04/P(18) 5 15 7 8 9 10 11 12 13 VDD C1 10p (Direction seen from controller) XT1 4.000 MHz VDD 14 VSS RS232 TXD RS232 DTR PIC TXD 5V DSR 13 RS232 8 11 5V 10 1 3 C6 10u C2 10p

MAX232

D VDD VSS C3 10u C4 10u 2 6 16 U1 R1 IN R2 IN T1 IN T2 IN C1+ C1 R1 OUT R2 OUT T1 OUT T2 OUT C2+ C2 12 9 14 7 4 5 V+ VVCC 5V RS232 PIC RXD 5V DTR RS232 RXD RS232 DSR

MAX232CPE(16) 15

GND

C7 10u

VSS

VDD VDD B VSS VSS RS232 DTR RS232 TXD RS232 RXD RS232 DSR 1 6 2 7 3 8 4 9 5

Title

VSS C8 100n VDD

RS232

(Direction seen from host) VSS

DSR and DTR signals are not used in my RS232 routines, but are drawn for completion. These signals are necessary for hardware handshaking, whilst my routines perform no handshaking. The MAX232 has two output and two input channels, specified to transmit up to 120 kbps depending on the type used.

B C9 100n VSS

PIC-RS232 Interface using MAX232

A SUB1 DB9 1 2 3

Written by Date Revision

A

20-Aug-2003 1.01

Page

Peter Luethi Dietikon, Switzerland

1 of 1

You might also like

- Caraca Node by Lancos 1.10: Claudio LanconelliDocument2 pagesCaraca Node by Lancos 1.10: Claudio LanconelliMohamed Zayed100% (1)

- DOP7Document2 pagesDOP7Nghia Do100% (1)

- FPP3Document1 pageFPP3uzunku100% (1)

- K12V +12V +5V: Elektronski Fakultet - Nis Lab. Vezba Iz PredmetaDocument1 pageK12V +12V +5V: Elektronski Fakultet - Nis Lab. Vezba Iz Predmetammmmm1900100% (2)

- DOP7Document1 pageDOP7Mor Se100% (1)

- Propeller Clock at Mega 32Document1 pagePropeller Clock at Mega 32diego140bpm100% (2)

- Two Serial + LCDDocument1 pageTwo Serial + LCDsajitsukumaran5719100% (3)

- PicsimLab Board3Document1 pagePicsimLab Board3cafumanashop100% (2)

- SchemaDocument1 pageSchemaAnonymous 1zdddnyJ100% (2)

- Schematic - Pic ModuleDocument1 pageSchematic - Pic ModuleDuc Le100% (1)

- Interfacing Example - 16 Character X 2 Line LCD: DescriptionDocument5 pagesInterfacing Example - 16 Character X 2 Line LCD: DescriptionManish Kumar sharma100% (1)

- EpspDocument1 pageEpspAhsen Junaid100% (1)

- MOD TC MK2 31855 SchematicDocument1 pageMOD TC MK2 31855 Schematicrdc02271100% (1)

- CAN DemoDocument1 pageCAN DemoTrí Nguyễn100% (1)

- Comunicacao RS232 PICDocument1 pageComunicacao RS232 PICdanilodant100% (2)

- List IC Maxim DallasDocument2 pagesList IC Maxim DallasFudin Safudin100% (1)

- LCD LCD: MCLR Led1 Led2 Led3 Led4 RXD MCLRDocument1 pageLCD LCD: MCLR Led1 Led2 Led3 Led4 RXD MCLRChu Trọng Khanh100% (1)

- MOtorDocument1 pageMOtorvladajk100% (3)

- Sg8V1 Programing Schematic: IC Design Research & Education CenterDocument1 pageSg8V1 Programing Schematic: IC Design Research & Education CenterKit Vi Điều Khiển100% (1)

- PGC PGDDocument1 pagePGC PGDkhoatran524100% (1)

- LCD162C# DatenblattDocument8 pagesLCD162C# Datenblattgeorgschmied100% (1)

- Libreria LCD XC8 PDFDocument2 pagesLibreria LCD XC8 PDFJUAN SEBASTIAN CORREA FERNANDEZ100% (1)

- Diagram ADocument1 pageDiagram AOscar Andres Soto100% (2)

- Pickit2 Clone 1Document1 pagePickit2 Clone 1Lorgio Chura Carrillo100% (1)

- PIC Introduction PDFDocument46 pagesPIC Introduction PDFPeeyush Kp100% (1)

- Schem AnticDocument1 pageSchem Anticthanhv_25100% (1)

- Voltmeter Using 8051.: Circuit DiagramDocument16 pagesVoltmeter Using 8051.: Circuit DiagramVikas Ps100% (1)

- TermometroDocument1 pageTermometroRafael Macfú100% (1)

- PIC18 Pulse Width ModulationDocument16 pagesPIC18 Pulse Width ModulationAnoj Pahathkumbura100% (1)

- DDT Interface (2020 - 03 - 04 12 - 58 - 46 UTC)Document1 pageDDT Interface (2020 - 03 - 04 12 - 58 - 46 UTC)opa952ya.ru100% (1)

- Variador 3.0Document1 pageVariador 3.0Angel Simo Morales100% (1)

- GD7965 Spec0fdeDocument76 pagesGD7965 Spec0fdejhonatan cock100% (1)

- MKR485ShieldV3.0 SCHDocument1 pageMKR485ShieldV3.0 SCHGa3iel100% (1)

- Dead TimeDocument1 pageDead Timebuiphuoclai100% (1)

- Schematic PrintsDocument1 pageSchematic PrintsWeb Devils100% (3)

- CompleteDocument1 pageCompleteTarek Schehadeih100% (1)

- Picprog CircuitDocument1 pagePicprog Circuitmiguel709100% (1)

- Blog Engleandroalves PIC USB PDFDocument1 pageBlog Engleandroalves PIC USB PDFAlexandre Corso100% (2)

- Usbasp: Marius Schäfer (Mschaefer@Mimamau - De)Document1 pageUsbasp: Marius Schäfer (Mschaefer@Mimamau - De)Nagesh Kolte100% (2)

- Avr Isp Usb AioDocument1 pageAvr Isp Usb Aiospy004100% (1)

- LCD Screen 8051Document23 pagesLCD Screen 8051ahimpli100% (2)

- DS Zadaci PDFDocument23 pagesDS Zadaci PDFArnela Tatic100% (1)

- PT2312E SDocument5 pagesPT2312E Sguillecompaq100% (1)

- SCHEMATIC2 LedDriverDocument1 pageSCHEMATIC2 LedDriverthanhlinh9191100% (1)

- Schematic1 - Page1Document1 pageSchematic1 - Page1VânSơn100% (2)

- Picpgm Usb v1.0Document1 pagePicpgm Usb v1.0Yudi Ananta Rangkuti100% (1)

- Agribot Project PresentationDocument21 pagesAgribot Project Presentationumaiya1990100% (1)

- Lector de Bus de Datos IÂ CDocument4 pagesLector de Bus de Datos IÂ CGiancarloRichardRivadeneyraMiranda100% (1)

- DiseqC SCHDocument1 pageDiseqC SCHnaseerak100% (2)

- Book PIC Microcontrollers-Chapter 5 CCP ModulesDocument17 pagesBook PIC Microcontrollers-Chapter 5 CCP ModulesHammamiSalah100% (1)

- 3921 Fig 02Document1 page3921 Fig 02Matheus Régis Dias100% (2)

- CAN Pirate SchematicsDocument1 pageCAN Pirate SchematicsDon Johnson100% (1)

- Nec Ir For PicDocument14 pagesNec Ir For Picsudhakar5472100% (1)

- Ping Ultrasonic Range FinderDocument5 pagesPing Ultrasonic Range FinderIdris Affandy100% (1)

- Povdd POVDD0Discovery Posignal0Out Povdd Povdd0Discovery: PIC201 PIC202 PIC401 PIC402 PIC201 PIC202 PIC401 PIC402Document4 pagesPovdd POVDD0Discovery Posignal0Out Povdd Povdd0Discovery: PIC201 PIC202 PIC401 PIC402 PIC201 PIC202 PIC401 PIC402Leonardo Ortiz67% (3)

- ZadatciDocument22 pagesZadatciTakticar100% (1)

- PICkit - 2 5V3.3V SchematicDocument1 pagePICkit - 2 5V3.3V SchematicJuan Carlos Mediavilla100% (2)

- PT2314Document4 pagesPT2314Yamir Sandoval100% (1)

- G5 SchematicDocument1 pageG5 Schematicjkifnoin100% (1)

- VCC 12V: PR14 SchematicDocument1 pageVCC 12V: PR14 SchematicHazmi HanifNo ratings yet