Professional Documents

Culture Documents

FPGA Implementation: Connect FPGA Kit To The CPU With JTAG Cable

FPGA Implementation: Connect FPGA Kit To The CPU With JTAG Cable

Uploaded by

vijaykannamalla0 ratings0% found this document useful (0 votes)

13 views39 pages1) An FPGA project is created and a Verilog file is added to implement a XOR gate.

2) The FPGA is configured by generating a UCF file, implementing the design, and assigning pin numbers.

3) The configured FPGA is programmed and the XOR gate functionality is observed by providing different input combinations and observing the output LEDs.

Original Description:

Original Title

fpga_imp

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

PPT, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Document1) An FPGA project is created and a Verilog file is added to implement a XOR gate.

2) The FPGA is configured by generating a UCF file, implementing the design, and assigning pin numbers.

3) The configured FPGA is programmed and the XOR gate functionality is observed by providing different input combinations and observing the output LEDs.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

13 views39 pagesFPGA Implementation: Connect FPGA Kit To The CPU With JTAG Cable

FPGA Implementation: Connect FPGA Kit To The CPU With JTAG Cable

Uploaded by

vijaykannamalla1) An FPGA project is created and a Verilog file is added to implement a XOR gate.

2) The FPGA is configured by generating a UCF file, implementing the design, and assigning pin numbers.

3) The configured FPGA is programmed and the XOR gate functionality is observed by providing different input combinations and observing the output LEDs.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as PPT, PDF, TXT or read online from Scribd

You are on page 1of 39

FPGA Implementation

Connect FPGA Kit to the CPU with JTAG cable

To create new project

Choose the properties as shown depending on the target device

Next

Next Then

Next

Device is added to our project

Add source file to the Device from modelsim

Choose path where we select modelsim simulation file D:/ ramanakumari / xorgate2.v

It will add selected file to the created project And to targeted device. As shown

To configure the FPGA Generate UCF file

It generate UCF file in source window. shown

Double click on implement design

Post route simulation will be completed

Assign pin numbers of the target device using User constraints

User constraints assign package pins Then save ok close the window

Configure device [IMPATT]

Select file from Assign New Configuration File window

Right click Program

observe program succeeded

Give 0s and 1s with different combinations to the inputs on FPGA Kit and observe the outputs

Connect JTAG to the processor & powersupply

We can observe XOR gate functionality 2 Switches OFF Position & observe the output zero , by observing not glowing LED, Inputs A = 0 ,B = 0 & Output Y = 0

Inputs A = 0 ,B = 1 & Output Y = 1

Inputs A = 1 ,B = 0 & Output Y = 1

Inputs A = 1 ,B = 1 & Output Y = 0

You might also like

- PLC Programming Using SIMATIC MANAGER for Beginners: With Basic Concepts of Ladder Logic ProgrammingFrom EverandPLC Programming Using SIMATIC MANAGER for Beginners: With Basic Concepts of Ladder Logic ProgrammingRating: 4 out of 5 stars4/5 (1)

- STM Notes Unit1Document61 pagesSTM Notes Unit1vijaykannamalla100% (1)

- LAB Manual Intel GalileoDocument24 pagesLAB Manual Intel GalileoHanamant SaleNo ratings yet

- VLSIDocument65 pagesVLSIChandrashekarNo ratings yet

- A Beginner's Guide To MAX+plus II: Quick ReferenceDocument8 pagesA Beginner's Guide To MAX+plus II: Quick ReferenceHemantkumarNo ratings yet

- Lab 2 FpgaDocument21 pagesLab 2 FpgaFarhana FadzliNo ratings yet

- Ex 2Document26 pagesEx 2Ako C SeanNo ratings yet

- Steps To Implement The Half Adder in The FPGA Using Xilinx ISEDocument18 pagesSteps To Implement The Half Adder in The FPGA Using Xilinx ISEAnonymous naEAR9adNo ratings yet

- Introduction To MP Lab, Universal Programmer and Device ProgrammingDocument9 pagesIntroduction To MP Lab, Universal Programmer and Device ProgrammingRana EhsanNo ratings yet

- Programming Device Manual Booklet: AVR Prog USB v2, STK500 v2Document17 pagesProgramming Device Manual Booklet: AVR Prog USB v2, STK500 v2emanueldanielNo ratings yet

- Programming Device Manual Booklet: AVR Prog USB v2, STK500 v2Document17 pagesProgramming Device Manual Booklet: AVR Prog USB v2, STK500 v2vali29No ratings yet

- Oppstartsmanual KV-Multiprog 2Document12 pagesOppstartsmanual KV-Multiprog 2thang doanNo ratings yet

- Step-1: Open: ISE Design Suite Step-2: Create New Project From File TabDocument9 pagesStep-1: Open: ISE Design Suite Step-2: Create New Project From File TabAnandNo ratings yet

- Pes1ug20ec217 Isa03 2022 23 Ue20ec324Document11 pagesPes1ug20ec217 Isa03 2022 23 Ue20ec324Vaishnavi B VNo ratings yet

- Step-1: Open: ISE Design Suite Step-2: Create New Project From File TabDocument9 pagesStep-1: Open: ISE Design Suite Step-2: Create New Project From File TabBuvanesh KanthNo ratings yet

- PWM in MPLAB Xpress Evaluation BoardDocument10 pagesPWM in MPLAB Xpress Evaluation BoardsivaNo ratings yet

- Project2 PsocDocument10 pagesProject2 PsocKarthik V KalyaniNo ratings yet

- Exp 3Document5 pagesExp 3Ashwini KothavaleNo ratings yet

- Basic Logic Gates: Expt - No: DateDocument2 pagesBasic Logic Gates: Expt - No: DatelalithaNo ratings yet

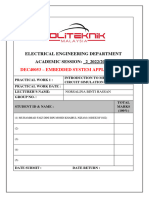

- Electrical Engineering Department Academic Session:: Dec40053 - Embedded System ApplicationsDocument21 pagesElectrical Engineering Department Academic Session:: Dec40053 - Embedded System ApplicationsIskandar YussofNo ratings yet

- AG Processor Replacement ProcedureDocument13 pagesAG Processor Replacement ProcedurekushwahanirajNo ratings yet

- Altera Quartus II and DE2 ManualDocument19 pagesAltera Quartus II and DE2 ManualMinh TrươngNo ratings yet

- Create A Project Using The Base System Builder in EDK10Document17 pagesCreate A Project Using The Base System Builder in EDK10nharsoor0488509No ratings yet

- Interfacing Gocator To Aurora Vision StudioDocument12 pagesInterfacing Gocator To Aurora Vision Studiovlp_bkNo ratings yet

- Nexys2 ISE 12 - 2 Decoder TutorialDocument15 pagesNexys2 ISE 12 - 2 Decoder TutorialVale Conde CuatzoNo ratings yet

- CPS Lab Report FinalDocument38 pagesCPS Lab Report Finaldevikam230354ecNo ratings yet

- SmartFusion SoftConsole POTlevel UART Tutorial UGDocument48 pagesSmartFusion SoftConsole POTlevel UART Tutorial UGfiveanglesNo ratings yet

- JNIOR Guidelines EditedDocument8 pagesJNIOR Guidelines EditedDanialSimmondsNo ratings yet

- Tutorial1 ISE Project CreationDocument26 pagesTutorial1 ISE Project Creationvetalap7No ratings yet

- 05FPGA的inout双向端口的使用之IIC读写eepromDocument6 pages05FPGA的inout双向端口的使用之IIC读写eepromMicro ZicNo ratings yet

- Electrical Engineering Department Practical Work 1Document35 pagesElectrical Engineering Department Practical Work 1NanaNo ratings yet

- VLSI Design LabDocument47 pagesVLSI Design LabqwertyuiopNo ratings yet

- Lab 1 TutorialDocument12 pagesLab 1 Tutorialmicrobotica126No ratings yet

- 2-TX FSK 15-16 Part 1Document8 pages2-TX FSK 15-16 Part 1Đặng Hoài Sơn100% (1)

- Computer Architecture Lab 2Document6 pagesComputer Architecture Lab 2Hasan IqbalNo ratings yet

- Exp 6Document5 pagesExp 6Ashwini KothavaleNo ratings yet

- Prathyusha: Engineering CollegeDocument41 pagesPrathyusha: Engineering CollegeVenkata sai Prasad ChevuruNo ratings yet

- Module 15 - Smart GeneratorsDocument15 pagesModule 15 - Smart GeneratorsMarious EesNo ratings yet

- 4D LCD Interface With MyRIODocument16 pages4D LCD Interface With MyRIOMuhammad Jazztyan Indra PradanaNo ratings yet

- PSoC 3Document25 pagesPSoC 3studedictsNo ratings yet

- USB Connection - Rev 20150923Document19 pagesUSB Connection - Rev 20150923Antero CasaniNo ratings yet

- DocumentationDocument3 pagesDocumentationHarshaBornfreeNo ratings yet

- COMP600 Spring Lab#2Document7 pagesCOMP600 Spring Lab#2jassica sahiNo ratings yet

- How To Download Program To The FPGA Board PDFDocument6 pagesHow To Download Program To The FPGA Board PDFRonnyNo ratings yet

- Lab Manual MES Experiment 1Document7 pagesLab Manual MES Experiment 1Kazi Al - KabidNo ratings yet

- Introduction To Quartus IIDocument13 pagesIntroduction To Quartus IICarine ChiaNo ratings yet

- Lab Report # 1: Sheikh Muhammad IsmailDocument22 pagesLab Report # 1: Sheikh Muhammad IsmailRajabackforgameNo ratings yet

- Hello World in EDKDocument21 pagesHello World in EDKconbo168No ratings yet

- DDP Lab 2Document9 pagesDDP Lab 2Eduardo ToribioNo ratings yet

- The Coding Chronicles - Chapter 1 PDFDocument9 pagesThe Coding Chronicles - Chapter 1 PDFhkNo ratings yet

- Krypton ManualDocument10 pagesKrypton ManualNaman JainNo ratings yet

- Auto-Gate ReportDocument21 pagesAuto-Gate Reportstamford_bridgeNo ratings yet

- Digital Circuit DesignDocument61 pagesDigital Circuit DesignJavier CruzNo ratings yet

- Lab 1Document10 pagesLab 1zagarzusemNo ratings yet

- PW1 Labsheet Embd System FaizDocument26 pagesPW1 Labsheet Embd System FaizIskandar YussofNo ratings yet

- Pro LoadDocument2 pagesPro Loadsunnynnus100% (2)

- UntitledDocument23 pagesUntitledShunethra SenthilkumarNo ratings yet

- SONOFF Zigbee 3.0 USB Dongle Plus Firmware FlashingDocument8 pagesSONOFF Zigbee 3.0 USB Dongle Plus Firmware FlashingpugNo ratings yet

- Lab ECAD 5Document11 pagesLab ECAD 5Noor Afiq100% (1)

- Experiment No. 4: Aim: Write A Simple NIOS II Program That Can Perform Simple I/O To Read Switches and WriteDocument4 pagesExperiment No. 4: Aim: Write A Simple NIOS II Program That Can Perform Simple I/O To Read Switches and WriteMohammad AtiqueNo ratings yet

- Details of Apios, Pios & Appellate Authorities Department of Horticulture, T.S., HydDocument3 pagesDetails of Apios, Pios & Appellate Authorities Department of Horticulture, T.S., HydvijaykannamallaNo ratings yet

- Pyxis SDL - ManualDocument119 pagesPyxis SDL - ManualvijaykannamallaNo ratings yet

- Detection of Brain Tumor Using Otsu-Region Based Method of SegmentationDocument7 pagesDetection of Brain Tumor Using Otsu-Region Based Method of SegmentationvijaykannamallaNo ratings yet

- Academic Calendar For The Ii, Iii & Iv B.tech I & Ii Sem Academic Year 2020-2021Document2 pagesAcademic Calendar For The Ii, Iii & Iv B.tech I & Ii Sem Academic Year 2020-2021vijaykannamallaNo ratings yet

- EsDocument18 pagesEsvijaykannamallaNo ratings yet

- Process of Converting Purchases To EMI For LIC Credit CardDocument2 pagesProcess of Converting Purchases To EMI For LIC Credit CardvijaykannamallaNo ratings yet

- Ijmte Dec - VCDocument10 pagesIjmte Dec - VCvijaykannamallaNo ratings yet

- The 8086 Microprocessor Supports 8 Types of InstructionsDocument6 pagesThe 8086 Microprocessor Supports 8 Types of InstructionsvijaykannamallaNo ratings yet

- Instruction Set ImpDocument23 pagesInstruction Set ImpvijaykannamallaNo ratings yet

- Ac UnitDocument32 pagesAc UnitvijaykannamallaNo ratings yet

- EC6513 Microprocessor Microcontroller Lab 1 2013 RegulationDocument92 pagesEC6513 Microprocessor Microcontroller Lab 1 2013 RegulationvijaykannamallaNo ratings yet

- Awp Course FileDocument24 pagesAwp Course FilevijaykannamallaNo ratings yet

- CN Hand Written NotesDocument180 pagesCN Hand Written NotesvijaykannamallaNo ratings yet

- New MPMC Lab 2015 16 2 - 0Document101 pagesNew MPMC Lab 2015 16 2 - 0vijaykannamallaNo ratings yet

- Assembler Directives and OperatorsDocument6 pagesAssembler Directives and Operatorsvijaykannamalla100% (1)

- 2 5Document14 pages2 5vijaykannamallaNo ratings yet

- Chapter 3 ImpDocument5 pagesChapter 3 ImpvijaykannamallaNo ratings yet

- Invoice: Gat No.592/2 H No.2044 Midc Shiroli Kolhapur 27621101624V 27621101624CDocument1 pageInvoice: Gat No.592/2 H No.2044 Midc Shiroli Kolhapur 27621101624V 27621101624CvijaykannamallaNo ratings yet

- Scanned by CamscannerDocument34 pagesScanned by CamscannervijaykannamallaNo ratings yet

- Paper - Ii: General Mathematics (SSC STD.,) ARITHMETIC: Number System-Natural Numbers, Integers, Rational and Real NumbersDocument2 pagesPaper - Ii: General Mathematics (SSC STD.,) ARITHMETIC: Number System-Natural Numbers, Integers, Rational and Real NumbersvijaykannamallaNo ratings yet

- 3rd UnitDocument12 pages3rd UnitvijaykannamallaNo ratings yet

- Development of A Real-Time Embedded System For Speech Emotion RecognitionDocument35 pagesDevelopment of A Real-Time Embedded System For Speech Emotion RecognitionvijaykannamallaNo ratings yet

- A Cell Phone-Based Remote Home Control System: Presentation by SrinivasDocument32 pagesA Cell Phone-Based Remote Home Control System: Presentation by SrinivasvijaykannamallaNo ratings yet

- Ae NotesDocument286 pagesAe NotesvijaykannamallaNo ratings yet

- Resume LayoutDocument10 pagesResume LayoutvijaykannamallaNo ratings yet