Professional Documents

Culture Documents

Logic Gates Number

Logic Gates Number

Uploaded by

Selvasundar KumarOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Logic Gates Number

Logic Gates Number

Uploaded by

Selvasundar KumarCopyright:

Available Formats

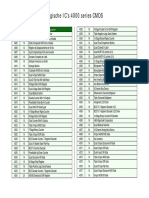

Part number

Description

7400

quad 2-input NAND gate

741G00

single 2-input NAND gate

7401

quad 2-input NAND gate with open collector outputs

741G01

single 2-input NAND gate with open drain output

7402

quad 2-input NOR gate

741G02

single 2-input NOR gate

7403

quad 2-input NAND gate with open collector outputs

741G03

single 2-input NAND gate with open drain output

7404

he in!erter

741G04

single in!erter

740"

he in!erter with open collector outputs

741G0"

single in!erter with open drain output

740#

he in!erter $u%%er&dri!er with 30 ! open collector outputs

741G0#

single in!erting $u%%er&dri!er with open drain output

7407

he $u%%er&dri!er with 30 ! open collector outputs

741G07

single non-in!erting $u%%er&dri!er with open drain output

740'

quad 2-input AND gate

741G0'

single 2-input AND gate

740(

quad 2-input AND gate with open collector outputs

741G0(

single 2-input AND gate with open drain output

7410

triple 3-input NAND gate

7411

triple 3-input AND gate

7412

triple 3-input NAND gate with open collector outputs

7413

dual )ch*itt trigger 4-input NAND gate

7414

he )ch*itt trigger in!erter

741G14

single )ch*itt trigger in!erter

741"

triple 3-input AND gate with open collector outputs

741#

he in!erter $u%%er&dri!er with 1" ! open collector outputs

7417

he $u%%er&dri!er with 1" ! open collector outputs

741G17

single )ch*itt-trigger $u%%er

741'

dual 4-input NAND gate with )ch*itt trigger inputs

741(

he )ch*itt trigger in!erter

7420

dual 4-input NAND gate

7421

dual 4-input AND gate

7422

dual 4-input NAND gate with open collector outputs

7423

e panda$le dual 4-input NOR gate with stro$e

7424

quad 2-input NAND gate gates with sch*itt-trigger line-recei!er inputs+

742"

dual 4-input NOR gate with stro$e

742#

quad 2-input NAND gate with 1" ! open collector outputs

7427

triple 3-input NOR gate

741G27

single 3-input NOR gate

742'

quad 2-input NOR $u%%er

7430

'-input NAND gate

7431

he dela, ele*ents

7432

quad 2-input OR gate

741G32

single 2-input OR gate

7433

quad 2-input NOR $u%%er with open collector outputs

743#

quad 2-input NOR gate -di%%erent pinout than 7402.

7437

quad 2-input NAND $u%%er

743'

quad 2-input NAND $u%%er with open collector outputs

743(

quad 2-input NAND $u%%er

7440

dual 4-input NAND $u%%er

7441

/0D to deci*al decoder&Ni ie tu$e dri!er

7442

/0D to deci*al decoder

7443

e cess-3 to deci*al decoder

7444

e cess-3-Gra, code to deci*al decoder

744"

/0D to deci*al decoder&dri!er

744#

/0D to se!en-seg*ent displa, decoder&dri!er with 30 ! open collector outputs

7447

/0D to 7-seg*ent decoder&dri!er with 1" ! open collector outputs

744'

/0D to 7-seg*ent decoder&dri!er with 1nternal 2ullups

744(

/0D to 7-seg*ent decoder&dri!er with open collector outputs

74"0

dual 2-wide 2-input AND-OR-in!ert gate -one gate e panda$le.

74"1

dual 2-wide 2-input AND-OR-in!ert gate

74"2

e panda$le 4-wide 2-input AND-OR gate

74"3

e panda$le 4-wide 2-input AND-OR-in!ert gate

74"4

4-wide 2-input AND-OR-in!ert gate

74""

2-wide 4-input AND-OR-in!ert Gate -743 !ersion is e panda$le.

74"#

"041 %requenc, di!ider

74"7

#041 %requenc, di!ider

74"'

2-input 5 3-input AND-OR Gate

74"(

2-input 5 3-input AND-OR-in!ert Gate

74#0

dual 4-input e pander

74#1

triple 3-input e pander

74#2

3-2-2-3-input AND-OR e pander

74#3

he current sensing inter%ace gates

74#4

4-2-3-2-input AND-OR-in!ert gate

74#"

4-2-3-2 input AND-OR-in!ert gate with open collector output

74#'

dual 4 $it decade counters

74#(

dual 4 $it $inar, counters

7470

AND-gated positi!e edge triggered 6-7 %lip-%lop with preset and clear

74371

AND-or-gated 6-7 *aster-sla!e %lip-%lop with preset

74871

AND-gated R-) *aster-sla!e %lip-%lop with preset and clear

7472

AND gated 6-7 *aster-sla!e %lip-%lop with preset and clear

7473

dual 6-7 %lip-%lop with clear

7474

dual D positi!e edge triggered %lip-%lop with preset and clear

747"

4-$it $ista$le latch

747#

dual 6-7 %lip-%lop with preset and clear

7477

4-$it $ista$le latch

7437'

dual positi!e pulse triggered 6-7 %lip-%lop with preset9 co**on cloc:9 and co**on clear -di%%erent pinout than 7487' & 748s7'.

7487'

dual positi!e pulse triggered 6-7 %lip-%lop with preset9 co**on cloc:9 and co**on clear

748s7'

dual negati!e edge triggered 6-7 %lip-%lop with preset9 co**on cloc:9 and co**on clear

747(

dual D %lip-%lop

741G7(

single D-t,pe %lip-%lop positi!e edge trigger non-in!erting output

74'0

gated %ull adder

741G'0

single D-t,pe %lip-%lop positi!e edge trigger in!erting output

74'1

1#-$it rando* access *e*or,

74'2

2-$it $inar, %ull adder

74'3

4-$it $inar, %ull adder

74'4

1#-$it rando* access *e*or,

74'"

4-$it *agnitude co*parator

74'#

quad 2-input ;OR gate

741G'#

single 2 input e clusi!e-OR gate

74'7

4-$it true&co*ple*ent&<ero&one ele*ent

74''

2"#-$it read-onl, *e*or,

74'(

#4-$it rando* access *e*or,

74(0

decade counter -separate di!ide-$,-2 and di!ide-$,-" sections.

74(1

'-$it shi%t register9 serial 1n9 serial out9 gated input

74(2

di!ide-$,-12 counter -separate di!ide-$,-2 and di!ide-$,-# sections.

74(3

4-$it $inar, counter -separate di!ide-$,-2 and di!ide-$,-' sections.

74(4

4-$it shi%t register9 dual as,nchronous presets

74("

4-$it shi%t register9 parallel 1n9 parallel out9 serial input

74(#

"-$it parallel-1n¶llel-out shi%t register9 as,nchronous preset

74(7

s,nchronous #-$it $inar, rate *ultiplier

741G(7

con%igura$le *ultiple-%unction gate

74('

4-$it data selector&storage register

74((

4-$it $idirectional uni!ersal shi%t register

74100

dual 4-$it $ista$le latch

74101

AND-or-gated 6-7 negati!e-edge-triggered %lip-%lop with preset

74102

AND-gated 6-7 negati!e-edge-triggered %lip-%lop with preset and clear

74103

dual 6-7 negati!e-edge-triggered %lip-%lop with clear

74104

6-7 *aster-sla!e %lip-%lop

7410"

6-7 *aster-sla!e %lip-%lop

7410#

dual 6-7 negati!e-edge-triggered %lip-%lop with preset and clear

74107

dual 6-7 %lip-%lop with clear

74107a

dual 6-7 negati!e-edge-triggered %lip-%lop with clear

7410'

dual 6-7 negati!e-edge-triggered %lip-%lop with preset9 co**on clear9 and co**on cloc:

7410(

dual 6-Not-7 positi!e-edge-triggered %lip-%lop with clear and preset

74110

AND-gated 6-7 *aster-sla!e %lip-%lop with data loc:out

74111

dual 6-7 *aster-sla!e %lip-%lop with data loc:out

74112

dual 6-7 negati!e-edge-triggered %lip-%lop with clear and preset

74113

dual 6-7 negati!e-edge-triggered %lip-%lop with preset

74114

dual 6-7 negati!e-edge-triggered %lip-%lop with preset9 co**on cloc: and clear

7411#

dual 4-$it latch with clear

7411'

he set&reset latch

7411(

he set&reset latch

74120

dual pulse s,nchroni<er&dri!ers

74121

*onosta$le *ulti!i$rator

74122

retriggera$le *onosta$le *ulti!i$rator with clear

74123

dual retriggera$le *onosta$le *ulti!i$rator with clear

741G123

single retriggera$le *onosta$le *ulti!i$rator with clear

74124

dual !oltage-controlled oscillator

7412"

quad $us $u%%er with three-state outputs9 negati!e ena$le

741G12"

$u%%er&8ine dri!er9 three-state output with acti!e low output ena$le

7412#

quad $us $u%%er with three-state outputs9 positi!e ena$le

7412'

quad 2-input NOR 8ine dri!er

741G12#

$u%%er&line dri!er9 three-state output with acti!e high output ena$le

74130

quad 2-input AND gate $u%%er with 30 ! open collector outputs

74131

quad 2-input AND gate $u%%er with 1" ! open collector outputs

74132

quad 2-input NAND sch*itt trigger

74133

13-input NAND gate

74134

12-input NAND gate with three-state output

7413"

quad e clusi!e-or&NOR gate

7413#

quad 2-input ;OR gate with open collector outputs

74137

3 to '-line decoder&de*ultiple er with address latch

7413'

3 to '-line decoder&de*ultiple er

7413(

dual 2 to 4-line decoder&de*ultiple er

74140

dual 4-input NAND line dri!er

74141

/0D to deci*al decoder&dri!er %or cold-cathode indicator&Ni ie tu$e

74142

decade counter&latch&decoder&dri!er %or Ni ie tu$es

74143

decade counter&latch&decoder&7-seg*ent dri!er9 1" *a constant current

74144

decade counter&latch&decoder&7-seg*ent dri!er9 1" ! open collector outputs

7414"

/0D to deci*al decoder&dri!er

74147

10-line to 4-line priorit, encoder

7414'

'-line to 3-line priorit, encoder

741"0

1#-line to 1-line data selector&*ultiple er

741"1

'-line to 1-line data selector&*ultiple er

741"2

'-line to 1-line data selector&*ultiple er

741"3

dual 4-line to 1-line data selector&*ultiple er

741"4

4-line to 1#-line decoder&de*ultiple er

741""

dual 2-line to 4-line decoder&de*ultiple er

741"#

dual 2-line to 4-line decoder&de*ultiple er with open collector outputs

741"7

quad 2-line to 1-line data selector&*ultiple er9 nonin!erting

741"'

quad 2-line to 1-line data selector&*ultiple er9 in!erting

741"(

4-line to 1#-line decoder&de*ultiple er with open collector outputs

741#0

s,nchronous 4-$it decade counter with as,nchronous clear

741#1

s,nchronous 4-$it $inar, counter with as,nchronous clear

741#2

s,nchronous 4-$it decade counter with s,nchronous clear

741#3

s,nchronous 4-$it $inar, counter with s,nchronous clear

741#4

'-$it parallel-out serial shi%t register with as,nchronous clear

741#"

'-$it serial shi%t register9 parallel 8oad9 co*ple*entar, outputs

741##

parallel-8oad '-$it shi%t register

741#7

s,nchronous decade rate *ultiplier

741#'

s,nchronous 4-$it up&down decade counter

741#(

s,nchronous 4-$it up&down $inar, counter

74170

4 $, 4 register %ile with open collector outputs

74172

1#-$it *ultiple port register %ile with three-state outputs

74173

quad d %lip-%lop with three-state outputs

74174

he d %lip-%lop with co**on clear

7417"

quad d edge-triggered %lip-%lop with co*ple*entar, outputs and as,nchronous clear

7417#

presetta$le decade -$i-quinar,. counter&latch

74177

presetta$le $inar, counter&latch

7417'

4-$it parallel-access shi%t register

7417(

4-$it parallel-access shi%t register with as,nchronous clear and co*ple*entar, = d outputs

741'0

(-$it odd&e!en parit, $it generator and chec:er

741'1

4-$it arith*etic logic unit and %unction generator

741'2

loo:ahead carr, generator

741'3

dual carr,-sa!e %ull adder

741'4

/0D to $inar, con!erter

741'"

$inar, to /0D con!erter

741'#

"12-$it -#4 '. read-onl, *e*or, with open collector outputs

741'7

1024-$it -2"# 4. read onl, *e*or, with open collector outputs

741''

2"#-$it -32 '. progra**a$le read-onl, *e*or, with open collector outputs

741'(

#4-$it -1# 4. ra* with in!erting three-state outputs

741(0

s,nchronous up&down decade counter

741(1

s,nchronous up&down $inar, counter

741(2

s,nchronous up&down decade counter with clear

741(3

s,nchronous up&down $inar, counter with clear

741(4

4-$it $idirectional uni!ersal shi%t register

741("

4-$it parallel-access shi%t register

741(#

presetta$le decade counter&latch

741(7

presetta$le $inar, counter&latch

741('

'-$it $idirectional uni!ersal shi%t register

741((

'-$it $idirectional uni!ersal shi%t register with 6-Not-7 serial inputs

74200

2"#-$it ra* with three-state outputs

74201

2"#-$it -2"# 1. ra* with three-state outputs

7420#

2"#-$it ra* with open collector outputs

7420(

1024-$it -1024 1. ra* with three-state output

74210

octal $u%%er

7421(

#4-$it -1# 4. ra* with nonin!erting three-state outputs

74221

dual *onosta$le *ulti!i$rator with sch*itt trigger input

74222

1# $, 4 s,nchronous >1>O *e*or, with three-state outputs

74224

1# $, 4 s,nchronous >1>O *e*or, with three-state outputs

7422"

as,nchronous 1# " >1>O *e*or,

7422#

4-$it parallel latched $us transcei!er with three-state outputs

74230

octal $u%%er&dri!er with three-state outputs

74232

quad NOR )ch*itt trigger

74237

1-o%-' decoder&de*ultiple er with address latch9 acti!e high outputs

7423'

1-o%-' decoder&de*ultiple er9 acti!e high outputs

7423(

dual 2-o%-4 decoder&de*ultiple er9 acti!e high outputs

74240

octal $u%%er with 1n!erted three-state outputs

74241

octal $u%%er with nonin!erted three-state outputs

74242

quad $us transcei!er with 1n!erted three-state outputs

74243

quad $us transcei!er with nonin!erted three-state outputs

74244

octal $u%%er with nonin!erted three-state outputs

7424"

octal $us transcei!er with nonin!erted three-state outputs

7424#

/0D to 7-seg*ent decoder&dri!er with 30 ! open collector outputs

74247

/0D to 7-seg*ent decoder&dri!er with 1" ! open collector outputs

7424'

/0D to 7-seg*ent decoder&dri!er with 1nternal 2ull-up outputs

7424(

/0D to 7-seg*ent decoder&dri!er with open collector outputs

742"1

'-line to 1-line data selector&*ultiple er with co*ple*entar, three-state outputs

742"3

dual 4-line to 1-line data selector&*ultiple er with three-state outputs

742""

dual 4-$it addressa$le latch

742"#

dual 4-$it addressa$le latch

742"7

quad 2-line to 1-line data selector&*ultiple er with nonin!erted three-state outputs

742"'

quad 2-line to 1-line data selector&*ultiple er with 1n!erted three-state outputs

742"(

'-$it addressa$le latch

742#0

dual "-input NOR gate

742#1

2-$it $, 4-$it parallel $inar, *ultiplier

742#"

quad co*ple*entar, output ele*ents

742##

quad 2-input ;NOR gate with open collectoroutputs

74270

204'-$it -"12 4. read onl, *e*or, with open collector outputs

74271

204'-$it -2"# '. read onl, *e*or, with open collector outputs

74273

'-$it register with reset

74274

4-$it $, 4-$it $inar, *ultiplier

7427"

7-$it slice ?allace tree

7427#

quad 6-Not-7 edge-triggered >lip->lops with separate cloc:s9 co**on preset and clear

7427'

4-$it cascadea$le priorit, registers with latched data inputs

7427(

quad set-reset latch

742'0

(-$it odd&e!en 2arit, $it Generator&chec:er

742'1

4-$it parallel $inar, accu*ulator

742'3

4-$it $inar, >ull adder

742'4

4-$it $, 4-$it parallel $inar, *ultiplier -low order 4 $its o% product.

742'"

4-$it $, 4-$it parallel $inar, *ultiplier -high order 4 $its o% product.

742'7

1024-$it -2"# 4. progra**a$le read-onl, *e*or, with three-state outputs

742''

2"#-$it -32 '. progra**a$le read-onl, *e*or, with three-state outputs

742'(

#4-$it -1# 4. RA@ with open collector outputs

742(0

decade counter -separate di!ide-$,-2 and di!ide-$,-" sections.

742(1

4-$it uni!ersal shi%t register9 $inar, up&down counter9 s,nchronous

742(2

progra**a$le %requenc, di!ider&digital ti*er

742(3

4-$it $inar, counter -separate di!ide-$,-2 and di!ide-$,-' sections.

742(4

progra**a$le %requenc, di!ider&digital ti*er

742("

4-$it $idirectional register with three-state outputs

742(7

digital phase-loc:ed-loop %ilter

742('

quad 2-input *ultiple er with storage

742((

'-$it $idirectional uni!ersal shi%t&storage register with three-state outputs

74301

2"#-$it -2"# 1. rando* access *e*or, with open collector output

7430(

1024-$it -1024 1. rando* access *e*or, with open collector output

74310

octal $u%%er with )ch*itt trigger inputs

74314

1024-$it rando* access *e*or,

74320

cr,stal controlled oscillator

74322

'-$it shi%t register with sign e tend9 three-state outputs

74323

'-$it $idirectional uni!ersal shi%t&storage register with three-state outputs

74324

!oltage controlled oscillator -or cr,stal controlled.

74340

octal $u%%er with )ch*itt trigger inputs and three-state in!erted outputs

74341

octal $u%%er with )ch*itt trigger inputs and three-state nonin!erted outputs

74344

octal $u%%er with )ch*itt trigger inputs and three-state nonin!erted outputs

7434'

' to 3-line priorit, encoder with three-state outputs

743"0

4-$it shi%ter with three-state outputs

743"1

dual '-line to 1-line data selectors&*ultiple ers with three-state outputs and 4 co**on data inputs

743"2

dual 4-line to 1-line data selectors&*ultiple ers with in!erting outputs

743"3

dual 4-line to 1-line data selectors&*ultiple ers with in!erting three-state outputs

743"4

' to 1-line data selector&*ultiple er with transparent latch9 three-state outputs

743"#

' to 1-line data selector&*ultiple er with edge-triggered register9 three-state outputs

743#1

$u$$le *e*or, %unction ti*ing generator

743#2

%our-phase cloc: generator&dri!er

743#"

he $u%%er with nonin!erted three-state outputs

743##

he $u%%er with 1n!erted three-state outputs

743#7

he $u%%er with nonin!erted three-state outputs

743#'

he $u%%er with 1n!erted three-state outputs

74370

204'-$it -"12 4. read-onl, *e*or, with three-state outputs

74371

204'-$it -2"# '. read-onl, *e*or, with three-state outputs

74373

octal transparent latch with three-state outputs

741G373

single transparent latch with three-state output

74374

octal register with three-state outputs

741G374

single d-t,pe %lip-%lop with three-state output

7437"

quad $ista$le latch

7437#

quad 6-Not-7 %lip-%lop with co**on cloc: and co**on clear

74377

'-$it register with cloc: ena$le

7437'

#-$it register with cloc: ena$le

7437(

4-$it register with cloc: ena$le and co*ple*entar, outputs

743'0

'-$it *ulti%unction register

743'1

4-$it arith*etic logic unit&%unction generator with generate and propagate outputs

743'2

4-$it arith*etic logic unit&%unction generator with ripple carr, and o!er%low outputs

743'"

quad 4-$it adder&su$tractor

743'#

quad 2-input ;OR gate

743'7

1024-$it -2"# 4. progra**a$le read-onl, *e*or, with open collector outputs

743''

4-$it register with standard and three-state outputs

743(0

dual 4-$it decade counter

743(3

dual 4-$it $inar, counter

743("

4-$it uni!ersal shi%t register with three-state outputs

743('

quad 2-input *ulitple ers with storage and co*ple*entar, outputs

743((

quad 2-input *ultiple er with storage

7440"

1 to ' decoder9 equi!alent to 1ntel '20"9 onl, %ound as A0B74)40" so *ight $e non-C1 nu*$er

7440'

'-$it parit, tree

74412

*ulti-*ode $u%%ered '-$it latches with three-state outputs and clear

74423

dual retriggera$le *onosta$le *ulti!i$rator

74424

two-phase cloc: generator&dri!er

7442"

quad gates with three-state outputs and acti!e low ena$les

7442#

quad gates with three-state outputs and acti!e high ena$les

7442'

s,ste* controller %or '0'0a

7443'

s,ste* controller %or '0'0a

74440

quad tridirectional $us transcei!er with nonin!erted open collector outputs

74441

quad tridirectional $us transcei!er with 1n!erted open collector outputs

74442

quad tridirectional $us transcei!er with nonin!erted three-state outputs

74443

quad tridirectional $us transcei!er with 1n!erted three-state outputs

74444

quad tridirectional $us transcei!er with 1n!erted and nonin!erted three-state outputs

7444'

quad tridirectional $us transcei!er with 1n!erted and nonin!erted open collector outputs

744"0

1#-to-1 *ultiple er with co*ple*entar, outputs

744"1

dual '-to-1 *ultiple er

744"2

dual decade counter9 s,nchronous

744"3

dual $inar, counter9 s,nchronous

744"3

quad 4-to-1 *ultiple er

744"4

dual decade up&down counter9 s,nchronous9 preset input

744""

dual $inar, up&down counter9 s,nchronous9 preset input

744"#

N/0D -Natural $inar, coded deci*al. adder

744#0

$us trans%er switch

744#1

'-$it presetta$le $inar, counter with three-state outputs

744#2

%i$er-optic lin: trans*itter

744#3

%i$er-optic lin: recei!er

744#"

octal $u%%er with three-state outputs

744#'

dual *os-to-tt8 le!el con!erter

74470

204'-$it -2"# '. progra**a$le read-onl, *e*or, with open collector outputs

74471

204'-$it -2"# '. progra**a$le read-onl, *e*or, with three-state outputs

74472

progra**a$le read-onl, *e*or, with open collector outputs

74473

progra**a$le read-onl, *e*or, with three-state outputs

74474

progra**a$le read-onl, *e*or, with open collector outputs

7447"

progra**a$le read-onl, *e*or, with three-state outputs

744'1

4-$it slice processor ele*ents

744'2

4-$it slice e panda$le control ele*ents

744'4

/0D-to-$inar, con!erter

744'"

$inar,-to-/0D con!erter

744(0

dual decade counter

744(1

10-$it $inar, up&down counter with li*ited preset and three-state outputs

744('

'-$it $idirectional shi%t register with parallel inputs and three-state outputs

74"0'

'-$it *ultiplier&di!ider

74"20

'-$it co*parator

74"21

'-$it co*parator

74"2#

%use progra**a$le identit, co*parator9 1# $it

74"27

%use progra**a$le identit, co*parator9 ' $it D 4 $it con!entional 1dentit, co*parator

74"2'

%use progra**a$le 1dentit, co*parator9 12 $it

74"31

octal transparent latch with 32 *a three-state outputs

74"32

octal register with 32 *a three-state outputs

74"33

octal transparent latch with in!erting three-state 8ogic outputs

74"34

octal register with in!erting three-state outputs

74"3"

octal transparent latch with in!erting three-state outputs

74"3#

octal register with in!erting 32 *a three-state outputs

74"37

/0D to deci*al decoder with three-state outputs

74"3'

1 o% ' decoder with three-state outputs

74"3(

dual 1 o% 4 decoder with three-state outputs

74"40

in!erting octal $u%%er with three-state outputs

74"41

non-in!erting octal $u%%er with three-state outputs

74"44

non-in!erting octal registered transcei!er with three-state outputs

74""'

'-$it $, '-$it *ultiplier with three-state outputs

74"#0

4-$it decade counter with three-state outputs

74"#1

4-$it $inar, counter with three-state outputs

74"#3

'-$it d-t,pe transparent latch with in!erting three-state outputs

74"#4

'-$it d-t,pe edge-triggered register with in!erting three-state outputs

74"#'

decade up&down counter with three-state outputs

74"#(

$inar, up&down counter with three-state outputs

74"73

octal D-t,pe transparent latch with three-state outputs

74"74

octal D-t,pe edge-triggered %lip-%lop with three-state outputs

74"7"

octal D-t,pe %lip-%lop with s,nchronous clear9 three-state outputs

74"7#

octal D-t,pe %lip-%lop with in!erting three-state outputs

74"77

octal D-t,pe %lip-%lop with s,nchronous clear9 in!erting three-state outputs

74"'0

octal transcei!er&latch with in!erting three-state outputs

74"'(

'-$it shi%t register with input latch9 three-state outputs

74"(0

'-$it $inar, counter with output registers and three-state outputs

74"(2

'-$it $inar, counter with input registers

74"(3

'-$it $inar, counter with input registers and three-state outputs

74"(4

serial-in shi%t register with output registers

74"("

serial-in shi%t register with output latches

74"(#

serial-in shi%t register with output registers and open collector outputs

74"(7

serial-out shi%t register with input latches

74"('

shi%t register with input latches

74#00

d,na*ic *e*or, re%resh controller9 transparent and $urst *odes9 %or 47 or 1#7 dra*s

74#01

d,na*ic *e*or, re%resh controller9 transparent and $urst *odes9 %or #47 dra*s

74#02

d,na*ic *e*or, re%resh controller9 c,cle steal and $urst *odes9 %or 47 or 1#7 dra*s

74#03

d,na*ic *e*or, re%resh controller9 c,cle steal and $urst *odes9 %or #47 dra*s

74#04

octal 2-input *ultiple er with latch9 high-speed9 with three-state outputs

74#0"

latch9 high-speed9 with open collector outputs

74#0#

octal 2-input *ultiple er with latch9 glitch-%ree9 with three-state outputs

74#07

octal 2-input *ultiple er with latch9 glitch-%ree9 with open collector outputs

74#0'

*e*or, c,cle controller

74#10

*e*or, *apper9 latched9 three-state outputs

74#11

*e*or, *apper9 latched9 open collector outputs

74#12

*e*or, *apper9 three-state outputs

74#13

*e*or, *apper9 open collector outputs

74#20

octal $us transcei!er9 in!erting9 three-state outputs

74#21

octal $us transcei!er9 nonin!erting9 open collector outputs

74#22

octal $us transcei!er9 in!erting9 open collector outputs

74#23

octal $us transcei!er9 nonin!erting9 three-state outputs

74#24

!oltage-controlled oscillator with ena$le control9 range control9 two-phase outputs

74#2"

dual !oltage-controlled oscillator with two-phase outputs

74#2#

dual !oltage-controlled oscillator with ena$le control9 two-phase outputs

74#27

dual !oltage-controlled oscillator

74#2'

!oltage-controlled oscillator with ena$le control9 range control9 e ternal te*perature co*pensation9 and two-phase outputs

74#2(

dual !oltage-controlled oscillator with ena$le control9 range control

74#30

1#-$it error detection and correction -EDA0. with three-state outputs

74#31

1#-$it error detection and correction with open collector outputs

74#32

32-$it error detection and correction

74#3'

octal $us transcei!er with in!erting three-state outputs

74#3(

octal $us transcei!er with nonin!erting three-state outputs

74#40

octal $us transcei!er with in!erting three-state outputs

74#41

octal $us transcei!er with nonin!erting open collector outputs

74#42

octal $us transcei!er with in!erting open collector outputs

74#43

octal $us transcei!er with *i o% in!erting and nonin!erting three-state outputs

74#44

octal $us transcei!er with *i o% in!erting and nonin!erting open collector outputs

74#4"

octal $us transcei!er

74#4#

octal $us transcei!er&latch&*ultiple er with nonin!erting three-state outputs

74#47

octal $us transcei!er&latch&*ultiple er with nonin!erting open collector outputs

74#4'

octal $us transcei!er&latch&*ultiple er with in!erting three-state outputs

74#4(

octal $us transcei!er&latch&*ultiple er with in!erting open collector outputs

74#"1

octal $us transcei!er®ister with in!erting three-state outputs

74#"2

octal $us transcei!er®ister with nonin!erting three-state outputs

74#"3

octal $us transcei!er®ister with in!erting three-state and open collector outputs

74#"4

octal $us transcei!er®ister with nonin!erting three-state and open collector outputs

74#"'

octal $us transcei!er with 2arit,9 in!erting

74#"(

octal $us transcei!er with 2arit,9 nonin!erting

74##4

octal $us transcei!er with 2arit,9 in!erting

74##"

octal $us transcei!er with 2arit,9 nonin!erting

74##'

s,nchronous 4-$it decade Ap&down counter

74##(

s,nchronous 4-$it $inar, Ap&down counter

74#70

4 $, 4 register >ile with three-state outputs

74#71

4-$it $idirectional shi%t register&latch &*ultiple er with three-state outputs

74#72

4-$it $idirectional shi%t register&latch&*ultiple er with three-state outputs

74#73

1#-$it serial-in serial-out shi%t register with output storage registers9 three-state outputs

74#74

1#-$it parallel-in serial-out shi%t register with three-state outputs

74#77

1#-$it address co*parator with ena$le

74#7'

1#-$it address co*parator with latch

74#7(

12-$it address co*parator with latch

74#'0

12-$it address co*parator with ena$le

74#'1

4-$it parallel $inar, accu*ulator

74#'2

'-$it *agnitude co*parator

74#'3

'-$it *agnitude co*parator with open collector outputs

74#'4

'-$it *agnitude co*parator

74#'"

'-$it *agnitude co*parator with open collector outputs

74#'#

'-$it *agnitude co*parator with ena$le

74#'7

'-$it *agnitude co*parator with ena$le

74#''

'-$it equalit, co*parator

74#'(

'-$it *agnitude co*parator with open collector outputs

74#(0

three state outputs

74#(1

4-$it $inar, counter&latch&*ultiple er with as,nchronous reset9 three-state outputs

74#(2

4-$it deci*al counter&latch&*ultiple er with s,nchronous reset9 three-state outputs

74#(3

4-$it $inar, counter&latch&*ultiple er with s,nchronous reset9 three-state outputs

74#(4

4-$it deci*al counter&latch&*ultiple er with s,nchronous and as,nchronous resets9 threestate outputs

74#("

4-$it $inar, counter&latch&*ultiple er with s,nchronous and as,nchronous resets9 threestate outputs

74#(#

4-$it deci*al counter®ister&*ultiple er with as,nchronous reset9 three-state outputs

74#(7

4-$it $inar, counter®ister&*ultiple er with as,nchronous reset9 three-state outputs

74#('

4-$it deci*al counter®ister&*ultiple er with s,nchronous reset9 three-state outputs

74#((

4-$it $inar, counter®ister&*ultiple er with s,nchronous reset9 three-state outputs

7471#

progra**a$le decade counter

7471'

progra**a$le $inar, counter

74724

!oltage controlled *ulti!i$rator

74740

octal $u%%er&8ine dri!er9 in!erting9 three-state outputs

74741

octal $u%%er&8ine dri!er9 nonin!erting9 three-state outputs9 *i ed ena$le polarit,

74744

octal $u%%er&8ine dri!er9 nonin!erting9 three-state outputs

7474'

' to 3-line priorit, encoder

7477(

'-$it $idirectional $inar, counter -3-state.

747'3

s,nchronous address *ultiple er

747(0

error detection and correction -EDA0.

747(4

'-$it register with read$ac:

747("

octal $u%%er with three-state outputs

747(#

octal $u%%er with three-state outputs

747(7

octal $u%%er with three-state outputs

747('

octal $u%%er with three-state outputs

74'04

he 2-input NAND dri!ers

74'0"

he 2-input NOR dri!ers

74'0'

he 2-input AND dri!ers

74'32

he 2-input OR dri!ers

74'4'

' to 3-line priorit, encoder with three-state outputs

74'73

octal transparent latch

74'74

octal d-t,pe %lip-%lop

74'7#

octal d-t,pe %lip-%lop with in!erting outputs

74'7'

dual 4-$it d-t,pe %lip-%lop with s,nchronous clear9 nonin!erting three-state outputs

74'7(

dual 4-$it d-t,pe %lip-%lop with s,nchronous clear9 in!erting three-state outputs

74''0

octal transparent latchwith in!erting outputs

74''1

arith*etic logic unit

74''2

32-$it loo:ahead carr, generator

74'''

'-$it slice processor

74(01

he in!erting CC8 $u%%er

74(02

he non-in!erting CC8 $u%%er

74(03

he in!erting 0@O) $u%%er

74(04

he non-in!erting 0@O) $u%%er

74(0"

12-/it successi!e appro i*ation register

74(0#

he open drain n-channel $u%%ers

74(07

he open drain p-channel $u%%ers

74(0'

dual 0@O) 30F rela, dri!er

74(0(

quad !oltage co*parator

74(10

2"# 1 0@O) static RA@

74(11

4 digit e panda$le displa, controller

74(12

# digit /0D displa, controller and dri!er

74(14

he sch*itt trigger with e tended input !oltage

74(1"

se!en seg*ent to /0D decoder

74(17

# digit 3e displa, controller and dri!er

74(1'

dual 0@O) 30F rela, dri!er

74(20

2"# 4 0@O) static RA@

74(21

2"# 4 0@O) static RA@

74(22

1#-:e, encoder

74(23

20-:e, encoder

74(2"

4-digit counter&displa, dri!er

74(2#

4-digit counter&displa, dri!er

74(27

4-digit counter&displa, dri!er

74(2'

4-digit counter&displa, dri!er

74(2(

1024 1 0@O) static RA@

74(30

1024 1 0@O) static RA@

74(32

phase co*parator

74(33

address $us co*parator

74(34

GAD00'2( AD09 see corresponding N)0 datasheet

74(3"

3+"-digit digital !olt*eter -DF@. support chip %or *ultiple ed 7-seg*ent displa,s

74(3#

3+7"-digit digital !olt*eter -DF@. support chip %or *ultiple ed 7-seg*ent displa,s

74(37

GAD03"11 AD09 see corresponding N)0 datasheet

74(3'

GAD03711 AD09 see corresponding N)0 datasheet

74(41

octal $us&line dri!ers&line recei!ers

74(4"

4 digit up&down counter with decoder and dri!er

74(47

4 digit up&down counter with decoder and dri!er

74(4'

GAD00'1# AD09 see corresponding N)0 datasheet

74(4(

GAD00'0' AD09 see corresponding N)0 datasheet

74(4(

GAD00'0' AD09 see corresponding N)0 datasheet

74100"

he in!erting $u%%er with open-collector output

74103"

he nonin!erting $u%%ers with open-collector outputs

742(#0

error detection and correction -EDA0.

742(#1

edac $us $u%%er9 in!erting

742(#2

edac $us $u%%er9 nonin!erting

742(#'

d,na*ic *e*or, controller

742(#(

*e*or, ti*ing controller %or use with EDA0

742(70

*e*or, ti*ing controller %or use without EDA0

741G320'

single 3 input OR-AND GateH

744002

dual 4-input NOR gate

74401"

dual 4-$it shi%t registers

744017

"-stage I10 6ohnson counter

744020

14-stage $inar, counter

744024

7 stage ripple carr, $inar, counter

74402'

/0D to deci*al decoder

744040

12-stage $inar, ripple counter

74404#

phase-loc:ed loop and !oltage-controlled oscillator

74404(

he in!erting $u%%er

7440"0

he $u%%er&con!erter -non-in!erting.

7440"1

high-speed 0@O) '-channel analog *ulitple er&de*ultiple er

7440"2

dual 4-channel analog *ultiple er&de*ultiple ers

7440"3

triple 2-channel analog *ultiple er&de*ultiple ers

7440"(

progra**a$le di!ide-$,-N counter

7440#0

14-stage $inar, ripple counter with oscillator

7440##

quad $ilateral switches

7440#7

1#-channel analog *ultiple er&de*ultiple er

74407"

triple 3-input OR gate

74407'

'-input OR&NOR gate

7440(4

'-$it three-state shi%t register&latch

74431#

quad analog switch

744"11

/0D to 7-seg*ent decoder

744"20

dual 4-$it s,nchronous $inar, counter

744"3'

dual retriggera$le precision *onosta$le *ulti!i$rator

747007

he $u%%er

7472##

quad 2-input ;NOR gate

742('41

10-$it $us-inter%ace D-t,pe latch with 3-state outputs

7440103

presetta$le '-$it s,nchronous down counter

744010"

4-$it $, 1#-word >1>O register

You might also like

- Digital Ic ListDocument24 pagesDigital Ic ListCosmin PavelNo ratings yet

- List of 7400 Series Integrated CircuitsDocument41 pagesList of 7400 Series Integrated CircuitsmanikandanNo ratings yet

- List of 7400 Series Integrated Circuits-2003Document7 pagesList of 7400 Series Integrated Circuits-2003Kalisetty SureshNo ratings yet

- Lista Dos CIs TTLDocument14 pagesLista Dos CIs TTLAgna De Oliveira SilvaNo ratings yet

- 7400 SeriesDocument16 pages7400 Seriespeeyush_tapadiyaNo ratings yet

- Listado 74xx SeriesDocument18 pagesListado 74xx SeriesCarlos Andrés Portilla CalderónNo ratings yet

- IC 74 FamilyDocument12 pagesIC 74 FamilyFlavio Cabrera-MoraNo ratings yet

- Digital Logic TTLDocument3 pagesDigital Logic TTLvincentho2kNo ratings yet

- IC'SDocument4 pagesIC'SDanish MughalNo ratings yet

- Ic Details of 74 Ic'sDocument3 pagesIc Details of 74 Ic'sRakesh Kumar D100% (1)

- CD4000 FunctionsDocument3 pagesCD4000 FunctionsAl MarghNo ratings yet

- 74xx IC'sDocument8 pages74xx IC'skarthikeyan bNo ratings yet

- Familia 7400 TTLDocument4 pagesFamilia 7400 TTLCristhian AmpudiaNo ratings yet

- Logic IC ListDocument5 pagesLogic IC ListdharamNo ratings yet

- Icslist NamesDocument10 pagesIcslist NamesKristin ChavezNo ratings yet

- Tabla de Compuertas CMOSDocument2 pagesTabla de Compuertas CMOSafgr1990No ratings yet

- TTL Texas Instruments: 7400 Series Integrated CircuitsDocument14 pagesTTL Texas Instruments: 7400 Series Integrated CircuitsRickey Castillo ValenzuelaNo ratings yet

- List of 7400 Series Integrated Circuits - Wikipedia, The Free EncyclopediaDocument11 pagesList of 7400 Series Integrated Circuits - Wikipedia, The Free EncyclopediaHermes Heli Retiz AlvarezNo ratings yet

- LIST OF ICsDocument14 pagesLIST OF ICsAbhishek ThakurNo ratings yet

- 74xx SeriesDocument3 pages74xx SeriesfernandofortunaNo ratings yet

- Equivalente TTL A Cmo'sDocument12 pagesEquivalente TTL A Cmo'steddyz50No ratings yet

- 4000 Series Ic's ListDocument4 pages4000 Series Ic's ListSyed Zulqadar HassanNo ratings yet

- Elektor PDFDocument13 pagesElektor PDFpoetaenator100% (2)

- LogicDocument21 pagesLogichemanthbbcNo ratings yet

- List of Instigated CircuitDocument25 pagesList of Instigated CircuitHardik100% (1)

- List of 7400 Series Integrated CircuitsDocument13 pagesList of 7400 Series Integrated CircuitsSalvador Flores TorresNo ratings yet

- 74 Series IC Data Sheet IndexDocument5 pages74 Series IC Data Sheet Indexkranthikiran211No ratings yet

- Pinagen e Descriçao Dos CI'sDocument15 pagesPinagen e Descriçao Dos CI'sjoelcoxa2014No ratings yet

- The Following Is A List of 7400 Series Digital Logic Integrated CircuitsDocument13 pagesThe Following Is A List of 7400 Series Digital Logic Integrated Circuitsmessage4guruNo ratings yet

- 74-Series IC DatasheetsDocument6 pages74-Series IC DatasheetsHabtamu GetaNo ratings yet

- List of 7400 SeriesDocument13 pagesList of 7400 Seriesawais_uetpkNo ratings yet

- These Documents Are in PDF Format, So May Take A While To AppearDocument4 pagesThese Documents Are in PDF Format, So May Take A While To Appeartomi tintiaNo ratings yet

- These Documents Are in PDF Format, So May Take A While To AppearDocument4 pagesThese Documents Are in PDF Format, So May Take A While To Appeartomi tintiaNo ratings yet

- Cmos Ic 핀 배치도: AppendixDocument14 pagesCmos Ic 핀 배치도: AppendixDavid AndersonNo ratings yet

- 7400 and 4000 SeriesDocument44 pages7400 and 4000 SeriesIljas IljaziNo ratings yet

- Integrisana Kola: Sn74Xx SelekcijaDocument10 pagesIntegrisana Kola: Sn74Xx SelekcijaСрећко Минић100% (1)

- 7400 Series Ic's ListDocument13 pages7400 Series Ic's ListSyed Zulqadar HassanNo ratings yet

- IC 74XX SeriesDocument34 pagesIC 74XX SeriesSandeep MishraNo ratings yet

- Tabla de Compuertas CMOSDocument2 pagesTabla de Compuertas CMOSPaola LorenzattoNo ratings yet

- HCF 4000B, 4500B, 40100B Standard SeriesDocument3 pagesHCF 4000B, 4500B, 40100B Standard SeriesMallickarjunaNo ratings yet

- List of 7400 Series Integrated Circuits: From Wikipedia, The Free EncyclopediaDocument13 pagesList of 7400 Series Integrated Circuits: From Wikipedia, The Free EncyclopediaGeovani NascimentoNo ratings yet

- IC DescriptionDocument4 pagesIC Descriptionraja viriyalaNo ratings yet

- 74Ls Series: Lower Power Schottky Low Power SchottkyDocument1 page74Ls Series: Lower Power Schottky Low Power SchottkyFrancisco JuarezNo ratings yet

- List of 7400 Series Integrated CircuitsDocument21 pagesList of 7400 Series Integrated CircuitsTyson Scott100% (1)

- Digital IC List AlllllDocument3 pagesDigital IC List AlllllDeepa DevarajNo ratings yet

- 7400Document18 pages7400Isaac Lara VasquezNo ratings yet

- 74 Series ICsDocument13 pages74 Series ICsKishan PrajapatiNo ratings yet

- Dispositivos TTLDocument1 pageDispositivos TTLMarcelo de PaulaNo ratings yet

- 7400 Series List ICDocument9 pages7400 Series List ICKirbs VirtucioNo ratings yet

- TTL 7400 Series List PDFDocument13 pagesTTL 7400 Series List PDFLuis Fernando Garcia S100% (1)

- Digital ICDocument5 pagesDigital ICacidreignNo ratings yet

- TTL Ic Inventory: IC Number Quantity NameDocument1 pageTTL Ic Inventory: IC Number Quantity Namesgu60775No ratings yet

- List Active Parts, TAMU ECE Equipment RoomDocument5 pagesList Active Parts, TAMU ECE Equipment RoomWilliam HuangNo ratings yet

- List of 7400 Series Integrated CircuitsDocument15 pagesList of 7400 Series Integrated CircuitssansureNo ratings yet

- Electronic Circuit Design Ideas: Edn Series for Design EngineersFrom EverandElectronic Circuit Design Ideas: Edn Series for Design EngineersRating: 5 out of 5 stars5/5 (2)

- Print DirectDocument4 pagesPrint Directapi-3849768100% (3)

- Language ResearchDocument8 pagesLanguage ResearchEditha BallesterosNo ratings yet

- Proficient in TSA - English Assessment Papers Primary 5 ListeningDocument13 pagesProficient in TSA - English Assessment Papers Primary 5 ListeningcocoyipNo ratings yet

- 01 - 7-Class - Maths - Bridge Program - Atp NCS - 1-23Document23 pages01 - 7-Class - Maths - Bridge Program - Atp NCS - 1-23Rita TripathiNo ratings yet

- Distance Exdcu PDFDocument431 pagesDistance Exdcu PDFShakeel AhmadNo ratings yet

- Graph QL Spring BootDocument28 pagesGraph QL Spring BootBilel WARDIENENo ratings yet

- BS Manual r18 - PDFDocument163 pagesBS Manual r18 - PDFAkkonduru KumarNo ratings yet

- Love and Law - Hegel's Critique of MoralityDocument41 pagesLove and Law - Hegel's Critique of MoralityArthur Almeida100% (1)

- Kim SeonDocument6 pagesKim SeonHarly Joe Baguna100% (1)

- ALC APA Referencing Guide T1 2019 FinalDocument97 pagesALC APA Referencing Guide T1 2019 FinalAnish AmatyaNo ratings yet

- VB5 Cracking With SmartCheck 5.0 PDFDocument5 pagesVB5 Cracking With SmartCheck 5.0 PDFSanjay PatilNo ratings yet

- Lecture 6: Modules 6.1-6.10 Web Server Security CSE 628/628ADocument23 pagesLecture 6: Modules 6.1-6.10 Web Server Security CSE 628/628AHarpreet SinghNo ratings yet

- 1st Test 1st Term 14-15 3LPhDocument3 pages1st Test 1st Term 14-15 3LPhjjjamelbNo ratings yet

- Verbs ListDocument2 pagesVerbs Listfabian.paez1983No ratings yet

- Simple Past Tense With Regular Verbs Esl Exercise Worksheet For KidsDocument2 pagesSimple Past Tense With Regular Verbs Esl Exercise Worksheet For KidsPatry sanchezNo ratings yet

- Aj Sik Mitran Di Vadheri AyDocument4 pagesAj Sik Mitran Di Vadheri Ayshahzadmaqsood81No ratings yet

- Smiga Review Irony CBQDocument3 pagesSmiga Review Irony CBQlionalon6No ratings yet

- MAPEH Dynamics LPDocument5 pagesMAPEH Dynamics LPJhon Allenn BulawanNo ratings yet

- Matthew 8Document26 pagesMatthew 8Mark Vincent RamaNo ratings yet

- Shrek EssayDocument3 pagesShrek Essayjonny1011995No ratings yet

- African Traditional Concept of GodDocument18 pagesAfrican Traditional Concept of GodESTHER OGODONo ratings yet

- White Paper Introduction To XtremIO Snapshots H13035Document30 pagesWhite Paper Introduction To XtremIO Snapshots H13035lahsivlahsivNo ratings yet

- WEEK 7 - in The PastDocument5 pagesWEEK 7 - in The PastJessica ChaiNo ratings yet

- Polaris Office Enterprise App 5.0 - UserGuide - Android - 1005Document72 pagesPolaris Office Enterprise App 5.0 - UserGuide - Android - 1005bobby carsonNo ratings yet

- The House Cat Direct Method Activities Reading Comprehension Exe 112330Document3 pagesThe House Cat Direct Method Activities Reading Comprehension Exe 112330Yolanda Vilchez0% (1)

- Evaluaci On de La Toxicidad de Mezclas Binarias de Cobre, Cinc y Ars Enico Sobre Daphnia Obtusa (Kurz, 1874) (Cladocera, Crustacea)Document9 pagesEvaluaci On de La Toxicidad de Mezclas Binarias de Cobre, Cinc y Ars Enico Sobre Daphnia Obtusa (Kurz, 1874) (Cladocera, Crustacea)Maria AliagaNo ratings yet

- FABM 1 Learning PlanDocument33 pagesFABM 1 Learning PlanGladys Angela ValdemoroNo ratings yet

- Comparing Places StudentDocument3 pagesComparing Places Studentisabel medinaNo ratings yet

- Build Your Own Website A Comic Guide To HTML, CSS and WordpressDocument266 pagesBuild Your Own Website A Comic Guide To HTML, CSS and Wordpresstrung_tien_dat100% (1)

- Categorical SyllogismDocument11 pagesCategorical SyllogismCj GuerreroNo ratings yet