Professional Documents

Culture Documents

Fa Structure Modelling

Uploaded by

dineshvhaval0 ratings0% found this document useful (0 votes)

4 views3 pagesThis document contains VHDL code for implementing a full adder using a structural modeling approach. It defines the full adder entity with inputs In1, In2, and c_in and outputs sum and c_out. The architecture instantiates two half adder components and one OR gate component, and maps the inputs and outputs to implement the full adder functionality. It also provides the code for the half adder and OR gate components.

Original Description:

f

Copyright

© Attribution Non-Commercial (BY-NC)

Available Formats

DOCX, PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentThis document contains VHDL code for implementing a full adder using a structural modeling approach. It defines the full adder entity with inputs In1, In2, and c_in and outputs sum and c_out. The architecture instantiates two half adder components and one OR gate component, and maps the inputs and outputs to implement the full adder functionality. It also provides the code for the half adder and OR gate components.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

4 views3 pagesFa Structure Modelling

Uploaded by

dineshvhavalThis document contains VHDL code for implementing a full adder using a structural modeling approach. It defines the full adder entity with inputs In1, In2, and c_in and outputs sum and c_out. The architecture instantiates two half adder components and one OR gate component, and maps the inputs and outputs to implement the full adder functionality. It also provides the code for the half adder and OR gate components.

Copyright:

Attribution Non-Commercial (BY-NC)

Available Formats

Download as DOCX, PDF, TXT or read online from Scribd

You are on page 1of 3

0

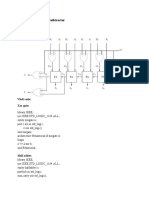

VHDL Code for Full Adder using Structural Modelling

library IEEE; use IEEE.std_logic_1164.all;

entity bejoy_fa is port(In1,In2,c_in : in std_logic; sum, c_out : out std_logic); end bejoy_fa;

architecture arc of bejoy_fa is

component half_adder port(a,b : in std_logic; sum, carry : out std_logic); end component;

component or_2 port(a,b : in std_logic; c : out std_logic); end component;

signal s1, s2, s3 : std_logic;

begin

H1: half_adder port map(a=>In1, b=>In2, sum=>s1, carry=>s3);

H2: half_adder port map(a=>s1, b=>c_in, sum=>sum, carry=>s2);

O1: or_2 port map(a=> s2, b=>s3, c=>c_out);

end arc;

entity half_adder is

port (a,b : in bit ; sum,carry : out bit);

end half_adder;

architecture arc of half_adder is

begin

sum<= a xor b; carry <= a and b;

end arc;

entity or_2 is

port (a,b : in bit ; c : out bit);

end or_2;

architecture arc of or_2 is

begin

c<= a or b;

end arc;

You might also like

- Ee529 Lab Asg4Document10 pagesEe529 Lab Asg4dd23015No ratings yet

- VHDL ProjectDocument14 pagesVHDL ProjectTanveer ShaikhNo ratings yet

- VHDL BasicsDocument21 pagesVHDL BasicsPriya PriyaNo ratings yet

- Exp No: 01 Verification of Logic Gates AimDocument54 pagesExp No: 01 Verification of Logic Gates AimDivya ChanduriNo ratings yet

- VHDL Code For Halfadder: - Logic - XorDocument30 pagesVHDL Code For Halfadder: - Logic - XorAnushNo ratings yet

- HALF ADDER VHDL CODEDocument8 pagesHALF ADDER VHDL CODEAnkit BhardwajNo ratings yet

- Design Half Adder Using VHDLDocument14 pagesDesign Half Adder Using VHDLAmit SahaNo ratings yet

- VHDL Lab FileDocument48 pagesVHDL Lab FileAnkit Gupta100% (1)

- Sol Ex010 11-Sã©rie2Document6 pagesSol Ex010 11-Sã©rie2cncr87kffkNo ratings yet

- Library IEEE Use IEEE - STD - LOGIC - 1164.ALLDocument4 pagesLibrary IEEE Use IEEE - STD - LOGIC - 1164.ALLJaspreet KaurNo ratings yet

- HDL Experiment2Document4 pagesHDL Experiment2choudharyarjun1121No ratings yet

- Experiment 6: Adder/subtractor Block Diagram:: VHDL Code: Xor GateDocument7 pagesExperiment 6: Adder/subtractor Block Diagram:: VHDL Code: Xor Gatepadmavasavi1973No ratings yet

- VHDL Sample PtogramsDocument40 pagesVHDL Sample PtogramsShanmuga PriyaNo ratings yet

- Register-Transfer Level Design Register-Transfer Level (RTL) Is A Design Abstraction Which Models A Synchronous DigitalDocument11 pagesRegister-Transfer Level Design Register-Transfer Level (RTL) Is A Design Abstraction Which Models A Synchronous Digitalmuru54321No ratings yet

- VHDL Code For Carry Save AdderDocument6 pagesVHDL Code For Carry Save AdderAnishkumar Ayyaswamy50% (2)

- ContohVHDL PartI II TugasDocument55 pagesContohVHDL PartI II TugasLuthfiyah13No ratings yet

- VHDL ReportDocument29 pagesVHDL ReportSalman AliNo ratings yet

- VHDL Code For BEHAVIORAL Model of Full AdderDocument2 pagesVHDL Code For BEHAVIORAL Model of Full AdderPavi EceNo ratings yet

- VHDL Code For ALUDocument26 pagesVHDL Code For ALUKirthika Vinoth KumarNo ratings yet

- Comparateur 1bit StructurelleDocument5 pagesComparateur 1bit StructurelleMohamed ChamessNo ratings yet

- Module 1 - Part 4 - Gate Level ExampleDocument8 pagesModule 1 - Part 4 - Gate Level ExampleJaspar Vinitha Sundari TNo ratings yet

- L7 Slides 2Document40 pagesL7 Slides 2Amit SahaNo ratings yet

- VHDL 4-bit Adder with Full Adder ComponentsDocument1 pageVHDL 4-bit Adder with Full Adder ComponentsKato PinderNo ratings yet

- VHDL Programming PDFDocument45 pagesVHDL Programming PDFA B Shinde100% (2)

- SRIHARI Lab8Document7 pagesSRIHARI Lab8srihari kempadalNo ratings yet

- HDL Lab Manual VTUDocument63 pagesHDL Lab Manual VTUSyed MisbahNo ratings yet

- CAS 8 CodeDocument3 pagesCAS 8 Codebhslegion1498No ratings yet

- LabDocument4 pagesLabSouvik PalNo ratings yet

- VhdlfileDocument7 pagesVhdlfileNaveen NegiNo ratings yet

- Code:: EXP.1 Title: Write A VHDL Code To Implement of All Logic GatesDocument7 pagesCode:: EXP.1 Title: Write A VHDL Code To Implement of All Logic GatesChandramouli HaldarNo ratings yet

- VHDL Code For Half Adder by Data Flow ModellingDocument14 pagesVHDL Code For Half Adder by Data Flow ModellingPrateekKumar96% (24)

- VHDL Codes for Logic Gates and Sequential CircuitsDocument42 pagesVHDL Codes for Logic Gates and Sequential CircuitsNaresh KumarNo ratings yet

- Coding:: VHDL Code For BufferDocument27 pagesCoding:: VHDL Code For BufferAar Kay GautamNo ratings yet

- VHDL Unit - 1Document10 pagesVHDL Unit - 1hemanthperreddy123No ratings yet

- MohamedSamir AssignmentDocument45 pagesMohamedSamir Assignmentmohamed samierNo ratings yet

- INFORME PRACTICA No 2Document30 pagesINFORME PRACTICA No 2MAURICIO REYES ROSERONo ratings yet

- VHDL ManualDocument19 pagesVHDL ManualDr.B.Krishna KumarNo ratings yet

- HDL Lab ManualDocument29 pagesHDL Lab ManualRaveen GulipuraNo ratings yet

- Half Adder-1 PDFDocument5 pagesHalf Adder-1 PDFر' حيلNo ratings yet

- CALab - Jalish BuktawarDocument19 pagesCALab - Jalish BuktawarSouvik PalNo ratings yet

- Wa0000.Document35 pagesWa0000.KARTAVYANo ratings yet

- FA HA Comp CodeDocument2 pagesFA HA Comp Codebhslegion1498No ratings yet

- UNIT-3: Design Combinational CKT Using Architecture ModelDocument36 pagesUNIT-3: Design Combinational CKT Using Architecture Modelankit_4382No ratings yet

- EECS 318 CAD - The VHDL N-bit AdderDocument21 pagesEECS 318 CAD - The VHDL N-bit AdderSiva RamNo ratings yet

- 1-bit and 5-bit Full Adder VHDL CodeDocument1 page1-bit and 5-bit Full Adder VHDL CodeJose Montiel PulidoNo ratings yet

- Adder CompoDocument4 pagesAdder Compobhslegion1498No ratings yet

- Deber Digitales Nombre: Jossuet Farfan A. Codigo VHDLDocument7 pagesDeber Digitales Nombre: Jossuet Farfan A. Codigo VHDLJossuet GallagherNo ratings yet

- 09 VHDL Component InstantiationsDocument7 pages09 VHDL Component InstantiationsOmnipotent yayNo ratings yet

- VHDL Code For Full AdderDocument5 pagesVHDL Code For Full AdderVinod Kumarrockz100% (1)

- EE-307 Combinational Logic in Verilog LectureDocument19 pagesEE-307 Combinational Logic in Verilog LectureMuhammad AnasNo ratings yet

- Vlsi Lab PgmsDocument18 pagesVlsi Lab PgmsLavanya ViswanathanNo ratings yet

- Computer Architecture Lab: Name - Roll - 12100119111 Section - (B) Computer Science EngineeringDocument71 pagesComputer Architecture Lab: Name - Roll - 12100119111 Section - (B) Computer Science EngineeringSankhadeep ChakrabartiNo ratings yet

- Dataflow Modelling Logic Gates and Circuits in VHDLDocument31 pagesDataflow Modelling Logic Gates and Circuits in VHDLvtechvishnuNo ratings yet

- EC0324 VLSI Lab Manual - LatestDocument62 pagesEC0324 VLSI Lab Manual - LatestAshwin RajaratnamNo ratings yet

- VHDL ProgramDocument5 pagesVHDL ProgramJaswanth TejaNo ratings yet

- Digital Circuits & Systems - Ii Lab ETEC 351: Maharaja Agrasen Institute of TechnologyDocument16 pagesDigital Circuits & Systems - Ii Lab ETEC 351: Maharaja Agrasen Institute of Technologysandeepdaiya45gmailcNo ratings yet

- 16:1 MUX using 2:1 MUXDocument15 pages16:1 MUX using 2:1 MUXGaurav DuggalNo ratings yet

- Projects With Microcontrollers And PICCFrom EverandProjects With Microcontrollers And PICCRating: 5 out of 5 stars5/5 (1)

- 7-Zip ReadmeDocument1 page7-Zip ReadmeExcellence ٹیچرNo ratings yet

- Ace Circuit BuilderDocument186 pagesAce Circuit BuilderBráulio SoaresNo ratings yet

- Ace Circuit BuilderDocument186 pagesAce Circuit BuilderBráulio SoaresNo ratings yet

- Ace Circuit BuilderDocument186 pagesAce Circuit BuilderBráulio SoaresNo ratings yet

- Adobe IDDocument1 pageAdobe IDzornitca378_23032348No ratings yet

- PDFSigQFormalRep PDFDocument1 pagePDFSigQFormalRep PDFJim LeeNo ratings yet

- Lecture Week6Document62 pagesLecture Week6dineshvhavalNo ratings yet

- Maharashtra Govt Job Seeker Registration SlipDocument1 pageMaharashtra Govt Job Seeker Registration SlipdineshvhavalNo ratings yet

- Chapter 3.10: Energy Efficient Technologies in Electrical SystemsDocument8 pagesChapter 3.10: Energy Efficient Technologies in Electrical SystemsdineshvhavalNo ratings yet

- Ej Sem5Document43 pagesEj Sem5dineshvhavalNo ratings yet

- Design InfluenceDocument80 pagesDesign InfluenceSelva RamNo ratings yet

- HistoryDocument18 pagesHistoryBắp NgọtNo ratings yet

- Interfacing Seven Segment Display To 8051: Electronic Circuits and Diagram-Electronics Projects and DesignDocument18 pagesInterfacing Seven Segment Display To 8051: Electronic Circuits and Diagram-Electronics Projects and DesigndineshvhavalNo ratings yet

- Introduction of IGBT Bas... Ngle Phase PWM InverterDocument5 pagesIntroduction of IGBT Bas... Ngle Phase PWM InverterdineshvhavalNo ratings yet

- Cen 012014 Appform Annextures Railway 1Document7 pagesCen 012014 Appform Annextures Railway 1dineshvhavalNo ratings yet

- Microprocessor and Microcontroller: Lecture NotesDocument32 pagesMicroprocessor and Microcontroller: Lecture NotesdineshvhavalNo ratings yet

- Lab 4Document4 pagesLab 4dineshvhavalNo ratings yet

- Maharashtra Govt Job Seeker Registration SlipDocument1 pageMaharashtra Govt Job Seeker Registration SlipdineshvhavalNo ratings yet

- Best AnswerDocument2 pagesBest AnswerdineshvhavalNo ratings yet

- Lesson 9Document11 pagesLesson 9dineshvhavalNo ratings yet

- Microprocessor and Microcontroller: Lecture NotesDocument32 pagesMicroprocessor and Microcontroller: Lecture NotesdineshvhavalNo ratings yet

- D Safra Z 004628Document4 pagesD Safra Z 004628dineshvhavalNo ratings yet

- 8051 ExplainedDocument16 pages8051 ExplainedApurva DesaiNo ratings yet

- Programming and Interfacing the 8051 MicrocontrollerDocument6 pagesProgramming and Interfacing the 8051 MicrocontrollerSAKETSHOURAVNo ratings yet

- PIC 16f877a Data SheetDocument234 pagesPIC 16f877a Data Sheetanon-26401438% (8)

- 8051Document28 pages8051MadhuSquareNo ratings yet

- Chap 14Document41 pagesChap 14vibinmanualNo ratings yet

- MicroC2 eCH03L02MemoryDocument28 pagesMicroC2 eCH03L02MemorydineshvhavalNo ratings yet

- Dsa 0036975Document284 pagesDsa 0036975dineshvhavalNo ratings yet

- Using The PIC Devices' SSP and MSSP Modules For Slave I2C CommunicationDocument20 pagesUsing The PIC Devices' SSP and MSSP Modules For Slave I2C CommunicationthelutheranknightNo ratings yet