Professional Documents

Culture Documents

VXL Btot Ay1213-S2

Uploaded by

Nguyên Phong0 ratings0% found this document useful (0 votes)

10 views8 pagesbài tập ôn thi cuối kì vi xử lý

Original Title

Vxl Btot Ay1213-s2

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this Documentbài tập ôn thi cuối kì vi xử lý

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

10 views8 pagesVXL Btot Ay1213-S2

Uploaded by

Nguyên Phongbài tập ôn thi cuối kì vi xử lý

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 8

VXL _BTOT_AY1213-S21/8

HBK Tp HCM Khoa T

BMT

GVPT: H Trung M

Bi tp n thi hc k Mn hc: Vi x l AY1213-S2

Ch :

Trong cc bi tp sau gi s dng 8051 vi thch anh (XTAL) l 12 MHz

H thng s c du l h thng c s m c biu din bng s b 2.

Khi bi ch ni vit chng trnh th ngm hiu l vit bng hp ng 8051.

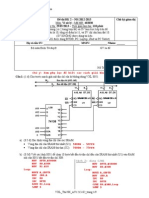

1) Cho trc mch gii m a ch ca h thng dng VXL 8051:

a) Xc nh vng a ch ca cc SRAM

b) Vit cc lnh 8051 sao chp 10 byte t vng nh c a ch u l a ch u ca SRAM th nht

(U1) n vng nh c a ch u l a ch u ca l a ch u ca SRAM th hai (U2)

2) Cho trc mch giao tip 8051 vi SRAM 4KB:

VXL _BTOT_AY1213-S22/8

a) Vit on chng trnh sao chp 10 byte t b nh chng trnh bt u t a ch 0100H n SRAM

bt u t a ch 0240H bng MOVX vi: i) DPTR, v ii) R0.

b) Thay v dng chn ALE ni vo chn LE mch cht, ngi ta ni chn P3.0 n chn LE ca mch

cht. Khi hy vit cc lnh sao chp 1 byte a ch 0375H vo thanh ghi R7.

c) Thay v dng cng P2 ni n cc ng a ch A8A11 ca SRAM, ngi ta dng cng P1 thay cho

cng P2. Khi hy vit cc lnh sao chp 1 byte a ch 0758H vo thanh ghi R7.

3) Thit k mch giao tip b nh cho 8051 vi b nh chng trnh bn ngoi ROM 16KB v b nh d liu

SRAM 32KB u c vng a ch bt u t 0000H. Mch ny c xy dng t 1 IC gii m 74138, 2 ROM

8Kx8 v 4 SRAM 8Kx8.

4) Cho bit ni dung ca thanh ghi A sau khi thc thi mi on chng trnh sau:

(a) (b) (c) (d) (e)

MOV 20h,#75h

MOV R1,#20H

MOV A,@R1

ANL a,#0FH

MOV R1,#2

MOV A,1

ORL A,#40H

XRL A,#0FH

MOV A,#0FFH

CLR C

MOV ACC.7,C

CPL C

MOV ACC.0,C

XRL A,ACC

ADD A,#0F7H

SETB C

MOV R1,#89H

ADDC A,R1

MOV A,#56H

SWAP A

RR A

RR A

5) Cho bit ni dung ca cc thanh ghi A, R0, R1, R2, R3, SP, PC, cc nh trong ROM c a ch l 0001H

v 0A8FH, v cc nh ca RAM ni c a ch l 01H, 02H v 03H sau khi 8051 thc thi lnh add A, R2:

Dng a ch M my Lnh

1 0000 ORG 0

2 0000 020A80 LJMP Start

3 0A80 ORG 0A80H

4 0A80 758170 Start: MOV SP,#70H

5 0A83 7A1C MOV R2,#1CH

6 0A85 7428 MOV A,#28H

7 0A87 78C7 MOV R0,#0C7H

8 0A89 C002 PUSH 2

9 0A8B C000 PUSH 0

10 0A8D 2A ADD A, R2

11 0A8E D001 POP 1

12 0A90 29 ADD A, R1

13 0A91 D000 POP 0

14 0A93 EB MOV A, R3

15 0A94 28 ADD A, R0

16 0A95 80FE SJMP $

17 0A97 END

6) Cho trc bng sau:

a ch

ROM (hex) M my (hex) Lnh 8051

Cch nh a ch ca ton hng

th nht th hai

ORG 0

MOV R0,#30H

MOV R1,#10

CLR A

MOV R2,A

MOV R3,A

Loop: MOV A,@R0

JB ACC.7,Neg

INC R3

SJMP Cont

Neg: INC R2

Cont: INC R0

DJNZ R1,Loop

SJMP $

END

a) in vo cc ch trng trong ct a ch ROM chng trnh, ct m my v ct cc cch a ch.

b) Cho bit on chng trnh trn lm g v vai tr ca cc thanh ghi R0, R1, R2, v R3 l g?

VXL _BTOT_AY1213-S23/8

7) Cho bit ni dung ca SP v RAM ni sau khi thc thi on chng trnh sau:

MOV SP,#49h

MOV R1,#5BH

PUSH 1

ORL 48H,#0A5h

XRL 4AH,#63h

POP 00h

PUSH 48H

a ch

RAM

Trc khi thc thi Sau khi thc thi

SP 07H

4AH 08H

49H 07H

48H 06H

00H 05H

8) Hy cho bit gi tr ca SP v ni dung ca stack sau khi thc thi mi dng lnh sau:

ORG 0BH

LCALL DELAY

SJMP $

ORG 300H

DELAY: MOV R5, #0FFH

AGAIN: DJNZ R5, AGAIN

RET

9) a) Vit chng trnh hp ng sao chp khi d liu 10 byte (ca RAM ngoi) c a ch u l 8020H

n khi d liu (RAM ngoi) c a ch u l 8040H.

b) Vit chng trnh hp ng sao chp khi d liu 10 byte (ca RAM ni) c a ch u l 20H n

khi d liu ( RAM ngoi) c a ch u l 8040H.

10) Hy hon tt chng trnh sau da theo cc ch thch i km ti mi lnh

. . . . . . . ; chng trnh bt u t a ch 100H

start: . . . . . . . ; A 9BH

. . . . . . . ; R0 32H vo thanh ghi A

. . . . . . . ; A A + R0

. . . . . . . ; DPTR 2010H

. . . . . . . ; ct A vo nh 2010H RAM ngoi

here: . . . . . . . ; lp vng ti y

END ; Kt thc chng trnh

11) Vit chng trnh con hp ng hoc C so snh 2 s 8 bit X v Y trong cc thanh ghi R5 v R6 tng

ng. Kt qu so snh c t trong R7 theo quy c sau:

X < Y th R7 = 01H

X = Y th R7 = 02H

X > Y th R7 = 04H

C F0 (trong PSW) dng chn so snh s khng du (khi F0=0) hay c du (khi F0=1).

p dng chng trnh con trn so snh 2 s 16 bit khng du t trong RAM ni vi byte thp a ch

thp, s th nht bt u t a ch 30H v s th hai bt u t 40H.

12) Vit chng trnh con thc hin php ton OR 8 bit thanh ghi A v cho kt qu trong c C vi cc cch

sau:

a) p dng lnh JZ hoc JNZ tm kt qu OR.

b) p dng lnh ORL cho bin Boole

ng dng chng trnh con trn tm:

i) OR 4 bit thp ca cng P1 v kt qu xut ra P1.4

ii) OR 16 bit ca DPTR v kt qu c C.

13) Vit chng trnh con thc hin php ton XOR 8 bit thanh ghi A v cho kt qu trong c C vi cc

cch sau:

a) Tn dng c parity P tm kt qu XOR.

b) m s bit 1 trong thanh ghi A tm kt qu XOR.

ng dng chng trnh con trn tm:

i) XOR 4 bit thp ca cng P1 v kt qu xut ra P1.4

ii) XOR 16 bit ca DPTR v kt qu c C.

14) a) Vit chng trnh con thc hin cng 2 s khng du nhiu byte. Gi s trc khi gi chng trnh con

ny th:

R0 cha a ch u ca ton hng th nht (trng vi a ch ca byte thp nht) N1.

VXL _BTOT_AY1213-S24/8

R1 cha a ch u ca ton hng th hai (trng vi a ch ca byte thp nht) N2.

R2 cha s byte trong mi ton hng (c 2 ton hng c cng chiu di).

Ton hng nhiu byte c trong RAM ni ca 8051 vi sp th t byte theo little endian.

Kt qu ca php tnh c ct li vo cng vng nh ca ton hng 1, ngha l tnh N1 = N1 + N2.

p dng tnh cng 2 ton hng 5 byte c cc a ch u l 20H v 30H.

b) Tng t a) nhng thc hin cng 2 s BCD khng du nhiu byte vi R2 cha tr s 2k (k > 0).

Vit chng trnh con thc hin tr 2 s khng du nhiu byte nhiu byte: N1 = N1 N2.

15) Vit chng trnh con thc hin cc php tnh sau theo ni dung ca thanh ghi R0 (nu R0 >7 th R3 = 0)

R0 Php ton R0 Php ton

0 R3 = R1 + R2 4 R3 = R1 AND R2

1 R3 = R1 R2 5 R3 = R1 OR R2

2 R3 = R1 * R2 6 R3 = R1 XOR R2

3 R3 = R1 / R2

(ch ly thng s)

7 R3 = NOT(R1)

vi cc cch sau:

a) Tn dng lnh CJNE

b) Tn dng lnh JMP @A+DPTR

16) Vit chng trnh bng hp ng hoc C m phng b m ln/xung 8 bit vi ng ra 8 bit cng P2.

B m ny c cc chn iu khin sau:

P0.0 = RESET = khi c cnh xung chn ny th ng ra P2 l 0. (c u tin cao nht)

P0.1 = UP = khi c cnh xung th gi tr ca P2 c tng thm 1 (c u tin nh)

P0.3 = DOWN = khi c cnh xung th gi tr ca P2 c gim i 1 (c u tin thp nht)

Sa li chng trnh vi chn RESET dng ngt ngoi 0 (/INT0).

17) Tn dng chng trnh (bng hp ng hoc C) m phng b m ln/xung 4 bit ng ra nh phn m

phng b m ln/xung 4 bit c cho php np tr u v tr cui ca b m (gi s gi tr u l 4 bit cao

ca P1 v gi tr cui l 4 bit thp ca P1, gi tr u lun lun nh hn gi tr cui). B m ny c cc chn

iu khin sau:

P0.0 = RESET = khi c cnh xung chn ny th np tr u v cui vo counter cho php tr

bt u m l gi tr u. (c u tin cao nht)

P0.1 = UP = khi c cnh xung th gi tr ca P2 c tng thm 1 (c u tin nh)

P0.3 = DOWN = khi c cnh xung th gi tr ca P2 c gim i 1 (c u tin thp nht)

18) Xt 1 mch 8051 vi cc cng tc: SW1 c ni vi P0.0, SW2 ni vi P0.1; v cc LED c ni:

LED 1 c ni vi P0.2, LED 2 c ni vi P0.3. Gi s LED c V

LED

=2V v I

LED

=10mA. Hy v s

mch v vit chng trnh hp ng hoc C cho mch ny. Qui lut hot ng ca mch nh sau:

P0.1 P0.0 LED 2 LED 1

0 0 Tt Tt

0 1 Tt Sng

1 0 Sng Tt

1 1 Nhp nhy chu k 1s Nhp nhy chu k 1s

ngc pha vi LED 2

19) Cho trc chng trnh con Delay sau:

Delay: MOV R1,#255

L1: MOV R0,#255

L2: DJNZ R0, L2

DJNZ R1, L1

RET

a) Hy ghi ch thch s chu k my (MC) cho mi lnh v t suy ra thi gian tr ca CT con ny.

b) Nu mun lm tr 100 ms th ta phi np cho R1 gi tr l bao nhiu?

c) Hy vit li chng trnh con lm tr 100 ms dng Timer (khng dng ngt Timer).

20) Chng trnh con sau to tr 1 giy vi XTAL=12MHz.

DELAY: MOV R0, #0

MOV R1, #0

MOV R2, #8

LOOP: DJNZ R0, LOOP

DJNZ R1, LOOP

VXL _BTOT_AY1213-S25/8

DJNZ R2, LOOP

RET

a) Nu s dng XTAL = 6MHz th phi sa cc tham s no trong chng trnh trn vn c tr 1 giy?

b) Chng trnh con trn c sai s bao nhiu? Hy sa li chng trn c chnh xc cao nht c th

c.

21) Vit chng trnh to sng vung (T

ON

=T

OFF

) chn P1.1 c tn s theo qui tc sau: 500 Hz nu P1.0 = 0,

100 Hz nu P1.0 = 1.

Phn to thi gian tr c thc hin bng cc cch sau:

a) Bng phn mm (dng DJNZ v NOP nu cn).

b) Bng timer0 khng dng ngt.

c) Bng ngt timer0

22) Thit k mch 8051 c chc nng sau: (SV t chn bt c chn no ca cng I/O cho ng vo iu khin)

Cc ng ra sng ln lt lin tc theo qui lut sau khi ng vo iu khin bng 0

n LED xanh sng trong 5 s trong khi cc n LED khc tt.

n LED vng sng trong 2 s trong khi cc n LED khc tt..

n LED sng trong 8 s trong khi cc n LED khc tt..

Ch c n LED vng sng nhp nhy vi chu k 2 s khi ng vo iu khin bng 1.

23) Cho trc mch sau vi cc chn ra 1Y1 ni vi on a,1Y2 ni vi on b,..,2Y3 ni vi on g ca

LED 7 on cathod chung vi cc R hn dng l 330.

Mch hot ng nh sau: (u tin cao hn P2.0)

Khi c cnh xung P2.0 th hin ln lt t 0 n 9 vi thi gian hin 1 s l 1s v lp li.

Khi c cnh xung P2.1 th hin ln lt t 0 n F vi thi gian hin 1 s l 1s v lp li.

a) Hy vit chng trnh hp ng hoc C cho mch ny.

b) Vit li chng trnh trn dng ngt ngoi 0 v ngt ngoi 1 thay cho cc tn hiu a vo P2.0 v

P2.1.

24) Vit chng trnh tm gi tr ca y (trong thanh ghi R7) bng 2 cch: dng cc lnh MUL v lnh MOVC,

vi gi tr y cn tnh l

a) y = x

2

+ 2x + 5 vi x (trong thanh ghi A) c gi tr t 0 n 9

b) y = x

2

2x + 3 vi x (trong thanh ghi A) c gi tr t 0 n 9

25) Mt mch dng 8051 to hiu ng trn LED vi cc kt ni LED v cng tc/kha nh sau:

Cc LED c ni vo P1.0, P1.1 v P1.2, cn cng tc c ni vo P0.0. Gi s in tr ko ln P0.0

l 10K v cc in tr hn dng cho LED l 330.

Vit chng trnh hp ng hoc C thc hin cng vic sau:

Nu P0.0 = 1 th cc bit P1.2..1.0 c tr nh phn thay i t nh nht n ln nht v lp li (mi

tr c duy tr trong 0.25s).

VXL _BTOT_AY1213-S26/8

Nu P0.0 = 0 th cc bit P1.2..1.0 c tr nh phn thay i t ln nht n nh nht v lp li (mi

tr c duy tr trong 0.25s).

26) Hy thit k mch nhp nhy LED (3 LED vi 3 R hn dng c gn vo cc chn P1.2..P1.0) vi quy

lut sau:

Nu P1.3=0 th P1.2..1.0=000, 001, 010, 011, 100, 101, 110, 111 v lp li (thi gian tr gia 2 s

m l 200ms)

Nu P1.3=1 th P1.2..1.0=000, 001, 011, 010, 110, 111, 101, 100 v lp li (thi gian tr gia 2 s

m l 200ms)

Hy vit chng trnh bng hp ng hoc C cho mch ny.

27) a) Thit k mch dng 8051 m phng b m ln/xung BCD 2 k s vi hin th LED 7 on c dn

knh sau:

Kt ni vi 8051 theo qui c sau:

P1 c ni vi cc chn a n g v dp ca mch hin th LED.

P2.0 v P2.1 c ni vi cc chn /DIGIT1 v /DIGIT2 ca mch hin th LED.

B m ny c cc chn iu khin sau:

P0.0 = RESET = khi c cnh xung chn ny th ng ra P2 l 0. (c u tin cao nht)

P0.1 = UP = khi c cnh xung th gi tr ca P2 c tng thm 1 (c u tin nh)

P0.3 = DOWN = khi c cnh xung th gi tr ca P2 c gim i 1 (c u tin thp nht)

b) Sa li chng trnh a) vi chn RESET dng chn ngt ngoi 0 (/INT0).

28) Thit k mch nh th n gin vi hin th trn LED 7 on (nh mch cu trn) cho thy s m t 0s

n 60s. Mch hot ng theo nguyn tc sau:

Khi c cnh xung tn hiu STOP/RUN (c ni vo chn ngt ngoi /INT0) th s hin th thi

gian t 0 n 60s v lp li (ch RUN), v khi c cnh xung STOP/RUN ln na th n s dng

(ch STOP) vi s hin th ng yn khng tng na.

Sau khi reset h thng th mch ch STOP v hin th 0s.

Hy vit chng trnh hp ng cho mch ny vi nh th 1s dng ngt timer 0 v ch STOP/RUN dng

ngt ngoi /INT0 kch cnh xung.

29) Vit chng trnh hp ng (bng 2 cch: lnh logic vi bin Boole v lnh r nhnh vi bin Boole) hoc

C m phng mch t hp sau (khng cha rt gn hm Boole):

VXL _BTOT_AY1213-S27/8

30) Vit chng trnh hp ng hoc C to sng vung (T

ON

=T

OFF

) chn P2.0. Chu k T ca sng vung

ny ph thuc vo gi tr c c t cng P1, nu tr s c t P1 l N th sng vung c chu k l N ms

(trng hp N = 0 th khng c sng vung u ra).

31) Vit chng trnh to sng vung 125 Hz c chu k nhim v l 25% theo cc cch sau:

a) Khng dng timer

b) Dng timer 0 ch 2 v khng dng ngt timer 0.

c) Dng timer 0 ch 1 v khng dng ngt timer 0.

d) Dng timer 0 ch 2 v dng ngt timer 0.

e) Dng timer 0 ch 1 v dng ngt timer 0.

32) a) Ngi ta dng 1 ngun xung vung 1Hz ni vi chn T0 ca 8051. Vit chng trnh s cp nht cc

bin SS(giy), MM(pht), HH(gi) c t tng ng trong cc nh trong RAM ni ti cc a ch 30H,

31H v 32H. Ni dung ca cc bin l HH, MM, v SS l cc s BCD 2 k s biu din cc gi tr gi (ti a

23H), pht (ti a 59H) v giy (ti a 59H) tng ng. Tn hiu RESET c ni vo chn /INT0, khi c

cnh xung ti /INT0 th cc bin HH, MM, v SS c tr u l 0.

b) Hin th gi, pht, v giy vi b hin th LED 7 on dn knh 6 k s.

c) Hin th gi, pht, v giy vi LCD

33) Cho trc mch giao tip 8051 vi bn phm v chng trnh sau:

MOV P2,#0FH

MOV A,#11110111B

MOV R0,#30H

LOOP:

MOV P1,A

MOV @R0,P2

INC R0

RR A

JB ACC.7,LOOP

Gi s 2 phm s 4 v 2 c nhn ng thi. Hy cho bit ni dung ca cc nh 30H n 33H trong RAM

ni l bao nhiu?

34) Vit chng trnh c t 32 byte t cng ni tip v ct vo 32 byte trong RAM ni t a ch 20H n

3FH. Gi s cng ni tip c tc baud l 4800. Thc hin cng vic bng cc cch sau:

a) Hi vng vi kim tra c RI.

b) Ngt cng ni tip.

35) a ch 200H trong ROM ni (b nh chng trnh) c chui k t (TD: This is a test!) c kt

thc bng k t NULL (=00H). Vit chng trnh chp chui k t ny vo RAM ngoi t a ch 2000H v

ng thi gi ra cng ni tip. Gi s 8051 dng XTAL=11.0592 MHz v cng ni tip c tc baud l

9600. Truyn d liu ra cng ni tip c vit bng 2 cch: hi vng TI v dng ngt ni tip vi TI.

36) a) Mch sau cho thy cch s dng cng ni tip ch thanh ghi dch m rng cng xut ca 8051:

Vit chng trnh xut ni dung ca R2 ra cng xut m rng ny. Gi s cng ni tip c tc baud l 2400

v XTAL = 11.0592 MHz.

VXL _BTOT_AY1213-S28/8

b) Vi mch a), hy ghp thm cc thanh ghi dch 74LS164 c thm 2 cng xut. Hy vit chng

trnh xut 3 byte trong cc nh RAM ni c a ch l 30H, 31H v 32H.

37) Xt 1 h thng gm 2 vi x l 8051 M1 v M2: M1 c nhim v c lin tc cng P1 v xut ni tip n

M2, M2 c nhim v nhn lin tc d liu ni tip v hin th ni dung ca P1 ra 2 LED 7 on c gn vo

cc cng P1 v P2. Th d nu P1 ca M1 c tr l 27H th M2 ta s thy 2 LED 7 on hin th s 27. C 2

VXL u s dng cng ni tip c tc baud l 4800 v XTAL = 11.0592 MHz.

38) a) V mch kt ni 8051 vi LCD (c 2 hng, mi hng 20 k t) dng giao tip d liu 8 bit

b) Vit chng trnh hin th chui Hello the world! hng th nht ca LCD.

c) To hiu ng dch sang tri mi ln 1 k t ca chui k t b). Sau khi dch ht th hin ny chui ny

nh c. Thi gian gia 2 ln dch l 200ms.

d) Xut ra chui Test: hng th 2 v xut tip cc con s cng 1 v tr trn hng 2 cc s t 0 n 9

v lp li, thi gian hin cho 1 s l 1s.

39) Vit chng trnh hp ng hoc C lm sng cc LED n c ni vi cng P1 (hnh trn en tng

ng LED sng v ng ra mc 0 lm LED sng). Nu ng vo P0.0 = 0 th sng theo mu 1 (TD: trc ht ch

c LED P1.0 sng trong 150 ms, k tip ch c LED P1.1 sng trong 150 ms, .., cui cng ch c LED

P1.7 sng trong 150 ms, v lp li) , v P0.0 th sng theo mu 2.

Mu 1 (Cun tri cc LED) Mu 2 (Cun phi cc LED)

a) Hy v s mch.

b) Vit chng trnh hp ng hay C

c) Thay v dng P0.0 iu khin, ta dng kch cnh xung ngt ngoi INT0 v INT1. Khi c ngt

ngoi INT0 th chy LED theo mu 1 v khi c ngt ngoi INT1 th chy LED theo mu 2.Vit chng

trnh hp ng hay C.

40) Hy gii thch chng trnh sau lm g?

#include <reg51.h>

sbit portbit = P1^5;

unsigned char state = 0;

void Timer0(unsigned char times)

{ unsigned char i;

for ( i = 0; i <= times ; i++)

{ TL0 = 100; TR0 = 1;

while (TF0 == 0) ;

TF0 = 0; TR0 = 0 ;

}

}

int main(void)

{

portbit = 1;

TMOD = 2;

while(1)

{

Timer0(state);

state = (state +1) % 4;

portbit = !portbit;

}

}

You might also like

- Tư Tư NG H Chí MinhDocument13 pagesTư Tư NG H Chí MinhNguyên PhongNo ratings yet

- Education Phase I Full ReportDocument28 pagesEducation Phase I Full ReportNguyên PhongNo ratings yet

- Báo Cáo Lập Trình NhúngDocument7 pagesBáo Cáo Lập Trình NhúngNguyên Phong0% (1)

- Ve Mach in Bang ProteusDocument11 pagesVe Mach in Bang ProteusTrần Nguyên HoàngNo ratings yet

- Bao Cao Do Luong Dien TuDocument7 pagesBao Cao Do Luong Dien TuNguyên PhongNo ratings yet

- VXL Thi HK Ay1213-S2 Co Dap AnDocument9 pagesVXL Thi HK Ay1213-S2 Co Dap AnNguyên PhongNo ratings yet

- Bài giản lập phân tích dự ánDocument266 pagesBài giản lập phân tích dự ánMinh Nhut TrinhNo ratings yet

- 408xxx TN BienDoiNangLuong BakDocument2 pages408xxx TN BienDoiNangLuong BakNguyên PhongNo ratings yet

- Mau Bao Cao Thi Nghiem VXL-VDK - 4-2012 - Dien - Dien TuDocument12 pagesMau Bao Cao Thi Nghiem VXL-VDK - 4-2012 - Dien - Dien TuThương Nguyễn VănNo ratings yet

- Giáo+trình+Triết+học+Mác-Lênin+-+Gs Ts Nguyễn+Ngọc+LongDocument214 pagesGiáo+trình+Triết+học+Mác-Lênin+-+Gs Ts Nguyễn+Ngọc+LongFC ChampionNo ratings yet

- Báo cáo thí nghiệm kĩ thuật sốDocument28 pagesBáo cáo thí nghiệm kĩ thuật sốNguyên PhongNo ratings yet

- $7.pt-bpt không mẫu mựcDocument2 pages$7.pt-bpt không mẫu mựcNguyên PhongNo ratings yet