Professional Documents

Culture Documents

I/O Pad Insertion For SOC Encounter: Meng-Kai Hsu EDA Lab Meng Kai Hsu, EDA Lab

I/O Pad Insertion For SOC Encounter: Meng-Kai Hsu EDA Lab Meng Kai Hsu, EDA Lab

Uploaded by

Utkarsh Jain0 ratings0% found this document useful (0 votes)

8 views7 pagesInput output Pad Insertion

Original Title

IO Pad Insertion

Copyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentInput output Pad Insertion

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

8 views7 pagesI/O Pad Insertion For SOC Encounter: Meng-Kai Hsu EDA Lab Meng Kai Hsu, EDA Lab

I/O Pad Insertion For SOC Encounter: Meng-Kai Hsu EDA Lab Meng Kai Hsu, EDA Lab

Uploaded by

Utkarsh JainInput output Pad Insertion

Copyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 7

I/O Pad Insertion for SOC Encounter

Meng-Kai Hsu EDA Lab Meng Kai Hsu, EDA Lab

Gate-Level Netlist

For a chip design the I/O pads should be added on the top For a chip design, the I/O pads should be added on the top

module.

I1

M

I2

O1

CHIP

I1

O1

Pad_I1

Pad O1

M

I2

O1

Pad_I2

_

2

Gate-Level Netlist (Example)

module M (O1, I1, I2);

output O1;

input I1;

input I2;

endmodule;

module M (O1, I1, I2);

t t O1

module CHIP (O1, I1, I2); // top module with I/O pads

output O1;

input I1, I2;

i i I1 i I2 i O1

output O1;

input I1;

input I2;

Endmodule;

wire i_I1, i_I2, i_O1;

M M(.O1(i_O1), .I1(i_I1), .I2(i_I2));

PDIDGZ Pad_I1 (.PAD(I1), .C(i_I1));

PDIDGZ P d i2 ( PAD(I2) C(i I2))

Endmodule;

Original design (M.v)

PDIDGZ Pad_i2 (.PAD(I2), .C(i_I2));

PDO02CDG Pad_O1(.PAD(O1), .I(i_O1));

endmodule;

3

Modified design (CHIP.v)

Gate-Level Netlist (Notes)

Pads PDIDGZ and PDO02CDG are available types for input Pads PDIDGZ and PDO02CDG are available types for input

and output pads, respectively, for tsmc18 process. There are

also other types of I/O pads could be used (please refer to a so ot e types o /O pa s cou e use (p ease e e to

tpz973.v) and for other libraries, different pads might be

used (different names, of course). ( )

For accurate simulation, I/O pads should be also considered

for timing delay assumptions. That is, tpz973.v should be g y p , p

included for tsmc18 process.

E.g., for verilog simulation, you should use g g

ncverilog +access+r tsmc18.v tpz973.v CHIP.v

4

I/O Pad Assignment

You should write ioc file according to your design before You should write .ioc file according to your design before

P&R.

In v file if no power pad information is included you may In .v file, if no power pad information is included, you may

add a new power pad by yourself.

VDD: PVDD1DGZ PVDD2DGZ // tsmc18 library VDD: PVDD1DGZ, PVDD2DGZ // tsmc18 library

VSS: PVSS1DGZ, PVSS2DGZ // tsmc18 library

Note: there are two types of power pads: (1) power pads for the Note: there are two types of power pads: (1) power pads for the

core (design), (2) power pads for I/O pads

Corner pads p

PCORNERDG // tsmc18 library

For other pads (design inputs/outputs), you should arrange For other pads (design inputs/outputs), you should arrange

them by yourself.

5

I/O Pad Assignment (Example)

CHIP

M

I1

I2

O1

Pad_I1

Pad_I2

Pad_O1

Version: 1 Version: 1

Pad: CORNER1 NW PCORNERDG

Pad: Pad_I1 N

Pad: Pad_CoreVDD N PVDD1DGZ

CORNER1

I

1

C

o

r

e

V

D

N

Pad: CORNER2 NE PCORNERDG

Pad: Pad_I2 W

Pad: PAD_CoreVSS W PVSS1DGZ

I2

CoreVSS

IOVSS

D

E

W

Pad: CORNER3 SW PCORNERDG

Pad: Pad_O1 S

Pad: PAD_IOVDD S PVDD2DGZ

P d CORNER4 SE PCORNERDG

I

O

V

D

D

O

1

6

Pad: CORNER4 SE PCORNERDG

Pad: PAD_IOVSS E PVSS2DGZ

D

S

I/O Pad Assignment (Notes)

For correct P&R you should make sure that in the v file For correct P&R, you should make sure that in the .v file

(CHIP.v), I/O pads are correctly connected to your original

design without pads. es g w t out pa s.

For power and corner pads (which are not included in the .v

file), pad types should be specified in the .ioc file. file), pad types should be specified in the .ioc file.

Pads are not necessarily uniformly distributed. (That is, we

can have different numbers of pads in different directions) can have different numbers of pads in different directions)

However, uniform assignment is suggested.

You might use more than one set of power pads (E g You might use more than one set of power pads (E.g.,

IOVDD1, IOVDD2, CoreVDD1, CoreVDD2).

Different rearrangements will result in different placement Different rearrangements will result in different placement,

routing, timing, power, etc.

7

You might also like

- DM 103vaDocument2 pagesDM 103vaTanvon MalikNo ratings yet

- 4-8-16 B Tech ECE Revised Batch 2011 3-8Document72 pages4-8-16 B Tech ECE Revised Batch 2011 3-8Zlatan Deric AturindaNo ratings yet

- Expanding The Synopsys Primetime Solution With Power AnalysisDocument7 pagesExpanding The Synopsys Primetime Solution With Power AnalysisAparna TiwariNo ratings yet

- FANUC R-J3iB - Maintenance Manual For Europe - B-81465EN-1-02Document345 pagesFANUC R-J3iB - Maintenance Manual For Europe - B-81465EN-1-02sierrapr92% (12)

- VCS Xprop: Increasing The Efficiency of X-Related Simulation and DebugDocument2 pagesVCS Xprop: Increasing The Efficiency of X-Related Simulation and Debugpinakin4uNo ratings yet

- Simple RTL PipelineDocument7 pagesSimple RTL PipelinepawanzNo ratings yet

- Synth ConstraintsDocument28 pagesSynth ConstraintsCherry AnushaNo ratings yet

- EC8661 VLSI Design Laboratory PDFDocument53 pagesEC8661 VLSI Design Laboratory PDFSINDHUNo ratings yet

- Atrenta Tutorial PDFDocument15 pagesAtrenta Tutorial PDFTechy GuysNo ratings yet

- 7 SeriesDocument416 pages7 SeriesEswaran SamyNo ratings yet

- FSM Implementations: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017Document25 pagesFSM Implementations: TIE-50206 Logic Synthesis Arto Perttula Tampere University of Technology Fall 2017antoniocljNo ratings yet

- tc1 6 Architecture Vol1Document225 pagestc1 6 Architecture Vol1Neelakandan Natarajan100% (1)

- Low Power VLSI Design: J.Ramesh ECE Department PSG College of TechnologyDocument146 pagesLow Power VLSI Design: J.Ramesh ECE Department PSG College of TechnologyVijay Kumar TNo ratings yet

- 03b - FIE - Parcial #3 PLD - Resumen 04c 09Document36 pages03b - FIE - Parcial #3 PLD - Resumen 04c 09amilcar93No ratings yet

- Buffer InsertionDocument47 pagesBuffer InsertionAkshay DesaiNo ratings yet

- Lecture 5 - Combinatorial and Sequential LogicDocument76 pagesLecture 5 - Combinatorial and Sequential LogicantoniocljNo ratings yet

- Arduino-Based Embedded System ModuleDocument8 pagesArduino-Based Embedded System ModuleIJRASETPublicationsNo ratings yet

- DSD 12 Synchronous DesignDocument9 pagesDSD 12 Synchronous DesignDavis AbrahamNo ratings yet

- Project FileDocument131 pagesProject FileshaanjalalNo ratings yet

- EDIflat 11 1.labDocument148 pagesEDIflat 11 1.labShahab KhanNo ratings yet

- DDR SDR Sdram ComparisionDocument12 pagesDDR SDR Sdram ComparisionSrinivas CherukuNo ratings yet

- SOC TestingDocument27 pagesSOC TestingMaria AllenNo ratings yet

- Common CentroidDocument4 pagesCommon CentroidSushil NaharNo ratings yet

- SpectreRF OhioDocument110 pagesSpectreRF OhioPratap P PratapNo ratings yet

- NBB - Module II - System PartitioingDocument60 pagesNBB - Module II - System Partitioing20D076 SHRIN BNo ratings yet

- 5 - Internal MemoryDocument22 pages5 - Internal Memoryerdvk100% (1)

- Course Systemverilog Oop For Uvm Verification Session2 Inheritance and Polymorphism DrichDocument14 pagesCourse Systemverilog Oop For Uvm Verification Session2 Inheritance and Polymorphism DrichsandraNo ratings yet

- Montecarlo PDFDocument7 pagesMontecarlo PDFSougata GhoshNo ratings yet

- Haps-54 March2009 ManualDocument74 pagesHaps-54 March2009 Manualjohn92691No ratings yet

- Commands Used in Soc Workshop PDFDocument16 pagesCommands Used in Soc Workshop PDFabhishek bhandareNo ratings yet

- 05 Systemc TutorialDocument32 pages05 Systemc TutorialjasonturfNo ratings yet

- Zynq 7000 TRMDocument1,770 pagesZynq 7000 TRMSambhav VermanNo ratings yet

- ASIC TimingDocument54 pagesASIC TimingKrishna MohanNo ratings yet

- ThrowAwayYourSpreadsheetsWorkShopSlides PDFDocument77 pagesThrowAwayYourSpreadsheetsWorkShopSlides PDFBudavarapu MaheshNo ratings yet

- Introduction To ADC TestingDocument78 pagesIntroduction To ADC Testingsanjeevss_200-No ratings yet

- Vi Editor Basic CommandsDocument2 pagesVi Editor Basic CommandsJust FriendNo ratings yet

- RC Optimization Best PracticesDocument12 pagesRC Optimization Best PracticespradeepmanthaniNo ratings yet

- Unit 1and II - ASIC - Design NewDocument120 pagesUnit 1and II - ASIC - Design New20D076 SHRIN BNo ratings yet

- HFIC Chapter 4 HF TransistorsDocument77 pagesHFIC Chapter 4 HF TransistorsYosra Be100% (1)

- 07 RTL Optimization TechniquesDocument20 pages07 RTL Optimization TechniquesvpsampathNo ratings yet

- Design of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTADocument22 pagesDesign of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTAZarion JacobsNo ratings yet

- Register and Its OperationsDocument56 pagesRegister and Its OperationsSARTHAK VARSHNEYNo ratings yet

- Mentor GraphicsDocument66 pagesMentor Graphicslhari_04No ratings yet

- Device Noise Simulation of ΔΣ Modulators (Designers-guide)Document22 pagesDevice Noise Simulation of ΔΣ Modulators (Designers-guide)alirezadNo ratings yet

- All Ac379 AnDocument43 pagesAll Ac379 AnsajusasiNo ratings yet

- Topic 6 - Clocking & Met A StabilityDocument9 pagesTopic 6 - Clocking & Met A Stabilityanish1988100% (1)

- Ahuja CompensationDocument5 pagesAhuja CompensationCem ÇakırNo ratings yet

- DVD2 JNTU Set1 SolutionsDocument12 pagesDVD2 JNTU Set1 Solutionsకిరణ్ కుమార్ పగడాలNo ratings yet

- Testability in EOCHL (And Beyond ) : Vladimir ZivkovicDocument24 pagesTestability in EOCHL (And Beyond ) : Vladimir ZivkovicsenthilkumarNo ratings yet

- Image Cryptography Design Based On Nano AES Security AlgorithmDocument6 pagesImage Cryptography Design Based On Nano AES Security AlgorithmIJRASETPublicationsNo ratings yet

- VLSI FPGA Projects Topics Using VHDL - Verilog - VLSI EncyclopediaDocument4 pagesVLSI FPGA Projects Topics Using VHDL - Verilog - VLSI EncyclopediaGunapalli venkata saikiranNo ratings yet

- Asic Prototyping AldecDocument10 pagesAsic Prototyping AldecKhaled Abou ElseoudNo ratings yet

- Unit - IV: Input - OutputDocument50 pagesUnit - IV: Input - Outputkarvind08No ratings yet

- Timing Behavior FSM Partitioning State Machine SignalingDocument47 pagesTiming Behavior FSM Partitioning State Machine SignalingsenthilkumarNo ratings yet

- 4 1.soc EncounterDocument181 pages4 1.soc Encounterachew911No ratings yet

- Vga BookDocument81 pagesVga BookManju BhargaviNo ratings yet

- Organization: Basic Computer Organization and DesignDocument29 pagesOrganization: Basic Computer Organization and DesignGemechisNo ratings yet

- Chapter 8 - CPU PerformanceDocument40 pagesChapter 8 - CPU PerformanceNurhidayatul FadhilahNo ratings yet

- Esp32 PDFDocument5 pagesEsp32 PDFIrfan ZuhriNo ratings yet

- 1-Getting To Know The BoardDocument4 pages1-Getting To Know The BoardaposhekerNo ratings yet

- Embedded System InternshipDocument47 pagesEmbedded System Internshipmangaimathi27No ratings yet

- STM32F4 Discovery Board Pinou Diagram Details, Features and ExamplesDocument11 pagesSTM32F4 Discovery Board Pinou Diagram Details, Features and ExamplesJsi DevNo ratings yet

- An Efficient RDL Routing For Flip Chip DesignsDocument10 pagesAn Efficient RDL Routing For Flip Chip DesignsAparna TiwariNo ratings yet

- Using Calbr WKB 919 03252003 9430Document550 pagesUsing Calbr WKB 919 03252003 9430Aparna Tiwari100% (1)

- ICC 201012 LG 06 FinishingDocument14 pagesICC 201012 LG 06 FinishingAparna TiwariNo ratings yet

- Multiple IO RingDocument27 pagesMultiple IO RingAparna TiwariNo ratings yet

- Master Thesis: Design and Implementation of A DDR Sdram Controller For System On ChipDocument89 pagesMaster Thesis: Design and Implementation of A DDR Sdram Controller For System On ChipAparna TiwariNo ratings yet

- Escuela de Sophia of Caloocan Inc Summative Test 2nd Grading CHS Sir RicDocument3 pagesEscuela de Sophia of Caloocan Inc Summative Test 2nd Grading CHS Sir RicRicardo NugasNo ratings yet

- EG8141A5 DatasheetDocument3 pagesEG8141A5 DatasheetdmolinapumaNo ratings yet

- RX Noise Bridges Belrose - 1988 05Document3 pagesRX Noise Bridges Belrose - 1988 05Raluca CiorceriNo ratings yet

- Coexistance Between AC Distribution and DC Distribution in The View of AppliancesDocument5 pagesCoexistance Between AC Distribution and DC Distribution in The View of AppliancesManti HerbertNo ratings yet

- NSFAS Laptop FormDocument2 pagesNSFAS Laptop FormKagiso China'män NtsaneNo ratings yet

- GSM SummaryDocument20 pagesGSM SummaryAnushree PunethaNo ratings yet

- Multiplexer, Demultiplexer and Encoder With Simulation and RTL SchematicDocument26 pagesMultiplexer, Demultiplexer and Encoder With Simulation and RTL SchematicJunaid ahmedNo ratings yet

- Overhead Robo For Safty & CommunicationDocument2 pagesOverhead Robo For Safty & CommunicationSanjayNo ratings yet

- DVG 6001GDocument2 pagesDVG 6001GAdão José PascoalNo ratings yet

- Electronic Devices and Circuits.Document8 pagesElectronic Devices and Circuits.Raja PirianNo ratings yet

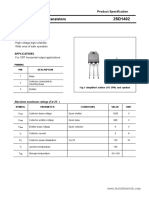

- D1402Document3 pagesD1402ban4444No ratings yet

- Datalogger MT 151Document2 pagesDatalogger MT 151Tung NguyenNo ratings yet

- ATT Unlimited Your WayDocument2 pagesATT Unlimited Your WayČärł-Ūñłøćkēr Tëčh210No ratings yet

- NEW Best OBS Streaming Settings For Slow InternDocument1 pageNEW Best OBS Streaming Settings For Slow InternJoy OrjiNo ratings yet

- List of Material - ElectricalDocument42 pagesList of Material - ElectricalHannah Verona JolisNo ratings yet

- 43 Military RadarsDocument15 pages43 Military RadarsShaik Ashwaq JavedNo ratings yet

- DSP LabmanualDocument82 pagesDSP LabmanualHemanth SharmaNo ratings yet

- Itron SMART TFT Modules TU800X480C-RT RangeDocument1 pageItron SMART TFT Modules TU800X480C-RT Rangeusman sajidNo ratings yet

- TutorialDocument224 pagesTutorialEspinoza RodriguezNo ratings yet

- Features: 75W Programmable Ip67 Driver Eum-075SxxxdgDocument13 pagesFeatures: 75W Programmable Ip67 Driver Eum-075SxxxdgCezarNo ratings yet

- An Efficient High Speed Wallace Tree MultiplierDocument5 pagesAn Efficient High Speed Wallace Tree MultiplierDelmaNo ratings yet

- Rotel rcd-971 SMDocument9 pagesRotel rcd-971 SMTwistedNo ratings yet

- SS-SM-009 Sensor Cable Spec Sheet Rev. EDocument2 pagesSS-SM-009 Sensor Cable Spec Sheet Rev. EDaniel Alexis HTNo ratings yet

- Eee1001 Electrical-circuits-And-systems LTP 1.0 1 Eee1001Document2 pagesEee1001 Electrical-circuits-And-systems LTP 1.0 1 Eee1001Mvrk KautilyaNo ratings yet

- Tariel Kapanadze CoilDocument5 pagesTariel Kapanadze Coilharishkumarsingh0% (1)

- CWNA Guide To Wireless LAN's Second Edition - Chapter 1Document39 pagesCWNA Guide To Wireless LAN's Second Edition - Chapter 1boytroy86100% (1)

- PP 2000 01Document132 pagesPP 2000 01franciscocampoverde8224100% (2)