Professional Documents

Culture Documents

Verilog L07 MIT

Verilog L07 MIT

Uploaded by

Nishant Jain0 ratings0% found this document useful (0 votes)

20 views18 pagesCopyright

© © All Rights Reserved

Available Formats

PDF, TXT or read online from Scribd

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

0 ratings0% found this document useful (0 votes)

20 views18 pagesVerilog L07 MIT

Verilog L07 MIT

Uploaded by

Nishant JainCopyright:

© All Rights Reserved

Available Formats

Download as PDF, TXT or read online from Scribd

You are on page 1of 18

6.

111 Fall 2007 Lecture 7, Slide 1

Design Example: Level-to-Pulse

A level-to-pulse converter produces a single-

cycle pulse each time its input goes high.

Its a synchronous rising-edge detector.

Sample uses:

Buttons and switches pressed by humans for

arbitrary periods of time

Single-cycle enable signals for counters

Level to

Pulse

Converter

L P

CLK

Whenever input L goes

from low to high...

...output P produces a

single pulse, one clock

period wide.

6.111 Fall 2007 Lecture 7, Slide 2

High input,

Waiting for fall

11

P = 0

L=1

L=0

00

Low input,

Waiting for rise

P = 0

01

Edge Detected!

P = 1

L=1

L=0

L=0

L=1

State transition diagram is a useful FSM representation and

design aid:

Step 1: State Transition Diagram

Block diagram of desired system:

D Q

Level to

Pulse

FSM

L P

unsynchronized

user input

Synchronizer

Edge Detector

This is the output that results from

this state. (Moore or Mealy?)

P = 0

11

Binary values of states

L=0

if L=0 at the clock edge,

then stay in state 00.

L=1

if L=1 at the clock edge,

then jump to state 01.

D Q

CLK

6.111 Fall 2007 Lecture 7, Slide 3

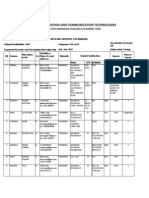

Step 2: Logic Derivation

00

Low input,

Waiting for rise

P = 0

01

Edge Detected!

P = 1

11

High input,

Waiting for fall

P = 0

L=1 L=1

L=0

L=0

L=1 L=0

1

0

1

0

1

0

L

In

0

0

1

1

0

0

P

Out

1

0

1

0

1

0

S

0

+

1

0

1

0

0

0

S

1

+

1

1

0

0

0

0

S

1

Next

State

Curren

t State

1

1

1

1

0

0

S

0

Combinational logic may be derived using Karnaugh maps

X 1 1 0 1

X 0 0 0 0

10 11 01 00

X 1 1 1 1

X 0 0 0 0

10 11 01 00

S

1

S

0

L

S

1

S

0

L

for S

1

+

:

for S

0

+

:

0 1 1

X 0 0

1 0

S

1

for P:

S

0

Comb.

Logic

CLK

n

Flip-

Flops

Comb.

Logic

D Q

S

n

S

+

L

P

S

1

+

= LS

0

S

0

+

= L

P = S

1

S

0

Transition diagram is readily converted to a

state transition table (just a truth table)

6.111 Fall 2007 Lecture 7, Slide 4

Moore Level-to-Pulse Converter

Moore FSM circuit implementation of level-to-pulse converter:

outputs

y

k

= f

k

(S)

inputs

x

0

...x

n

Comb.

Logic

CLK

n

Flip-

Flops

Comb.

Logic

D Q

present state S

n

next

state

S

+

D Q

S

1

+

= LS

0

S

0

+

= L

P = S

1

S

0

D Q

S

0

S

1

CLK

S

0

+

S

1

+

L

P

Q

Q

6.111 Fall 2007 Lecture 7, Slide 5

1. When L=1 and S=0, this output is

asserted immediately and until the

state transition occurs (or L changes).

2. While in state S=1 and as long as L

remains at 1, this output is asserted.

L=1 | P=0

L=1 | P=1

P=0

0

Input is low

1

Input is high

L=0 | P=0

L=0 | P=0

Design of a Mealy Level-to-Pulse

Since outputs are determined by state and inputs, Mealy FSMs may

need fewer states than Moore FSM implementations

S

Comb.

Logic

CLK

Flip-

Flops

Comb.

Logic

D Q

n

S

+

n

direct combinational path!

P

L

State

Clock

Output transitions immediately.

State transitions at the clock edge.

1

2

6.111 Fall 2007 Lecture 7, Slide 6

Mealy Level-to-Pulse Converter

Mealy FSM circuit implementation of level-to-pulse converter:

1

0

1

0

L

In

0

0

1

0

P

Out

1

0

1

0

S

+

Next

State

Pres.

State

1

1

0

0

S

D Q

S

CLK

S

+

L

P

Q

S

FSMs state simply remembers the previous value of L

Circuit benefits from the Mealy FSMs implicit single-

cycle assertion of outputs during state transitions

0

Input is low

1

Input is high

L=1 | P=1

L=0 | P=0

L=1 | P=0 L=0 | P=0

6.111 Fall 2007 Lecture 7, Slide 7

Moore/Mealy Trade-Offs

How are they different?

Moore: outputs = f( state ) only

Mealy outputs = f( state and input )

Mealy outputs generally occur one cycle earlier than a Moore:

Compared to a Moore FSM, a Mealy FSM might...

Be more difficult to conceptualize and design

Have fewer states

P

L

State

Clock

Mealy: immediate assertion of P

P

L

State[0]

Clock

Moore: delayed assertion of P

6.111 Fall 2007 Lecture 7, Slide 8

Light Switch Revisited

D Q

BUTTON

LIGHT

CLK

0

1

D Q

Q

Level-to-Pulse

FSM

Light Switch

FSM

6.111 Fall 2007 Lecture 7, Slide 9

FSM Example

GOAL:

Build an electronic combination lock with a reset

button, two number buttons (0 and 1), and an

unlock output. The combination should be 01011.

0

1

RESET

UNLOCK

STEPS:

1.Design lock FSM (block diagram, state transitions)

2.Write Verilog module(s) for FSM

6.111 Fall 2007 Lecture 7, Slide 10

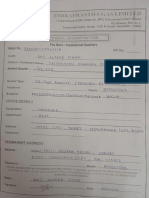

Step 1A: Block Diagram

fsm_clock

reset

b0_in

b1_in

lock

button

button

button

Clock

generator

Button

Enter

Button

0

Button

1

fsm

state

unlock

reset

b0

b1

LED

DISPLAY

Unlock

LED

6.111 Fall 2007 Lecture 7, Slide 11

Step 1B: State transition diagram

RESET

Unlock = 0

0

Unlock = 0

01

Unlock = 0

01011

Unlock = 1

0101

Unlock = 0

010

Unlock = 0

0 1

0

1 1

1

0

1

0

0

1

0

RESET

6 states ! 3 bits

6.111 Fall 2007 Lecture 7, Slide 12

Step 2: Write Verilog

module lock(clk,reset_in,b0_in,b1_in,out);

input clk,reset,b0_in,b1_in;

output out;

// synchronize push buttons, convert to pulses

// implement state transition diagram

reg [2:0] state,next_state;

always @ (*) begin

// combinational logic!

next_state = ???;

end

always @ (posedge clk) state <= next_state;

// generate output

assign out = ???;

// debugging?

endmodule

6.111 Fall 2007 Lecture 7, Slide 13

Step 2A: Synchronize buttons

// button -- push button synchronizer and level-to-pulse converter

// OUT goes high for one cycle of CLK whenever IN makes a

// low-to-high transition.

module button(clk,in,out);

input clk;

input in;

output out;

reg r1,r2,r3;

always @ (posedge clk)

begin

r1 <= in; // first reg in synchronizer

r2 <= r1; // second reg in synchronizer, output is in sync!

r3 <= r2; // remembers previous state of button

end

// rising edge = old value is 0, new value is 1

assign out = ~r3 & r2;

endmodule

D Q D Q D Q in

r3 r1 r2

clk

out

synchronizer state

6.111 Fall 2007 Lecture 7, Slide 14

Step 2B: state transition diagram

parameter S_RESET = 0; // state assignments

parameter S_0 = 1;

parameter S_01 = 2;

parameter S_010 = 3;

parameter S_0101 = 4;

parameter S_01011 = 5;

reg [2:0] state, next_state;

always @ (*) begin

// implement state transition diagram

if (reset) next_state = S_RESET;

else case (state)

S_RESET: next_state = b0 ? S_0 : b1 ? S_RESET : state;

S_0: next_state = b0 ? S_0 : b1 ? S_01 : state;

S_01: next_state = b0 ? S_010 : b1 ? S_RESET : state;

S_010: next_state = b0 ? S_0 : b1 ? S_0101 : state;

S_0101: next_state = b0 ? S_010 : b1 ? S_01011 : state;

S_01011: next_state = b0 ? S_0 : b1 ? S_RESET : state;

default: next_state = S_RESET; // handle unused states

endcase

end

always @ (posedge clk) state <= next_state;

RESET

Unlock = 0

0

Unlock = 0

01

Unlock = 0

01011

Unlock = 1

0101

Unlock = 0

010

Unlock = 0

0 1

0

1 1

1

0

1

0

0

1

0

RESET

6.111 Fall 2007 Lecture 7, Slide 15

Step 2C: generate output

// its a Moore machine! Output only depends on current state

assign out = (state == S_01011);

Step 2D: debugging?

// hmmm. What would be useful to know? Current state?

assign hex_display = {1'b0,state[2:0]};

6.111 Fall 2007 Lecture 7, Slide 16

Step 2: final Verilog implementation

module lock(clk,reset_in,b0_in,b1_in,out, hex_display);

input clk,reset,b0_in,b1_in;

output out; output[3:0] hex_display;

wire reset, b0, b1; // synchronize push buttons, convert to pulses

button b_reset(clk,reset_in,reset);

button b_0(clk,b0_in,b0);

button b_1(clk,b1_in,b1);

parameter S_RESET = 0; parameter S_0 = 1; // state assignments

parameter S_01 = 2; parameter S_010 = 3;

parameter S_0101 = 4; parameter S_01011 = 5;

reg [2:0] state,next_state;

always @ (*) begin // implement state transition diagram

if (reset) next_state = S_RESET;

else case (state)

S_RESET: next_state = b0 ? S_0 : b1 ? S_RESET : state;

S_0: next_state = b0 ? S_0 : b1 ? S_01 : state;

S_01: next_state = b0 ? S_010 : b1 ? S_RESET : state;

S_010: next_state = b0 ? S_0 : b1 ? S_0101 : state;

S_0101: next_state = b0 ? S_010 : b1 ? S_01011 : state;

S_01011: next_state = b0 ? S_0 : b1 ? S_RESET : state;

default: next_state = S_RESET; // handle unused states

endcase

end

always @ (posedge clk) state <= next_state;

assign out = (state == S_01011); // assign output: Moore machine

assign hex_display = {1'b0,state}; // debugging

endmodule

6.111 Fall 2007 Lecture 7, Slide 17

Where should CLK come from?

Option 1: external crystal

Stable, known frequency, typically 50% duty cycle

Option 2: internal signals

Option 2A: output of combinational logic

No! If inputs to logic change, output may make several

transitions before settling to final value ! several rising

edges, not just one! Hard to design away output glitches

Option 2B: output of a register

Okay, but timing of CLK2 wont line up with CLK1

D Q

CLK1

CLK2

CLK1

6.111 Fall 2007 Lecture 7, Slide 18

Summary

Modern digital system design:

Hardware description language FPGA / ASIC

Toolchain:

Design Entry Synthesis Implementation

New Labkit:

Design Entry

(Verilog)

Synthesis

(xst)

Implementation

(map, place, route)

Programming

(parallel cable)

S

i

m

u

l

a

t

i

o

n

(

m

o

d

e

l

s

i

m

)

*.v

rtl

*.bit

Black-box peripherals

Almost all functionality

is programmed in!

How to generate video?

Synchronize systems?

Create/Digitize Audio?

Serial & communications?

Simulate

You might also like

- Unit 4 - Turing MachineuuDocument50 pagesUnit 4 - Turing MachineuujunkBOX GladiAtorNo ratings yet

- Ultimate Ect ReviewerDocument2 pagesUltimate Ect ReviewerErvin John Yu Dy67% (3)

- Adder (Electronics)Document4 pagesAdder (Electronics)TurbosMixerNo ratings yet

- Circuit Deagrams of FIFODocument5 pagesCircuit Deagrams of FIFOSandip BhadaniNo ratings yet

- Scope of Scripting in VLSIDocument4 pagesScope of Scripting in VLSIAamodh KuthethurNo ratings yet

- Asynchronous Programming PatternsDocument174 pagesAsynchronous Programming PatternsgeorgesmaccarioNo ratings yet

- Stefan Doll-VHDL Verification Course-UPDATEDDocument133 pagesStefan Doll-VHDL Verification Course-UPDATEDblovellf2No ratings yet

- Registers and CountersDocument28 pagesRegisters and CountersHammadMehmoodNo ratings yet

- TCL TK Reference GuideDocument149 pagesTCL TK Reference GuideAnand ChaudharyNo ratings yet

- EE 4314 - Control Systems: Inverse Laplace TransformDocument8 pagesEE 4314 - Control Systems: Inverse Laplace TransformNick NumlkNo ratings yet

- Ahb-Lite To Apb Protocol: BY Shraddha Devaiya EC - 018 Anand Therattil EC - 092Document29 pagesAhb-Lite To Apb Protocol: BY Shraddha Devaiya EC - 018 Anand Therattil EC - 092AnandNo ratings yet

- RTL Coding For Logic SynthesisDocument11 pagesRTL Coding For Logic SynthesisgarimaguptaNo ratings yet

- Deterministic Finite Automata (DFA)Document19 pagesDeterministic Finite Automata (DFA)xigon53558No ratings yet

- IHI0024C Amba Apb Protocol SpecDocument28 pagesIHI0024C Amba Apb Protocol SpecAnil KumarNo ratings yet

- WA1.3 Bhat PaperDocument16 pagesWA1.3 Bhat PaperShashank Mishra100% (1)

- Introduction To VerilogDocument88 pagesIntroduction To Verilogmaster vijayNo ratings yet

- Design & Verification of AMBA APB ProtocolDocument4 pagesDesign & Verification of AMBA APB ProtocolKrishnajithKjNo ratings yet

- A Look at TCLDocument22 pagesA Look at TCLZachary Hayes100% (2)

- SoC System DesignDocument82 pagesSoC System DesignA B Shinde100% (2)

- Asic Design SyllabusDocument6 pagesAsic Design Syllabus20D076 SHRIN BNo ratings yet

- Cadence Digital Design Synthesis FlowDocument22 pagesCadence Digital Design Synthesis FlowAdeeb HusnainNo ratings yet

- Design, Characterization and Use of Custom Standard CellsDocument18 pagesDesign, Characterization and Use of Custom Standard CellsAlamgir MohammedNo ratings yet

- SDFDocument18 pagesSDFManda SwamyNo ratings yet

- Low Power Design of Digital SystemsDocument28 pagesLow Power Design of Digital SystemssuperECENo ratings yet

- Intro HDLDocument141 pagesIntro HDLAnonymous IN80L4rRNo ratings yet

- JESD204B Physical Layer (PHY) : Texas Instruments High Speed Data Converter TrainingDocument33 pagesJESD204B Physical Layer (PHY) : Texas Instruments High Speed Data Converter TrainingramukajarrNo ratings yet

- Verilog HDLDocument204 pagesVerilog HDLNhu Ngoc Phan Tran100% (1)

- Design Methodologies and ToolsDocument95 pagesDesign Methodologies and ToolsThomas JamesNo ratings yet

- An Introduction To Synopsys Design AutomationDocument24 pagesAn Introduction To Synopsys Design Automationprathap13No ratings yet

- Sed and AwkDocument13 pagesSed and AwkVamsi KrishnaNo ratings yet

- X-Prop - Mb3 Evans PresDocument83 pagesX-Prop - Mb3 Evans PresComposerNo ratings yet

- Hold and Setup Violation and SDFDocument2 pagesHold and Setup Violation and SDFIlaiyaveni IyanduraiNo ratings yet

- Xilinx Training CoursesDocument16 pagesXilinx Training Coursesnocaries9300No ratings yet

- VLSI Design - VerilogDocument30 pagesVLSI Design - Veriloganand_duraiswamyNo ratings yet

- Introduction To UNIXDocument67 pagesIntroduction To UNIXNeo DragonNo ratings yet

- Introduction To VHDLDocument88 pagesIntroduction To VHDLpusd_90No ratings yet

- Reference Manual: Date: 10/17/08Document31 pagesReference Manual: Date: 10/17/08Abhishek RanjanNo ratings yet

- Riscv SpecDocument236 pagesRiscv SpecAshwini PatilNo ratings yet

- APL in R PDFDocument14 pagesAPL in R PDFwilliam_V_LeeNo ratings yet

- The D Flip FlopDocument7 pagesThe D Flip FlopAlinChanNo ratings yet

- Quartus VHDL TutorialDocument9 pagesQuartus VHDL TutorialJose Antonio Jara ChavezNo ratings yet

- APBDocument29 pagesAPBsuneeldvNo ratings yet

- Vlsi ppts1-1Document63 pagesVlsi ppts1-1naveensilveriNo ratings yet

- Study and Analysis of RTL Verification Tool IEEE ConferenceDocument7 pagesStudy and Analysis of RTL Verification Tool IEEE ConferenceZC LNo ratings yet

- Fpga Programming Using Verilog HDL LanguageDocument89 pagesFpga Programming Using Verilog HDL LanguageSidhartha Sankar Rout0% (1)

- Verilog 2012Document70 pagesVerilog 2012Bach TrungNo ratings yet

- Verilog Lab Behavioral LevelDocument24 pagesVerilog Lab Behavioral LevelDr Sreenivasa Rao IjjadaNo ratings yet

- Risc VDocument66 pagesRisc Vfarha19No ratings yet

- Advance Digital Design Using VeilogDocument99 pagesAdvance Digital Design Using Veilogpcjoshi02No ratings yet

- A Shallow Introduction To The K Programming Language - Kuro5hinDocument22 pagesA Shallow Introduction To The K Programming Language - Kuro5hinlycancapitalNo ratings yet

- Register Transfer and MicrooperationsDocument57 pagesRegister Transfer and MicrooperationsSheena Mohammed100% (1)

- Shakti ReportDocument24 pagesShakti Reportsachin m cNo ratings yet

- Embedded Systems Interview QuestionsEmbedded Systems Interview QuestionsEmbedded Systems Interview QuestionsEmbedded Systems Interview QuestionsDocument1 pageEmbedded Systems Interview QuestionsEmbedded Systems Interview QuestionsEmbedded Systems Interview QuestionsEmbedded Systems Interview Questionsjanakiram473No ratings yet

- Xilinx Lab RecordDocument76 pagesXilinx Lab RecordDivya SantoshiNo ratings yet

- VHDL Bram BromDocument9 pagesVHDL Bram BromGmit MandyaNo ratings yet

- Fifo DesignDocument43 pagesFifo Designbviswanath84No ratings yet

- Logic Gates: Learning Differnt Types of Gates Designing The Logical CircuitsDocument17 pagesLogic Gates: Learning Differnt Types of Gates Designing The Logical CircuitsSmita ShetNo ratings yet

- Week 4 OOPDocument16 pagesWeek 4 OOPArslan Baloch AshuNo ratings yet

- L06Document32 pagesL06Aliya SarunNo ratings yet

- Meeting 1: A Past Time To RememberDocument12 pagesMeeting 1: A Past Time To RememberAmyunJun CottonNo ratings yet

- Effect of Corrosion in StructuresDocument32 pagesEffect of Corrosion in StructuresasvihariNo ratings yet

- REN RC210xxA DST 20230601Document59 pagesREN RC210xxA DST 20230601杉澤 佑樹No ratings yet

- World Rivers - World General Knowledge MCQsDocument7 pagesWorld Rivers - World General Knowledge MCQsAzad SamiNo ratings yet

- Synthesis Essay - DluceDocument3 pagesSynthesis Essay - Dluceapi-550300197No ratings yet

- Chapter 2 PDFDocument46 pagesChapter 2 PDFejamrespectNo ratings yet

- Advantages of Using Hot DI WaterDocument1 pageAdvantages of Using Hot DI WaterEduardo CastañedaNo ratings yet

- ADM Physical Science Q2 Module 3Document23 pagesADM Physical Science Q2 Module 3EdenNo ratings yet

- Scientific ManagementDocument24 pagesScientific Managementdipti30No ratings yet

- Part I: Nature and Scope of Managerial Economics DescriptionDocument8 pagesPart I: Nature and Scope of Managerial Economics DescriptionGamers PhilippinesNo ratings yet

- Chapter 7 AirDocument92 pagesChapter 7 AirVinetha NadarajanNo ratings yet

- A Electrical PDFDocument163 pagesA Electrical PDFsyed yaqubNo ratings yet

- Reflection Journey Beyond PositivismDocument3 pagesReflection Journey Beyond PositivismDiane DuranNo ratings yet

- 234 DS AssignmentDocument16 pages234 DS Assignmentbhupesh joshiNo ratings yet

- Sample MCQs On Employability Skills 2Document20 pagesSample MCQs On Employability Skills 2rohitkrajbhar9281No ratings yet

- Materials Today Communications: Mirko Kariz, Milan Sernek, Mur Čo Obućina, Manja Kitek KuzmanDocument6 pagesMaterials Today Communications: Mirko Kariz, Milan Sernek, Mur Čo Obućina, Manja Kitek KuzmanyaellNo ratings yet

- Lesson Plan MiraDocument5 pagesLesson Plan Miraika pratamaNo ratings yet

- DTC SS24 T&aDocument4 pagesDTC SS24 T&aemessa.docsNo ratings yet

- 407GXP - Garmin G1000HDocument2 pages407GXP - Garmin G1000HedwinNo ratings yet

- CoICT Postgraduate Admission 2013 - 14Document16 pagesCoICT Postgraduate Admission 2013 - 14Rashid BumarwaNo ratings yet

- Project Management Process Groups KA Mapping PMBOK 5TH EdDocument2 pagesProject Management Process Groups KA Mapping PMBOK 5TH EdDilip Kumar100% (1)

- Ayush Cutoff HK r1Document7 pagesAyush Cutoff HK r1Varshitha govindNo ratings yet

- Wireless Transceiver Circuits PDFDocument572 pagesWireless Transceiver Circuits PDFsaravananNo ratings yet

- Document IGLDocument10 pagesDocument IGLRaj SinghNo ratings yet

- The Importance of The English Language in Today's WorldDocument4 pagesThe Importance of The English Language in Today's WorldAlexander Walter Riveros BernardoNo ratings yet

- 7 SegdisplayDocument10 pages7 SegdisplaySatyarth SampathNo ratings yet

- UntitledDocument14 pagesUntitledsyntacs skNo ratings yet

- Reading: Test 1Document10 pagesReading: Test 131郭譿斳VeraNo ratings yet

- Bca 1 Sem Problem Solving Using C 76963 Nov 2019Document2 pagesBca 1 Sem Problem Solving Using C 76963 Nov 2019bishtamisha19No ratings yet