Professional Documents

Culture Documents

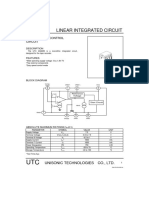

LM555

LM555

Uploaded by

jucsxxxCopyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

LM555

LM555

Uploaded by

jucsxxxCopyright:

Available Formats

2002 Fairchild Semiconductor Corporation

www.fairchildsemi.com www.fairchildsemi.com www.fairchildsemi.com www.fairchildsemi.com

Rev. 1.0.3

Features Features Features Features

High Current Drive Capability (200mA)

Adjustable Duty Cycle

Temperature Stability of 0.005%/C

Timing From Sec to Hours

Turn off Time Less Than 2Sec

Applications Applications Applications Applications

Precision Timing

Pulse Generation

Time Delay Generation

Sequential Timing

Description Description Description Description

The LM555/NE555/SA555 is a highly stable controller

capable of producing accurate timing pulses. With a

monostable operation, the time delay is controlled by one

external resistor and one capacitor. With an astable

operation, the frequency and duty cycle are accurately

controlled by two external resistors and one capacitor.

8-DIP 8-DIP 8-DIP 8-DIP

8-SOP 8-SOP 8-SOP 8-SOP

1

1

Internal Block Diagram Internal Block Diagram Internal Block Diagram Internal Block Diagram

F/F F/F F/F F/F

OutPut OutPut OutPut OutPut

Stage Stage Stage Stage

1 11 1

7 77 7

5 55 5

2 22 2

3 33 3

4 44 4

6 66 6

8 88 8

R RR R R RR R R RR R

Comp. Comp. Comp. Comp.

Comp. Comp. Comp. Comp.

Discharging Tr. Discharging Tr. Discharging Tr. Discharging Tr.

Vref Vref Vref Vref

Vcc Vcc Vcc Vcc

Discharge Discharge Discharge Discharge

Threshold Threshold Threshold Threshold

Control Control Control Control

Voltage Voltage Voltage Voltage

GND GND GND GND

Trigger Trigger Trigger Trigger

Output Output Output Output

Reset Reset Reset Reset

LM555/NE555/SA555

Si ngl e Ti mer

LM555/NE555/SA555

2 22 2

Absolute Maximum Ratings (T Absolute Maximum Ratings (T Absolute Maximum Ratings (T Absolute Maximum Ratings (T

A AA A

= 25 = 25 = 25 = 25 C) C) C) C)

Parameter Parameter Parameter Parameter Symbol Symbol Symbol Symbol Value Value Value Value Unit Unit Unit Unit

Supply Voltage VCC 16 V

Lead Temperature (Soldering 10sec) TLEAD 300 C

Power Dissipation PD 600 mW

Operating Temperature Range

LM555/NE555

SA555

TOPR 0 ~ +70

-40 ~ +85

C

Storage Temperature Range TSTG -65 ~ +150 C

LM555/NE555/SA555

3 33 3

Electrical Characteristics Electrical Characteristics Electrical Characteristics Electrical Characteristics

(TA = 25C, VCC = 5 ~ 15V, unless otherwise specified)

Notes: Notes: Notes: Notes:

1. When the output is high, the supply current is typically 1mA less than at VCC = 5V.

2. Tested at VCC = 5.0V and VCC = 15V.

3. This will determine the maximum value of RA + RB for 15V operation, the max. total R = 20M, and for 5V operation, the max.

total R = 6.7M.

4. These parameters, although guaranteed, are not 100% tested in production.

Parameter Parameter Parameter Parameter Symbol Symbol Symbol Symbol Conditions Conditions Conditions Conditions Min. Min. Min. Min. Typ. Typ. Typ. Typ. Max. Max. Max. Max. Unit Unit Unit Unit

Supply Voltage VCC - 4.5 - 16 V

Supply Current (Low Stable) (Note1) ICC

VCC = 5V, RL = - 3 6 mA

VCC = 15V, RL = - 7.5 15 mA

Timing Error (Monostable)

Initial Accuracy (Note2)

Drift with Temperature (Note4)

Drift with Supply Voltage (Note4)

ACCUR

t/T

t/VCC

RA = 1k to100k

C = 0.1F

- 1.0

50

0.1

3.0

0.5

%

ppm/C

%/V

Timing Error (Astable)

Intial Accuracy (Note2)

Drift with Temperature (Note4)

Drift with Supply Voltage (Note4)

ACCUR

t/T

t/VCC

RA = 1k to 100k

C = 0.1F

-

2.25

150

0.3

- %

ppm/C

%/V

Control Voltage VC

VCC = 15V 9.0 10.0 11.0 V

VCC = 5V 2.6 3.33 4.0 V

Threshold Voltage VTH

VCC = 15V - 10.0 - V

VCC = 5V - 3.33 - V

Threshold Current (Note3) ITH - -- - - 0.1 0.25 A

Trigger Voltage VTR

VCC = 5V 1.1 1.67 2.2 V

VCC = 15V 4.5 5 5.6 V

Trigger Current ITR VTR = 0V 0.01 2.0 A

Reset Voltage VRST - -- - 0.4 0.7 1.0 V

Reset Current IRST - -- - 0.1 0.4 mA

Low Output Voltage VOL

VCC = 15V

ISINK = 10mA

ISINK = 50mA

- 0.06

0.3

0.25

0.75

V

V

VCC = 5V

ISINK = 5mA

- 0.05 0.35 V

High Output Voltage VOH

VCC = 15V

ISOURCE = 200mA

ISOURCE = 100mA 12.75

12.5

13.3

- V

V

VCC = 5V

ISOURCE = 100mA

2.75 3.3 - V

Rise Time of Output (Note4) tR - -- - - 100 - ns

Fall Time of Output (Note4) tF - -- - - 100 - ns

Discharge Leakage Current ILKG - -- - - 20 100 nA

LM555/NE555/SA555

4 44 4

Application Information Application Information Application Information Application Information

Table 1 below is the basic operating table of 555 timer:

When the low signal input is applied to the reset terminal, the timer output remains low regardless of the threshold voltage or

the trigger voltage. Only when the high signal is applied to the reset terminal, the timer's output changes according to

threshold voltage and trigger voltage.

When the threshold voltage exceeds 2/3 of the supply voltage while the timer output is high, the timer's internal discharge Tr.

turns on, lowering the threshold voltage to below 1/3 of the supply voltage. During this time, the timer output is maintained

low. Later, if a low signal is applied to the trigger voltage so that it becomes 1/3 of the supply voltage, the timer's internal

discharge Tr. turns off, increasing the threshold voltage and driving the timer output again at high.

1. Monostable Operation 1. Monostable Operation 1. Monostable Operation 1. Monostable Operation

Table 1. Basic Operating Table Table 1. Basic Operating Table Table 1. Basic Operating Table Table 1. Basic Operating Table

Threshold Voltage Threshold Voltage Threshold Voltage Threshold Voltage

(V (V (V (Vth th th th)(PIN 6) )(PIN 6) )(PIN 6) )(PIN 6)

Trigger Voltage Trigger Voltage Trigger Voltage Trigger Voltage

(V (V (V (Vtr tr tr tr)(PIN 2) )(PIN 2) )(PIN 2) )(PIN 2)

Reset(PIN 4) Reset(PIN 4) Reset(PIN 4) Reset(PIN 4) Output(PIN 3) Output(PIN 3) Output(PIN 3) Output(PIN 3)

Discharging Tr. Discharging Tr. Discharging Tr. Discharging Tr.

(PIN 7) (PIN 7) (PIN 7) (PIN 7)

Don't care Don't care Low Low ON

Vth > 2Vcc / 3 Vth > 2Vcc / 3 High Low ON

Vcc / 3 < Vth < 2 Vcc / 3 Vcc / 3 < Vth < 2 Vcc / 3 High - -

Vth < Vcc / 3 Vth < Vcc / 3 High High OFF

10 10 10 10

-5 -5 -5 -5

10 10 10 10

-4 -4 -4 -4

10 10 10 10

-3 -3 -3 -3

10 10 10 10

-2 -2 -2 -2

10 10 10 10

-1 -1 -1 -1

10 10 10 10

0 00 0

10 10 10 10

1 11 1

10 10 10 10

2 22 2

10 10 10 10

-3 -3 -3 -3

10 10 10 10

-2 -2 -2 -2

10 10 10 10

-1 -1 -1 -1

10 10 10 10

0 00 0

10 10 10 10

1 11 1

10 10 10 10

2 22 2

1

0

M

1

0

M

1

0

M

1

0

M

1

M

1

M

1

M

1

M

1

0

k

1

0

k

1

0

k

1

0

k

1

0

0

k

1

0

0

k

1

0

0

k

1

0

0

k

RRR R

AAA A

=

1

k

=

1

k

=

1

k

=

1

k

C

a

p

a

c

i

t

a

n

c

e

(

u

F

)

C

a

p

a

c

i

t

a

n

c

e

(

u

F

)

C

a

p

a

c

i

t

a

n

c

e

(

u

F

)

C

a

p

a

c

i

t

a

n

c

e

(

u

F

)

Time Delay(s) Time Delay(s) Time Delay(s) Time Delay(s)

Figure 1. Monoatable Circuit Figure 1. Monoatable Circuit Figure 1. Monoatable Circuit Figure 1. Monoatable Circuit Figure 2. Resistance and Capacitance vs. Figure 2. Resistance and Capacitance vs. Figure 2. Resistance and Capacitance vs. Figure 2. Resistance and Capacitance vs.

Time delay(t Time delay(t Time delay(t Time delay(td dd d) )) )

Figure 3. Waveforms of Monostable Operation Figure 3. Waveforms of Monostable Operation Figure 3. Waveforms of Monostable Operation Figure 3. Waveforms of Monostable Operation

1

5

6

7

8 4

2

3

RESET Vcc

DISCH

THRES

CONT

GND

OUT

TRIG

+Vcc

RA

C1

C2 RL

Trigger

LM555/NE555/SA555

5 55 5

Figure 1 illustrates a monostable circuit. In this mode, the timer generates a fixed pulse whenever the trigger voltage falls

below Vcc/3. When the trigger pulse voltage applied to the #2 pin falls below Vcc/3 while the timer output is low, the timer's

internal flip-flop turns the discharging Tr. off and causes the timer output to become high by charging the external capacitor C1

and setting the flip-flop output at the same time.

The voltage across the external capacitor C1, VC1 increases exponentially with the time constant t=RA*C and reaches 2Vcc/3

at td=1.1RA*C. Hence, capacitor C1 is charged through resistor RA. The greater the time constant RAC, the longer it takes

for the VC1 to reach 2Vcc/3. In other words, the time constant RAC controls the output pulse width.

When the applied voltage to the capacitor C1 reaches 2Vcc/3, the comparator on the trigger terminal resets the flip-flop,

turning the discharging Tr. on. At this time, C1 begins to discharge and the timer output converts to low.

In this way, the timer operating in the monostable repeats the above process. Figure 2 shows the time constant relationship

based on RA and C. Figure 3 shows the general waveforms during the monostable operation.

It must be noted that, for a normal operation, the trigger pulse voltage needs to maintain a minimum of Vcc/3 before the timer

output turns low. That is, although the output remains unaffected even if a different trigger pulse is applied while the output is

high, it may be affected and the waveform does not operate properly if the trigger pulse voltage at the end of the output pulse

remains at below Vcc/3. Figure 4 shows such a timer output abnormality.

2. Astable Operation 2. Astable Operation 2. Astable Operation 2. Astable Operation

Figure 4. Waveforms of Monostable Operation (abnormal) Figure 4. Waveforms of Monostable Operation (abnormal) Figure 4. Waveforms of Monostable Operation (abnormal) Figure 4. Waveforms of Monostable Operation (abnormal)

100m 100m 100m 100m 1 11 1 10 10 10 10 100 100 100 100 1k 1k 1k 1k 10k 10k 10k 10k 100k 100k 100k 100k

1E-3 1E-3 1E-3 1E-3

0.01 0.01 0.01 0.01

0.1 0.1 0.1 0.1

1 11 1

10 10 10 10

100 100 100 100

1

0

M

1

0

M

1

0

M

1

0

M

1

M

1

M

1

M

1

M

1

0

0

k

1

0

0

k

1

0

0

k

1

0

0

k

1

0

k

1

0

k

1

0

k

1

0

k

1

k

1

k

1

k

1

k

(R (R (R (R

A AA A

+2R +2R +2R +2R

B BB B

) )) )

C

a

p

a

c

i

t

a

n

c

e

(

u

F

)

C

a

p

a

c

i

t

a

n

c

e

(

u

F

)

C

a

p

a

c

i

t

a

n

c

e

(

u

F

)

C

a

p

a

c

i

t

a

n

c

e

(

u

F

)

Fr equency(Hz) Fr equency(Hz) Fr equency(Hz) Fr equency(Hz)

Figure 5. Astable Circuit Figure 5. Astable Circuit Figure 5. Astable Circuit Figure 5. Astable Circuit

Figure 6. Capacitance and Resistance vs. Frequency Figure 6. Capacitance and Resistance vs. Frequency Figure 6. Capacitance and Resistance vs. Frequency Figure 6. Capacitance and Resistance vs. Frequency

1

5

6

7

8 4

2

3

RESET Vcc

DISCH

THRES

CONT

GND

OUT

TRIG

+Vcc

RA

C1

C2 RL

RB

LM555/NE555/SA555

6 66 6

An astable timer operation is achieved by adding resistor RB to Figure 1 and configuring as shown on Figure 5. In the astable

operation, the trigger terminal and the threshold terminal are connected so that a self-trigger is formed, operating as a multi

vibrator. When the timer output is high, its internal discharging Tr. turns off and the VC1 increases by exponential

function with the time constant (RA+RB)*C.

When the VC1, or the threshold voltage, reaches 2Vcc/3, the comparator output on the trigger terminal becomes high,

resetting the F/F and causing the timer output to become low. This in turn turns on the discharging Tr. and the C1 discharges

through the discharging channel formed by RB and the discharging Tr. When the VC1 falls below Vcc/3, the comparator

output on the trigger terminal becomes high and the timer output becomes high again. The discharging Tr. turns off and the

VC1 rises again.

In the above process, the section where the timer output is high is the time it takes for the VC1 to rise from Vcc/3 to 2Vcc/3,

and the section where the timer output is low is the time it takes for the VC1 to drop from 2Vcc/3 to Vcc/3. When timer output

is high, the equivalent circuit for charging capacitor C1 is as follows:

Since the duration of the timer output high state(tH) is the amount of time it takes for the VC1(t) to reach 2Vcc/3,

Figure 7. Waveforms of Astable Operation Figure 7. Waveforms of Astable Operation Figure 7. Waveforms of Astable Operation Figure 7. Waveforms of Astable Operation

Vcc

R

A

R

B

C1 Vc1(0-)=Vcc/3

C

1

dv

c1

dt

-------------

V

cc

V 0- ( )

R

A

R

B

+

------------------------------- = 1 ( )

V

C1

0+ ( ) V

CC

3 = 2 ( )

V

C1

t ( ) V

CC

1

2

3

---e

-

t

R

A

R

B

+ ( )C1

------------------------------------

= 3 ( )

LM555/NE555/SA555

7 77 7

The equivalent circuit for discharging capacitor C1, when timer output is low is, as follows:

Since the duration of the timer output low state(tL) is the amount of time it takes for the VC1(t) to reach Vcc/3,

Since RD is normally RB>>RD although related to the size of discharging Tr.,

tL=0.693RBC1 (10)

Consequently, if the timer operates in astable, the period is the same with

'T=tH+tL=0.693(RA+RB)C1+0.693RBC1=0.693(RA+2RB)C1' because the period is the sum of the charge time and discharge

time. And since frequency is the reciprocal of the period, the following applies.

3. Frequency divider 3. Frequency divider 3. Frequency divider 3. Frequency divider

By adjusting the length of the timing cycle, the basic circuit of Figure 1 can be made to operate as a frequency divider. Figure

8. illustrates a divide-by-three circuit that makes use of the fact that retriggering cannot occur during the timing cycle.

V

C1

t ( )

2

3

---V

CC

V =

CC

1

2

3

---e

-

t

H

R

A

R

B

+ ( )C1

------------------------------------

= 4 ( )

t

H

C

1

R

A

R

B

+ ( )In2 0.693 R

A

R

B

+ ( )C

1

= = 5 ( )

C1

R

B

R

D

V

C1

(0-)=2Vcc/3

C

1

dv

C1

dt

--------------

1

R

A

R

B

+

-----------------------V

C1

0 = + 6 ( )

V

C1

t ( )

2

3

---V

CC

e

-

t

R

A

R

D

+ ( )C1

-------------------------------------

= 7 ( )

1

3

---V

CC

2

3

---V

CC

e

-

t

L

R

A

R

D

+ ( )C1

-------------------------------------

= 8 ( )

t

L

C

1

R

B

R

D

+ ( )In2 0.693 R

B

R

D

+ ( )C

1

= = 9 ( )

frequency, f

1

T

---

1.44

R

A

2R

B

+ ( )C

1

---------------------------------------- = = 11 ( )

LM555/NE555/SA555

8 88 8

4. Pulse Width Modulation 4. Pulse Width Modulation 4. Pulse Width Modulation 4. Pulse Width Modulation

The timer output waveform may be changed by modulating the control voltage applied to the timer's pin 5 and changing the

reference of the timer's internal comparators. Figure 9 illustrates the pulse width modulation circuit.

When the continuous trigger pulse train is applied in the monostable mode, the timer output width is modulated according to

the signal applied to the control terminal. Sine wave as well as other waveforms may be applied as a signal to the control

terminal. Figure 10 shows the example of pulse width modulation waveform.

5. Pulse Position Modulation 5. Pulse Position Modulation 5. Pulse Position Modulation 5. Pulse Position Modulation

If the modulating signal is applied to the control terminal while the timer is connected for the astable operation as in Figure 11,

the timer becomes a pulse position modulator.

In the pulse position modulator, the reference of the timer's internal comparators is modulated which in turn modulates the

timer output according to the modulation signal applied to the control terminal.

Figure 12 illustrates a sine wave for modulation signal and the resulting output pulse position modulation : however, any wave

shape could be used.

Figure 8. Waveforms of Frequency Divider Operation Figure 8. Waveforms of Frequency Divider Operation Figure 8. Waveforms of Frequency Divider Operation Figure 8. Waveforms of Frequency Divider Operation

Figure 9. Circuit for Pulse Width Modulation Figure 9. Circuit for Pulse Width Modulation Figure 9. Circuit for Pulse Width Modulation Figure 9. Circuit for Pulse Width Modulation Figure 10. Waveforms of Pulse Width Modulation Figure 10. Waveforms of Pulse Width Modulation Figure 10. Waveforms of Pulse Width Modulation Figure 10. Waveforms of Pulse Width Modulation

8 4

7

1

2

3

5

6

CONT

GND

Vcc

DISCH

THRES

RESET

TRIG

OUT

+Vcc +Vcc +Vcc +Vcc

Trigger Trigger Trigger Trigger

R RR R

A AA A

C CC C

Output Output Output Output

Input Input Input Input

LM555/NE555/SA555

9 99 9

6. Linear Ramp 6. Linear Ramp 6. Linear Ramp 6. Linear Ramp

When the pull-up resistor RA in the monostable circuit shown in Figure 1 is replaced with constant current source, the VC1

increases linearly, generating a linear ramp. Figure 13 shows the linear ramp generating circuit and Figure 14 illustrates the

generated linear ramp waveforms.

In Figure 13, current source is created by PNP transistor Q1 and resistor R1, R2, and RE.

For example, if Vcc=15V, RE=20k, R1=5kW, R2=10k, and VBE=0.7V,

VE=0.7V+10V=10.7V

Ic=(15-10.7)/20k=0.215mA

8 4

7

1

2

3

5

6

CONT

GND

Vcc

DISCH

THRES

RESET

TRIG

OUT

+Vcc +Vcc +Vcc +Vcc

R RR R

A AA A

C CC C

R RR R

B BB B

Modulation Modulation Modulation Modulation

Output Output Output Output

Figure 11. Circuit for Pulse Position Modulation Figure 11. Circuit for Pulse Position Modulation Figure 11. Circuit for Pulse Position Modulation Figure 11. Circuit for Pulse Position Modulation

Figure 12. Waveforms of pulse position modulation Figure 12. Waveforms of pulse position modulation Figure 12. Waveforms of pulse position modulation Figure 12. Waveforms of pulse position modulation

Figure 13. Circuit for Linear Ramp Figure 13. Circuit for Linear Ramp Figure 13. Circuit for Linear Ramp Figure 13. Circuit for Linear Ramp Figure 14. Waveforms of Linear Ramp Figure 14. Waveforms of Linear Ramp Figure 14. Waveforms of Linear Ramp Figure 14. Waveforms of Linear Ramp

1

5

6

7

8 4

2

3

RESET Vcc

DISCH

THRES

CONT

GND

OUT

TRIG

+Vcc

C2

R1

R2

C1

Q1

Output

RE

I

C

V

CC

V

E

R

E

--------------------------- = 12 ( )

Here, V

E is

V

E

V

BE

R

2

R

1

R

2

+

----------------------V

CC

+ = 13 ( )

LM555/NE555/SA555

10 10 10 10

When the trigger starts in a timer configured as shown in Figure 13, the current flowing through capacitor C1 becomes a

constant current generated by PNP transistor and resistors.

Hence, the VC is a linear ramp function as shown in Figure 14. The gradient S of the linear ramp function is defined as

follows:

Here the Vp-p is the peak-to-peak voltage.

If the electric charge amount accumulated in the capacitor is divided by the capacitance, the VC comes out as follows:

V=Q/C (15)

The above equation divided on both sides by T gives us

and may be simplified into the following equation.

S=I/C (17)

In other words, the gradient of the linear ramp function appearing across the capacitor can be obtained by using the constant

current flowing through the capacitor.

If the constant current flow through the capacitor is 0.215mA and the capacitance is 0.02F, the gradient of the ramp function

at both ends of the capacitor is S = 0.215m/0.022 = 9.77V/ms.

S

V

p p

T

---------------- = 14 ( )

V

T

--- -

Q T

C

------------ = 16 ( )

LM555/NE555/SA555

11 11 11 11

Mechanical Dimensions Mechanical Dimensions Mechanical Dimensions Mechanical Dimensions

Package Package Package Package

Dimensions in millimeters Dimensions in millimeters Dimensions in millimeters Dimensions in millimeters

6.40 0.20

3.30 0.30

0.130 0.012

3.40 0.20

0.134 0.008

#1

#4 #5

#8

0.252 0.008

9

.

2

0

0

.

2

0

0

.

7

9

2

.

5

4

0

.

1

0

0

0

.

0

3

1

(

)

0

.

4

6

0

.

1

0

0

.

0

1

8

0

.

0

0

4

0

.

0

6

0

0

.

0

0

4

1

.

5

2

4

0

.

1

0

0

.

3

6

2

0

.

0

0

8

9

.

6

0

0

.

3

7

8

M

A

X

5.08

0.200

0.33

0.013

7.62

0

~

1

5

0.300

MAX

MIN

0.25

+0.10

0.05

0.010

+0.004

0.002

8-DIP 8-DIP 8-DIP 8-DIP

LM555/NE555/SA555

12 12 12 12

Mechanical Dimensions Mechanical Dimensions Mechanical Dimensions Mechanical Dimensions (Continued)

Package Package Package Package

Dimensions in millimeters Dimensions in millimeters Dimensions in millimeters Dimensions in millimeters

4

.

9

2

0

.

2

0

0

.

1

9

4

0

.

0

0

8

0

.

4

1

0

.

1

0

0

.

0

1

6

0

.

0

0

4

1

.

2

7

0

.

0

5

0

5.72

0.225

1.55 0.20

0.061 0.008

0.1~0.25

0.004~0.001

6.00 0.30

0.236 0.012

3.95 0.20

0.156 0.008

0.50 0.20

0.020 0.008

5

.

1

3

0

.

2

0

2

M

A

X

#1

#4 #5

0

~

8

#8

0

.

5

6

0

.

0

2

2

(

)

1.80

0.071

M

A

X

0

.

1

0

M

A

X

0

.

0

0

4

MAX

MIN

+

0

.

1

0

-

0

.

0

5

0

.

1

5

+

0

.

0

0

4

-

0

.

0

0

2

0

.

0

0

6

8-SOP 8-SOP 8-SOP 8-SOP

LM555/NE555/SA555

13 13 13 13

Ordering Information Ordering Information Ordering Information Ordering Information

Product Number Product Number Product Number Product Number Package Package Package Package Operating Temperature Operating Temperature Operating Temperature Operating Temperature

LM555CN 8-DIP

0 ~ +70C

LM555CM 8-SOP

Product Number Product Number Product Number Product Number Package Package Package Package Operating Temperature Operating Temperature Operating Temperature Operating Temperature

NE555N 8-DIP

0 ~ +70C

NE555D 8-SOP

Product Number Product Number Product Number Product Number Package Package Package Package Operating Temperature Operating Temperature Operating Temperature Operating Temperature

SA555 8-DIP

-40 ~ +85C

SA555D 8-SOP

LM555/NE555/SA555 LM555/NE555/SA555 LM555/NE555/SA555 LM555/NE555/SA555

11/29/02 0.0m 001

Stock#DSxxxxxxxx

2002 Fairchild Semiconductor Corporation

LIFE SUPPORT POLICY LIFE SUPPORT POLICY LIFE SUPPORT POLICY LIFE SUPPORT POLICY

FAIRCHILDS PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES

OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR

CORPORATION. As used herein:

1. Life support devices or systems are devices or systems

which, (a) are intended for surgical implant into the body,

or (b) support or sustain life, and (c) whose failure to

perform when properly used in accordance with

instructions for use provided in the labeling, can be

reasonably expected to result in a significant injury of the

user.

2. A critical component in any component of a life support

device or system whose failure to perform can be

reasonably expected to cause the failure of the life support

device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

DISCLAIMER DISCLAIMER DISCLAIMER DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY

PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY

LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER

DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

You might also like

- Binthen Motorized Curtain Price List Rev1.0 Jan 2022Document4 pagesBinthen Motorized Curtain Price List Rev1.0 Jan 2022Emil EremiaNo ratings yet

- 2015-2016 TestDocument15 pages2015-2016 TestMohamed Issam45% (29)

- Go Programming LanguageDocument21 pagesGo Programming LanguageKevin Lysander James100% (1)

- PIX4D Simply PowerfulDocument43 pagesPIX4D Simply PowerfulJUAN BAQUERONo ratings yet

- LM555Document14 pagesLM555Lactalis GenesisNo ratings yet

- LM555Document14 pagesLM555haodt2002No ratings yet

- Single Timer: Features DescriptionDocument13 pagesSingle Timer: Features DescriptionSonal GuptaNo ratings yet

- Single Timer: Features DescriptionDocument13 pagesSingle Timer: Features DescriptionSonal GuptaNo ratings yet

- Single Timer: Features DescriptionDocument14 pagesSingle Timer: Features DescriptionAHMED MELIH ULUSOYNo ratings yet

- Unisonic Technologies Co., LTD: Single TimerDocument8 pagesUnisonic Technologies Co., LTD: Single TimerDevartha AncenNo ratings yet

- Unisonic Technologies Co., LTD: Single TimerDocument7 pagesUnisonic Technologies Co., LTD: Single TimerMarco BrupenNo ratings yet

- LM555 2Document2 pagesLM555 2Jomar SartoNo ratings yet

- KA558 FairchildSemiconductor PDFDocument6 pagesKA558 FairchildSemiconductor PDFCajun LeBeauNo ratings yet

- Utc3842 YouwangelectronicsDocument9 pagesUtc3842 YouwangelectronicsMindSet MarcosNo ratings yet

- Quad Timer: Features DescriptionDocument6 pagesQuad Timer: Features DescriptionCajun LeBeauNo ratings yet

- Mip2L30Mtscf: Product StandardsDocument9 pagesMip2L30Mtscf: Product StandardsSIVARAMANJAGANATHANNo ratings yet

- LM555 1Document2 pagesLM555 1Jomar SartoNo ratings yet

- AN6650 کنترل دور موتورDocument3 pagesAN6650 کنترل دور موتورJavad MohseniNo ratings yet

- SSCNE555: Elektronische BauelementeDocument5 pagesSSCNE555: Elektronische BauelementeValentin RaduNo ratings yet

- SMPS Controller: Features DescriptionDocument11 pagesSMPS Controller: Features DescriptionAdah BumboneNo ratings yet

- Precision Timer: Connection DiagramDocument5 pagesPrecision Timer: Connection DiagramValentin RaduNo ratings yet

- Soldadora UTC3843DDocument9 pagesSoldadora UTC3843DChristian ormeñoNo ratings yet

- UC3846Document10 pagesUC3846Polo Soldas Polo SoldasNo ratings yet

- SMSNE555: Elektronische BauelementeDocument5 pagesSMSNE555: Elektronische BauelementeValentin RaduNo ratings yet

- UTC TL1451 Linear Integrated Circuit: Dual Pulse-Width-Modulation Control CircuitsDocument5 pagesUTC TL1451 Linear Integrated Circuit: Dual Pulse-Width-Modulation Control CircuitsMarcos Gomes MisselNo ratings yet

- 3842Document12 pages3842luisNo ratings yet

- Description: P Ack AgeDocument3 pagesDescription: P Ack AgeAlexandru CioponeaNo ratings yet

- UC3842/UC3843/UC3844/UC3845: SMPS ControllerDocument12 pagesUC3842/UC3843/UC3844/UC3845: SMPS ControllerMohamed HaddadNo ratings yet

- 3842a DatasheetDocument8 pages3842a DatasheetVịnh DemoNo ratings yet

- Ka5S-Series: KA5S0765C/KA5S0965/KA5S12656/KA5S1265 Fairchild Power Switch (FPS)Document16 pagesKa5S-Series: KA5S0765C/KA5S0965/KA5S12656/KA5S1265 Fairchild Power Switch (FPS)Arte Y MecatrónicaNo ratings yet

- UTC NE558 Linear Integrated Circuit: Quad TimerDocument2 pagesUTC NE558 Linear Integrated Circuit: Quad TimerCajun LeBeauNo ratings yet

- TC74HC279AP, TC74HC279AF: Quad S - R LatchDocument8 pagesTC74HC279AP, TC74HC279AF: Quad S - R LatchBiblia em ÁudioNo ratings yet

- NE556 Linear Integrated Circuit: Dual TimerDocument4 pagesNE556 Linear Integrated Circuit: Dual TimerJim LiebNo ratings yet

- BD9882F, FVDocument5 pagesBD9882F, FVbahti1284No ratings yet

- 74HC132APDocument8 pages74HC132APSlobodan StrizovicNo ratings yet

- SE8117TADocument7 pagesSE8117TAdavid.gjeorgevskiNo ratings yet

- UTC AN6650 Linear Integrated Circuit: Motor Speed Control CircuitDocument3 pagesUTC AN6650 Linear Integrated Circuit: Motor Speed Control CircuitLeider montero lunaNo ratings yet

- IP3002 DatasheetDocument11 pagesIP3002 DatasheetSerhiiNo ratings yet

- TC74HC175AP, TC74HC175AF, TC74HC175AFN: Quad D-Type Flip Flop With ClearDocument10 pagesTC74HC175AP, TC74HC175AF, TC74HC175AFN: Quad D-Type Flip Flop With ClearEngin UzunNo ratings yet

- LM1578A/LM2578A/LM3578A Switching Regulator: General Description FeaturesDocument18 pagesLM1578A/LM2578A/LM3578A Switching Regulator: General Description FeaturesMauricio VillarNo ratings yet

- Bay Linear: Current Mode PWM ControllerDocument11 pagesBay Linear: Current Mode PWM ControllerShashikant PatilNo ratings yet

- DatasheetDocument12 pagesDatasheetJuan JoseNo ratings yet

- Datasheet 10Document5 pagesDatasheet 10Kike VillasurNo ratings yet

- Ir1150 (S) (Pbf) Ir1150I (S) (Pbf) : Μpfc One Cycle Control Pfc IcDocument16 pagesIr1150 (S) (Pbf) Ir1150I (S) (Pbf) : Μpfc One Cycle Control Pfc IcBidu BiduNo ratings yet

- Current Mode PWMDocument9 pagesCurrent Mode PWMluis albertoNo ratings yet

- ZSCT1555: Precision Single Cell TimerDocument10 pagesZSCT1555: Precision Single Cell TimerDylan FlorezNo ratings yet

- TC2001Document15 pagesTC2001api-3736768No ratings yet

- KA7500BDocument8 pagesKA7500Bzdenko60No ratings yet

- SMPS Controller: Features DescriptionDocument8 pagesSMPS Controller: Features DescriptionVolodiyaNo ratings yet

- 3A L.D.O. VOLTAGE REGULATOR (Adjustable & Fixed) LM1085: FeaturesDocument8 pages3A L.D.O. VOLTAGE REGULATOR (Adjustable & Fixed) LM1085: FeatureslghmshariNo ratings yet

- TLE4266G SiemensSemiconductorGroupDocument9 pagesTLE4266G SiemensSemiconductorGroupDuranRod2013No ratings yet

- Servo Control IC ZN409: Absolute Maximum RatingsDocument6 pagesServo Control IC ZN409: Absolute Maximum RatingsArmannovNo ratings yet

- Current Controller For Stepping Motors: DescriptionDocument8 pagesCurrent Controller For Stepping Motors: DescriptionNuno FilipeNo ratings yet

- Ilicore: Motor Speed Control Circuit D6650Document4 pagesIlicore: Motor Speed Control Circuit D6650Byhna TosaNo ratings yet

- DP8600C YwDocument9 pagesDP8600C YwSURESH CHANDRA ROUTNo ratings yet

- Surface Mount Transient Voltage Suppressor SMCJ SERIES Q1812Document9 pagesSurface Mount Transient Voltage Suppressor SMCJ SERIES Q1812Ronald Lima do NascimentoNo ratings yet

- TSM103W: Dual Operational Amplifier and Voltage ReferenceDocument7 pagesTSM103W: Dual Operational Amplifier and Voltage Reference[INSERT MY NAME]No ratings yet

- 3843ANDocument8 pages3843ANinfosolutionNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- 404 Westridge Dr. - Watsonville, CA 95076 831/761-6555 - 800/525-1609 - FAX 831/761-6544Document12 pages404 Westridge Dr. - Watsonville, CA 95076 831/761-6555 - 800/525-1609 - FAX 831/761-6544api-3720161No ratings yet

- lm355 PDFDocument12 pageslm355 PDFCesar VilledaNo ratings yet

- TahoeDocument58 pagesTahoeapi-3720161No ratings yet

- SensorsDocument30 pagesSensorsapi-3720161100% (1)

- Prjtguidlns Ocw-EmbeddedDocument6 pagesPrjtguidlns Ocw-Embeddedapi-3720161No ratings yet

- Lec 36-AssemblyDocument3 pagesLec 36-Assemblyapi-3720161No ratings yet

- DaintroDocument62 pagesDaintroapi-3720161No ratings yet

- Kozinski HarperDocument37 pagesKozinski Harperapi-3720161No ratings yet

- Homeland Security StrategyDocument90 pagesHomeland Security Strategyapi-3720161No ratings yet

- 19 - 20070327 - Course p-4 Spring 2005Document70 pages19 - 20070327 - Course p-4 Spring 2005api-3720161No ratings yet

- 19 - 20070327 - Course p-5 Spring 2005Document74 pages19 - 20070327 - Course p-5 Spring 2005api-3720161No ratings yet

- 19 - 20070327 - Course p-3 Spring 2005Document42 pages19 - 20070327 - Course p-3 Spring 2005api-3720161No ratings yet

- Class2 Aits 04-AssemblyDocument28 pagesClass2 Aits 04-Assemblyapi-3720161No ratings yet

- 19 - 20070327 - Course p-1 Spring 2005Document47 pages19 - 20070327 - Course p-1 Spring 2005api-3720161No ratings yet

- Creating and Initializing Oracle® Hyperion Workforce Planning, Fusion Edition 11.1.2 ApplicationsDocument27 pagesCreating and Initializing Oracle® Hyperion Workforce Planning, Fusion Edition 11.1.2 ApplicationsPriyanka GargNo ratings yet

- Bio Clina Booklet enDocument22 pagesBio Clina Booklet enCarlos LehmanNo ratings yet

- Tools and DefinitionsDocument14 pagesTools and Definitionsjoseph john durolfoNo ratings yet

- 15 Basic Steps in Boiler DesignDocument11 pages15 Basic Steps in Boiler DesignPesona Alam CilebakNo ratings yet

- The Role of Social Media Sites in The Enhancement of English Language LearningDocument9 pagesThe Role of Social Media Sites in The Enhancement of English Language LearningnengcintiaNo ratings yet

- Prueba Presión Mazda 6Document8 pagesPrueba Presión Mazda 6Jose Luis LopezNo ratings yet

- 2014 Scheme Abd Syllabus - 12 11 2017 PDFDocument206 pages2014 Scheme Abd Syllabus - 12 11 2017 PDFNikhil JoshiNo ratings yet

- Perfect Plus Asia Brochure MPAPP02.2015Document8 pagesPerfect Plus Asia Brochure MPAPP02.2015toufikNo ratings yet

- Methanol Plants: How You Profit From Our One-Stop ShopDocument7 pagesMethanol Plants: How You Profit From Our One-Stop ShopMuhammad NaeemNo ratings yet

- Fan7529 1006915Document23 pagesFan7529 1006915Valmir BarbosaNo ratings yet

- Current Resume - TechDocument1 pageCurrent Resume - TechJesse Oliver SanfordNo ratings yet

- 62 0467 PDFDocument4 pages62 0467 PDFNgọc Thanh VũNo ratings yet

- Drilling Engineering Fundamentals (Jorge H.B. Sampayo)Document220 pagesDrilling Engineering Fundamentals (Jorge H.B. Sampayo)Davidson JustoNo ratings yet

- Omm Mitsubishi 220LC 2 R07Document195 pagesOmm Mitsubishi 220LC 2 R07SergeyNo ratings yet

- 1483 E IMS 8 StorageDocument10 pages1483 E IMS 8 StorageJuan Manuel Pescador ReyesNo ratings yet

- Keyence Laser MicrometerDocument20 pagesKeyence Laser MicrometerimrancenakkNo ratings yet

- Baker d65r HIPOTDocument2 pagesBaker d65r HIPOTjon1224100% (1)

- E-Book - Cutting Tools For CNC RouterDocument11 pagesE-Book - Cutting Tools For CNC RouterVictor ParvanNo ratings yet

- Worktips 01 Priming of PavementsDocument2 pagesWorktips 01 Priming of PavementsDilhara WickramaarachchiNo ratings yet

- User Manual User ManualDocument13 pagesUser Manual User ManualNeath MaroonNo ratings yet

- NAV 2015 Install Guide PDFDocument17 pagesNAV 2015 Install Guide PDFJacob Joseph OchiengNo ratings yet

- How To Carry Out Problem Solving: Value Chain Competitiveness (VCC)Document26 pagesHow To Carry Out Problem Solving: Value Chain Competitiveness (VCC)suhasNo ratings yet

- Huawei Lte Outdoor Cpe b2338 168 Product DescriptionDocument30 pagesHuawei Lte Outdoor Cpe b2338 168 Product DescriptionLars-ErikJägardNo ratings yet

- Spraying System Ssco Cat70 GDocument20 pagesSpraying System Ssco Cat70 GJonny FosterNo ratings yet

- Architectural Design IndraDocument7 pagesArchitectural Design IndraAshu JainNo ratings yet

- Anabond Epoxy Steel 4min TDSDocument2 pagesAnabond Epoxy Steel 4min TDSArun GuptaNo ratings yet