Professional Documents

Culture Documents

Utc3842 Youwangelectronics

Uploaded by

MindSet MarcosOriginal Description:

Original Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Utc3842 Youwangelectronics

Uploaded by

MindSet MarcosCopyright:

Available Formats

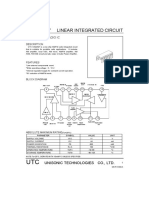

UTC3842 LINEAR INTEGRATED CIRCUIT

CURRENT MODE PWM CONTROL

CIRCUITS

DESCRIPTION

The UTC3842 provides the necessary features to

implement off-line or DC to DC fixed frequency current mode

DIP-8

control schemes with a minimal external parts count.

Internally implemented circuits include under-voltage lockout

featuring start up current less than 1mA,a precision

reference trimmed for accuracy at the error amp input, logic

to insure latched operation, a PWM comparator which also

provides current limit control, and a totem pole output stage

designed to source or sink high peak current. The output

stage, suitable for driving N channel MOSFETs, is low in the

off state. SOP-8

FEATURES

*Optimized for off-line and DC to DC converts *Double pulse Suppression

*Low start up current(<1mA) *High current totem pole output

*Automatic feed forward compensation *Internally trimmed band-gap reference

*Pulse-by-Pulse current limiting *500kHz operation

*Enhanced load response characteristics *Low Ro error amp

*Under-voltage lockout with hysteresis

BLOCK DIAGRAM

7 Vcc

Vref 8 5V REF S/R

5 GND

Internal U.V.L.O

Bias Vref

Good

1/2Vref Logic CURRENT

1/3Vref SENSE 7 Vcc

COMPAREATOR

VFB 2 R

ERROR 1V

AMPLIFIER PWM

COMP 1 LATCH

6 OUTPUT

S

CURRENT SENSE 3

5 GND

RT/CT 4 OSCILLATOR

YOUWANG ELECTRONICS CO.LTD 2005.06.09 V1.1

1

UTC3842 LINEAR INTEGRATED CIRCUIT

ABSOLUTE MAXIMUM RATINGS(Ta=25°C)

Characteristic Symbol Value Unit

Supply Voltage(Low Impedance Source) VCC 30 V

Supply Voltage(Icc<30mA) Vcc Self Limiting V

Output Current Io ±1 A

Output Energy(capacitive Load) 5 µJ

Analog Inputs(pin 2,3) VI(ANA) -0.3 to +6.3 V

Error Amplifier Output Sink Current ISINK(EA) 10 mA

Power Dissipation PD at Tamb≤25°C 1.0 W

Lead Temperature Tlead 300 °C

Storage Temperature Tstg -65~+150 °C

Note 1: Ta>25°C,PD derated with 8mW/°C.

ELECTRICAL CHARACTERISTICS

(0≤Ta≤70°C,VCC=15V,RT=10kΩ,CT=3.3nF,unless otherwise specified)

Characteristic Symbol Test Conditions Min Typ Max Units

Reference Section

Output Voltage VREF Tj=25°C,Io=1mA 4.90 5.00 5.10 V

Line Regulation ∆VREF 12≤VIN≤25V 6 20 mV

Load Regulation ∆VREF 1≤Io=20mA 6 25 mV

Temperature Stability (Note 2) 0.2 0.4 mV/°C

Total Output Variation Line,Load,Temp(note 2) 4.82 5.18 µV

Output Noise Voltage Vosc 10Hz≤f≤10kHz,Tj=25°C (note 2) 50 mV

Long term stability Ta=25°C,1000Hrs(note 2) 5 25 mV

Output Short Circuit ISC -30 -100 -180 mA

Oscillator Section

Initial Accuracy f Tj=25°C 47 52 57 kHz

Voltage Stability ∆f/∆Vcc 12≤Vcc≤25V 0.2 1 %

Temp stability Tmin≤TA≤Tmax(note 2) 5 %

Amplitude Vosc Vpin 4 peak to peak 1.7 V

Error Amplifier Section

Input Voltage VI(EA) Vpin 1=2.5V 2.42 2.50 2.58 V

Input Bias current IBIAS -0.3 -2 µA

AVOL 2 ≤Vo≤4V 60 90 dB

Unity Gain Bandwidth Tj=25°C (note 2) 0.7 1 mHz

PSRR I2 ≤Vcc≤25V 60 70 dB

Output Sink Current Isink Vpin 2=2.7V,Vpin 1=1.1V 2 6 mA

Output Source Current Isource Vpin 2=2.3V,Vpin 1=5V -0.5 -0.8 mA

Vout High VOH Vpin 2=2.3V, RL=15kΩ to GND 5 6 V

Vout Low VOL Vpin 2=2.7V,Vpin 1=1.1V 0.7 1.1 V

Current Sense section

Gain GV (note 3,4) 2.85 3 3.15 V/V

Maximum Input signal VI(MAX) Vpin 1=5V( note 3) 0.9 1 1.1 V

PSRR 12≤Vcc≤25V 70 dB

Input Bias Current IBIAS -2 -10 µA

Delay to Output Vpin 3=0 to 2V 150 300 ns

Output Section

Output low Level VOL Isink=20mA 0.1 0.4 V

Isink=200mA 1.5 2.2 V

YOUWANG ELECTRONICS CO.LTD 2005.06.09 V1.1

2

UTC3842 LINEAR INTEGRATED CIRCUIT

(continued)

Characteristic Symbol Test Conditions Min Typ Max Units

Output High Level VOH Isource=20mA 13 13.5 V

Isource=200mA 12 13.5 V

Rise Time tR Tj=25°C,CL=1nF(note 2) 50 150 ns

Fall Time tF Tj=25°C,CL=1nF(note 2) 50 150 ns

UVLO Saturation Vcc=5V,Isink=10mA 0.7 1.2 V

Under-Voltage Lockout Output Section

Start Threshold VTH(ST) 14.5 16 17.5 V

Min.Operating Voltage After Turn VOPR(min) 8.5 10 11.5 V

On

PWM Section

Maximum duty Cycle D(MAX) 95 07 100 %

Minimum Duty Cycle D(MIN) 0 %

Total Standby Current

Start-up Current IST 0.5 1 mA

Operating Supply Current ICC(opr) Vpin 2=Vpin 3=0V 11 17 mA

Vcc Zener Voltage Vz Icc=25mA 34 V

note 2:These parameters, although guaranteed ,are not 100% tested in production.

note 3:Parameters measured at trip point of latch with Vpin 2=0.

note 4:Gain defined as:

∆Vpin 1

A= ;0 ≤Vpin 3≤ 0.8V

∆Vpin 3

note 5:Adjust Vcc above the start threshold before setting at 15V.

OPEN-LOOP LABORATORY TEST CIRCUIT

Vref

4.7kΩ

RT

1 8 A Vcc

100kΩ

0.1µF

Error Amp 2 7

0.1µF

Adjust 1kΩ

/ 1W

4.7kΩ

Isense

3 6

Adjust

OUTPUT

5kΩ

4 5

CT

High peak current associated with capacitive loads in single point GND. The transistor and 5kΩ potentio -

necessitate careful grounding techniques. Timing and meter are used to sample the oscillator waveform and

bypass capacitors should be connected close to pin 5 apply an adjustable Ramp to Pin 3.

YOUWANG ELECTRONICS CO.LTD 2005.06.09 V1.1

3

UTC3842 LINEAR INTEGRATED CIRCUIT

UNDER-VOLTAGE LOCKOUT

Icc

Vcc >15mA

7 ON/OFF Command

to rest of IC

Von=16V

Voff=10V

<1mA

Von Voff

Vcc

During Under-Voltage Lockout, the output driver is activating the power switch with output leakage

biased to a high impedance state. Pin 6 should be currents.

shunt to GND with a bleeder resistor to prevent

ERROR AMPLIFIER CONFIGURATION

2.5V

0.5mA

Zi 2

Zf 1

Error amplifier can source or sink up to 0.5mA

CURRENT SENSE CIRCUIT

Error

Amplifier

2R

Is

R 1V

1

Current Sense

R Comparator

3

Rs C

5

Peak current (Is) determined by the formula:

Ismax=10V/Rs.

A small RC filter be required to suppress switch transients.

YOUWANG ELECTRONICS CO.LTD 2005.06.09 V1.1

4

UTC3842 LINEAR INTEGRATED CIRCUIT

SLOPE COMPENSATION

0.1µF

RT

4

CT

R1 Isense

R2

3

C Rsense

A fraction of the oscillator ramp can be resistively 50%.Note that capacitor C, forms a filter with R2 to

summed with the current sense signal to provide slope suppress the leading edge switch spikes.

compensation for converts requiring duty cycles over

OSCILLATOR SECTION

V4

Large RT

8 Small CT

INTERNAL

RT CLOCK

4 V4

CT

Small RT

5 INTERNAL

Large CT

CLOCK

Deadtime VS CT(RT>5k Ω) Timing Resistance Vs Frequency

100

100

td (µs) RT (kΩ)

CT=1nF

CT=2.2nF

10

CT=4.7nF

10 CT=10nF

CT=22nF

1

CT=47nF

CT=100nF

1

0.1 2 3 4 5 6

1 10 100 10 10 10 10 10

CT (nF) Frequency (Hz)

YOUWANG ELECTRONICS CO.LTD 2005.06.09 V1.1

5

UTC3842 LINEAR INTEGRATED CIRCUIT

SHUTDOWN TECHNIQUES

Shutdown UTC3842 can be accomplished by

two methods; either raise pin 3 above 1V or pull

1kΩ 1 Pin 1 below a voltage two diode drops above

8 ground. Either method caused the output of PWM

comparator to be high(refer to block diagram).The

PWM latch is reset dominant so that the output

330Ω

Shutdown

will remain low until the next clock cycle after the

3

shutdown condition at pins a and/or 3 is remov-

500Ω

ed .In one example, an externally latched shut -

Shutdown

To current down may be accomplished by adding an SCR

Sense resistor which be reset by cycling Vcc below the lower

UVLO threshold. At this point the reference turns

off allowing the SCR to reset.

TYPICAL PERFORMANCE CHARACTERISTICS

Vref Temperature Drift Istart Temperature Drift

5.02 550

Vref (V)

5.01 500

Vcc=15V

Vcc=9V

Io=1mA

5.00 450

Istart (mA)

4.99 400

4.98 350

4.97 300

4.96

250

-50 -25 0 25 50 75 100 125 150 -50 -25 0 25 50 75 100 125 150

Temperature ( ) ℃ ℃

Temperature ( )

15

Icc (mA)

14

Vcc=15V

Io=1mA

13

12

11

10

9

-50 -25 0 25 50 75 100 125 150

Temperature ( ) ℃

Icc Temperature Drift

YOUWANG ELECTRONICS CO.LTD 2005.06.09 V1.1

6

UTC3842 LINEAR INTEGRATED CIRCUIT

4 100

Vcc=15V

℃

Ta=+25 80 0

3 ℃

Ta=-55

Voltage Gain (dB)

Saturation Voltage (V)

60 -45

PHASE (Degree)

2 40 -90

20 -135

1

0 -180

0

2 3 4 5 6 7

0.01 0.1 1 10 10 10 10 10 10 10

Output Current Frequency (Hz)

(Sourse or Sink Current) (A)

Output Saturation Characteristics Error Amplifier Open-Loop

Frequency Response

YOUWANG ELECTRONICS CO.LTD 2005.06.09 V1.1

7

UTC3842 LINEAR INTEGRATED CIRCUIT

PACKAGE DIMENSIONS

DIP-8-300-2.54

SOP-8-225-1.27

YOUWANG ELECTRONICS CO.LTD 2005.06.09 V1.1

8

UTC3842 LINEAR INTEGRATED CIRCUIT

Attach

Revision History

Data REV Description Page

1.0 Original

2005.06.09 1.1 Add “PACKAGE OUTLINE DIP-8,SOP-8” 8

YOUWANG ELECTRONICS CO.LTD 2005.06.09 V1.1

9

You might also like

- Soldadora UTC3843DDocument9 pagesSoldadora UTC3843DChristian ormeñoNo ratings yet

- Current Mode PWMDocument9 pagesCurrent Mode PWMluis albertoNo ratings yet

- Ka3882/3/4/5 Smps Controller: Current Mode PWM ControllerDocument6 pagesKa3882/3/4/5 Smps Controller: Current Mode PWM Controllerjoil alvesNo ratings yet

- Current Mode PWM Controller: PIN Connection DescriptionDocument9 pagesCurrent Mode PWM Controller: PIN Connection Descriptionkudatroya43No ratings yet

- SMPS Controller: Features DescriptionDocument11 pagesSMPS Controller: Features DescriptionAdah BumboneNo ratings yet

- Bay Linear: Current Mode PWM ControllerDocument11 pagesBay Linear: Current Mode PWM ControllerShashikant PatilNo ratings yet

- Single Timer: Features DescriptionDocument13 pagesSingle Timer: Features DescriptionSonal GuptaNo ratings yet

- Single Timer: Features DescriptionDocument13 pagesSingle Timer: Features DescriptionSonal GuptaNo ratings yet

- IP3002 DatasheetDocument11 pagesIP3002 DatasheetSerhiiNo ratings yet

- 3842Document12 pages3842luisNo ratings yet

- UC3846Document10 pagesUC3846Polo Soldas Polo SoldasNo ratings yet

- 3842a DatasheetDocument8 pages3842a DatasheetVịnh DemoNo ratings yet

- 4 Pin Sop Phototransistor Photocoupler Ac Input Photocouple EL354N-G SeriesDocument11 pages4 Pin Sop Phototransistor Photocoupler Ac Input Photocouple EL354N-G SeriesCristian C. OlayaNo ratings yet

- SC1088 SilanMicroelectronicsDocument7 pagesSC1088 SilanMicroelectronicssoheil.zhalepouya1383No ratings yet

- TLE4266G SiemensSemiconductorGroupDocument9 pagesTLE4266G SiemensSemiconductorGroupDuranRod2013No ratings yet

- DP8600C YwDocument9 pagesDP8600C YwSURESH CHANDRA ROUTNo ratings yet

- 6脚电源IC资料及代换Document7 pages6脚电源IC资料及代换Justin NgNo ratings yet

- 3001B-DIP8: SANYO Electric Co.,Ltd. Semiconductor Bussiness HeadquartersDocument4 pages3001B-DIP8: SANYO Electric Co.,Ltd. Semiconductor Bussiness HeadquartersManuel MartinezNo ratings yet

- Telefono l3240b Twotone RingerDocument6 pagesTelefono l3240b Twotone Ringerblackbeast79No ratings yet

- Linear Integrated Circuit: Current Mode PWM ControllerDocument6 pagesLinear Integrated Circuit: Current Mode PWM ControllernermeenelnaggarNo ratings yet

- KA3842A IC Datasheet PDFDocument5 pagesKA3842A IC Datasheet PDFagarcosNo ratings yet

- SDC7500 enDocument7 pagesSDC7500 enodelaineNo ratings yet

- DatasheetDocument8 pagesDatasheetduc vinhNo ratings yet

- 4 Pin Sop Phototransistor Photocoupler EL357N-G Series: FeaturesDocument11 pages4 Pin Sop Phototransistor Photocoupler EL357N-G Series: FeaturesJuan Pablo CharrisNo ratings yet

- LM555Document14 pagesLM555Lactalis GenesisNo ratings yet

- NE555Document14 pagesNE555api-3720161100% (1)

- UTC TL1451 Linear Integrated Circuit: Dual Pulse-Width-Modulation Control CircuitsDocument5 pagesUTC TL1451 Linear Integrated Circuit: Dual Pulse-Width-Modulation Control CircuitsMarcos Gomes MisselNo ratings yet

- Silicon Monolithic Integrated Circuit LED Driver Control IC: Maximum Junction TemperatureDocument5 pagesSilicon Monolithic Integrated Circuit LED Driver Control IC: Maximum Junction TemperatureVenera Segunda ManoNo ratings yet

- UC384XA-BW Current Mode PWM Controller: (UC3842A-BW/ 43A-BW/ 44A-BW/ 45A-BW)Document10 pagesUC384XA-BW Current Mode PWM Controller: (UC3842A-BW/ 43A-BW/ 44A-BW/ 45A-BW)Damir SkarepNo ratings yet

- EL3H4-G Series PDFDocument11 pagesEL3H4-G Series PDFRodrigo GomezNo ratings yet

- KA2410 DatasheetDocument6 pagesKA2410 Datasheetauyantepuy73No ratings yet

- SE8117TADocument7 pagesSE8117TAdavid.gjeorgevskiNo ratings yet

- UC3842/UC3843/UC3844/UC3845: SMPS ControllerDocument12 pagesUC3842/UC3843/UC3844/UC3845: SMPS ControllerMohamed HaddadNo ratings yet

- DatasheetDocument6 pagesDatasheetFatah ZennouNo ratings yet

- Tca 785 DatasheetDocument18 pagesTca 785 DatasheetCarlos SilvaNo ratings yet

- L4960 PDFDocument16 pagesL4960 PDFedgar_dauzonNo ratings yet

- 4 Pin Dip Phototransistor Photocoupler EL817 Series: FeaturesDocument14 pages4 Pin Dip Phototransistor Photocoupler EL817 Series: FeaturesAli Ali AlialiNo ratings yet

- UC3842B 43 44 45. UC2842-3-4-5pdf PDFDocument15 pagesUC3842B 43 44 45. UC2842-3-4-5pdf PDFVictor Hugo Pulido QuiñonesNo ratings yet

- HS8108Document8 pagesHS8108Lenin AlvaradoNo ratings yet

- Single Timer: Features DescriptionDocument14 pagesSingle Timer: Features DescriptionAHMED MELIH ULUSOYNo ratings yet

- BD9270FDocument5 pagesBD9270FWercklein SanchezNo ratings yet

- Data Sheet BD 9270Document5 pagesData Sheet BD 9270senilsonNo ratings yet

- Datasheet l6506dDocument8 pagesDatasheet l6506dSIELAB C.A.No ratings yet

- 4-Ch BTL Driver For CD Player With 5V Output Voltage: DescriptionDocument10 pages4-Ch BTL Driver For CD Player With 5V Output Voltage: DescriptionJosé BenavidesNo ratings yet

- hs8108 PDFDocument9 pageshs8108 PDFUndibal Alejandro RivasNo ratings yet

- MP1484Document10 pagesMP1484Florian DimanciaNo ratings yet

- Electronic Tuning-Use FM Front End For Car Radio, Home StereosDocument8 pagesElectronic Tuning-Use FM Front End For Car Radio, Home StereosVeronicaGonzalezNo ratings yet

- UTC KA22427 DatasheetDocument3 pagesUTC KA22427 DatasheetSergio Daniel BarretoNo ratings yet

- AN6650 کنترل دور موتورDocument3 pagesAN6650 کنترل دور موتورJavad MohseniNo ratings yet

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Newnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1From EverandNewnes Electronics Circuits Pocket Book (Linear IC): Newnes Electronics Circuits Pocket Book, Volume 1Rating: 4.5 out of 5 stars4.5/5 (3)

- Analog Circuit Design Volume Three: Design Note CollectionFrom EverandAnalog Circuit Design Volume Three: Design Note CollectionRating: 3 out of 5 stars3/5 (2)

- D ft1208dj ft1208mj ft1204mj ft1204dj ft1208bj ft1208nj ft1204bj TDocument6 pagesD ft1208dj ft1208mj ft1204mj ft1204dj ft1208bj ft1208nj ft1204bj TMindSet MarcosNo ratings yet

- R1 IF SMDDocument2 pagesR1 IF SMDMindSet MarcosNo ratings yet

- Data Sheet: BTA204S Series D, E and F BTA204M Series D, E and FDocument8 pagesData Sheet: BTA204S Series D, E and F BTA204M Series D, E and FMindSet MarcosNo ratings yet

- 6th Central Pay Commission Salary CalculatorDocument15 pages6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Aula 1 Docs Vs 8eth06fppbf DatasheetDocument9 pagesAula 1 Docs Vs 8eth06fppbf DatasheetMindSet MarcosNo ratings yet

- Data SheetDocument5 pagesData SheetMindSet MarcosNo ratings yet

- STM 4472Document7 pagesSTM 4472MindSet MarcosNo ratings yet

- T-CON Samsung LN26A330-1Document2 pagesT-CON Samsung LN26A330-1MindSet MarcosNo ratings yet

- MGD623SDocument2 pagesMGD623SMindSet MarcosNo ratings yet

- MMS9014 L TPDocument2 pagesMMS9014 L TPMindSet MarcosNo ratings yet

- 24AA02 24LC02B 24FC02 2K I2C Serial EEPROM 2000170-2577009Document52 pages24AA02 24LC02B 24FC02 2K I2C Serial EEPROM 2000170-2577009MindSet MarcosNo ratings yet

- MBR1080CTDocument3 pagesMBR1080CTMindSet MarcosNo ratings yet

- DatasheetDocument15 pagesDatasheetMindSet MarcosNo ratings yet

- Philips+TPM18 7L+LADocument59 pagesPhilips+TPM18 7L+LAMindSet MarcosNo ratings yet

- Features 10N65 650V N-Channel MOSFET: TO-220F PackageDocument7 pagesFeatures 10N65 650V N-Channel MOSFET: TO-220F PackageMindSet MarcosNo ratings yet

- 5 GHZ Airmax Ac Cpe With Wi-Fi Management RadioDocument24 pages5 GHZ Airmax Ac Cpe With Wi-Fi Management RadioMindSet MarcosNo ratings yet

- 16042217224577Document15 pages16042217224577MindSet MarcosNo ratings yet

- Up Down Left Right L1 L2 Triangle Fork Square Circle R1 R2: KC2616 Wireless Gamepad TXDocument3 pagesUp Down Left Right L1 L2 Triangle Fork Square Circle R1 R2: KC2616 Wireless Gamepad TXMindSet MarcosNo ratings yet

- Schottky Rectifier 60 Amp: Bulletin PD-20635 Rev. A 12/01Document6 pagesSchottky Rectifier 60 Amp: Bulletin PD-20635 Rev. A 12/01MindSet MarcosNo ratings yet

- 2N3055 NPN Silicon Darlingtons: Absolute Maximum RatingsDocument3 pages2N3055 NPN Silicon Darlingtons: Absolute Maximum RatingsMindSet MarcosNo ratings yet

- 6c SMDDocument4 pages6c SMDMindSet MarcosNo ratings yet

- A78Rxxpic: DescriptionDocument7 pagesA78Rxxpic: DescriptionMindSet MarcosNo ratings yet

- Nevion Cp560 Data Sheet r1513Document4 pagesNevion Cp560 Data Sheet r1513dominhsonNo ratings yet

- Tata Mis ProjectDocument13 pagesTata Mis ProjectLove AuteNo ratings yet

- Document Control Procedure (20.10.14)Document18 pagesDocument Control Procedure (20.10.14)whmughal00100% (5)

- Using The Smith Chart in An E-Learning Approach: February 2012Document25 pagesUsing The Smith Chart in An E-Learning Approach: February 2012Naveen kumarNo ratings yet

- LTE L16 Troubleshooting With AMOSDocument43 pagesLTE L16 Troubleshooting With AMOSJohn P. GibsonNo ratings yet

- Sparcengine Ultra Axi: Oem Technical ManualDocument174 pagesSparcengine Ultra Axi: Oem Technical ManualDante Nuevo100% (1)

- Untitled PDFDocument17 pagesUntitled PDFGopi KrishnanNo ratings yet

- N68SC-M3S Bios 110321Document40 pagesN68SC-M3S Bios 110321agnaldoreis1988No ratings yet

- Impact of Basic Office Skills Correted NowDocument42 pagesImpact of Basic Office Skills Correted NowIfeji u. johnNo ratings yet

- Primo Theory Level 1Document56 pagesPrimo Theory Level 1rob c100% (13)

- Issues About Fintech Techfin and Cyber RiskDocument7 pagesIssues About Fintech Techfin and Cyber RiskBellamy1123No ratings yet

- Alex Michaelides Pacienta Tăcută PDFDocument358 pagesAlex Michaelides Pacienta Tăcută PDFOanea ElenaNo ratings yet

- Curriculum Computational Engineering and Networking PDFDocument26 pagesCurriculum Computational Engineering and Networking PDFVijay ShankarNo ratings yet

- Measures of CentraltendencyDocument33 pagesMeasures of CentraltendencyArjhay GironellaNo ratings yet

- Facebook LeetcodeDocument30 pagesFacebook LeetcodeRitik GargNo ratings yet

- Masroor Elahi ResumeDocument4 pagesMasroor Elahi ResumeMasroorNo ratings yet

- MDU Series Device V800R016C10SPH210 Patch Release Notes 01Document27 pagesMDU Series Device V800R016C10SPH210 Patch Release Notes 01Elvis JavierNo ratings yet

- VLC Media Player TutorialDocument107 pagesVLC Media Player TutorialRudyard VonNo ratings yet

- Internship Report Java ScriptDocument24 pagesInternship Report Java ScriptAbhishek GautamNo ratings yet

- SAC 305 Bar Solder Data SheetDocument2 pagesSAC 305 Bar Solder Data Sheetmuki10No ratings yet

- CFdesign 2010-Users GuideDocument457 pagesCFdesign 2010-Users GuidetomatlabNo ratings yet

- VDOT Cube Training FinalDocument164 pagesVDOT Cube Training FinalsuryaNo ratings yet

- E-Waste AssignmentDocument5 pagesE-Waste AssignmentRitesh Rai50% (2)

- Electronic Circuit Design and Analysis For Space ApplicationsDocument8 pagesElectronic Circuit Design and Analysis For Space ApplicationsH SMNo ratings yet

- Object Oriented ConceptDocument21 pagesObject Oriented ConceptKhagesh JoshNo ratings yet

- VLSI TutorialDocument16 pagesVLSI Tutorialthanos_3333No ratings yet

- SIC Multiwipe 1.1 ReadmeDocument8 pagesSIC Multiwipe 1.1 ReadmeGabriel BarretoNo ratings yet

- MJ15003 (NPN), MJ15004 (PNP) Complementary Silicon Power TransistorsDocument4 pagesMJ15003 (NPN), MJ15004 (PNP) Complementary Silicon Power Transistorsw4rh4ck3rNo ratings yet

- Results For Panalo Ako Translation From Tagalog To English: Ask GoogleDocument6 pagesResults For Panalo Ako Translation From Tagalog To English: Ask GoogleLebron FajardoNo ratings yet

- Internal Control QuestionnaireDocument4 pagesInternal Control Questionnairega_arnNo ratings yet