Professional Documents

Culture Documents

Description Features: Programmable Synchronous DC/DC Converter, Dual Low Dropout Regulator Controller

Description Features: Programmable Synchronous DC/DC Converter, Dual Low Dropout Regulator Controller

Uploaded by

thongleOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

Description Features: Programmable Synchronous DC/DC Converter, Dual Low Dropout Regulator Controller

Description Features: Programmable Synchronous DC/DC Converter, Dual Low Dropout Regulator Controller

Uploaded by

thongleCopyright:

Available Formats

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

1

DESCRIPTION

The SC1164/5 combines a synchronous voltage mode

controller with two low-dropout linear regulators

providing most of the circuitry necessary to implement

three DC/DC converters for powering advanced

microprocessors such as Pentium

II.

The SC1164/5 switching section features an integrated

5 bit D/A converter, pulse by pulse current limiting,

integrated power good signaling, and logic compatible

shutdown. The SC1164/5 switching section operates at

a fixed frequency of 200kHz, providing an optimum

compromise between size, efficiency and cost in the

intended application areas. The integrated D/A con-

verter provides programmability of output voltage from

2.0V to 3.5V in 100mV increments and 1.30V to 2.05V

in 50mV increments with no external components.

The SC1164/5 linear sections are low dropout regula-

tors. The SC1164 supplies 1.5V for GTL bus and 2.5V

for non-GTL I/O.

For the SC1165 both LDOs are adjustable.

Pentiumis a registered trademark of Intel Corporation

TEL:805-498-2111 FAX:805-498-3804 WEB:http://www.semtech.com

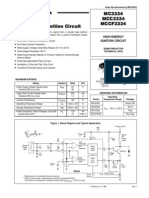

BLOCK DIAGRAM PIN CONFIGURATION

FEATURES

Synchronous design, enables no heatsink solution

95% efficiency (switching section)

5 bit DAC for output programmability

On chip power good function

Designed for Intel Pentium

ll requirements

1.5V, 2.5V or Adj. @ 1% for linear section

APPLICATIONS

Pentium

ll or Deschutes microprocessor supplies

Flexible motherboards

1.3V to 3.5V microprocessor supplies

Programmable triple power supplies

ORDERING INFORMATION

Part Number

(1)

Package

Linear

Voltage

Temp.

Range (T

J

)

SC1164CSW SO-24 1.5V/2.5V 0 to 125C

SC1165CSW SO-24 Adj. 0 to 125C

Note:

(1) Add suffix TR for tape and reel.

Top View

(24 Pin SOIC)

AGND

GATE1

LDOS1

LDOS2

VCC

OVP

PWRGOOD

CS-

CS+

PGNDH

DH

PGNDL

1

2

3

LDOV

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

VOSENSE

EN

BSTH

BSTL

DL

VID0

VID1

VID2

VID3

VID4

GATE2

2.5V/ADJ . 1.5V/ADJ .

1.265V FET

CONTROLLER

REF.

FET

CONTROLLER

REF.

LDOV

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

2

Parameter Symbol Maximum Units

VCC to GND VCC -0.3 to +7 V

PGND to GND 1 V

BST to GND -0.3 to +15 V

Operating Temperature Range T

A

0 to +70 C

J unction Temperature Range T

J

0 to +125 C

Storage Temperature Range T

STG

-65 to +150 C

Lead Temperature (Soldering) 10 seconds T

L

300 C

Thermal Impedance J unction to Ambient

J A

80 C/W

Thermal Impedance J unction to Case

J C

25 C/W

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

Unless specified: VCC =4.75V to 5.25V; GND =PGND =0V; VOSENSE =V

O

; 0mV <(CS+-CS-) <60mV; LDOV =11.4V to 12.6V; T

A

=25C

PARAMETER CONDITIONS MIN TYP MAX UNITS

Switching Section

Output Voltage I

O

=2A See Note 1.

Supply Voltage VCC 4.5 7 V

Supply Current VCC =5.0V 8 15 mA

Load Regulation I

O

=0.8A to 15A 1 %

Line Regulation 0.5 %

Current Limit Voltage 55 70 85 mV

Oscillator Frequency 175 200 225 kHz

Oscillator Max Duty Cycle 90 95 %

Peak DH Sink/Source Current BSTH-DH =4.5V, DH-PGNDH =3V 1 A

Peak DL Sink/Source Current BSTL-DL =4.5V, DL-PGNDL =3V 1 A

Output Voltage Tempco 65 ppm/

o

C

Gain (A

OL

) VOSENSE to V

O

35 dB

OVP threshold voltage 120 %

OVP source current V

OVP

=3.0V 10 mA

Power good threshold voltage 85 115 %

Dead time 50 100 ns

Linear Sections

Quiescent current LDOV =12V 5 mA

Output Voltage (LDO1 SC1164) 2.475 2.500 2.525 V

Output Voltage (LDO2 SC1164) 1.485 1.500 1.515 V

Reference Voltage (SC1165) 1.252 1.265 1.278 V

Feedback Pin Bias Current (SC1165) 10 uA

Gain (A

OL

) LDOS (1,2) to GATE (1,2) 90 dB

Load Regulation I

O

=0 to 8A

(2)

0.3 %

Line Regulation 0.3 %

Output Impedance 1 K

Notes: (1) See Output Voltage table.

(2) In application circuit.

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

3

Note:

(1) All logic level inputs and outputs are open

collector TTL compatible.

PIN DESCRIPTION

Pin Pin Name Pin Function

1 AGND Small Signal Analog and Digital Ground

2 GATE1 Gate Drive Output LDO1

3 LDOS1 Sense Input for LDO1

4 LDOS2 Sense Input for LDO2

5 VCC Input Voltage

6 OVP High Signal out if V

O

>setpoint +20%

7 PWRGOOD

(1)

Open collector logic output, high if V

O

within 10% of setpoint

8 CS- Current Sense Input (negative)

9 CS+ Current Sense Input (positive)

10 PGNDH Power Ground for High Side Switch

11 DH High Side Driver Output

12 PGNDL Power Ground for Low Side Switch

13 DL Low Side Driver Output

14 BSTL Supply for Low Side Driver

15 BSTH Supply for High Side Driver

16 EN

(1)

Logic low shuts down the converter;

High or open for normal operation.

17 VOSENSE Top end of internal feedback chain

18

VID4

(1)

Programming Input (MSB)

19

VID3

(1)

Programming Input

20

VID2

(1)

Programming Input

21

VID1

(1)

Programming Input

22

VID0

(1)

Programming Input (LSB)

23 LDOV +12V for LDO section

24 GATE2 Gate Drive Output LDO2

Top View

(24 Pin SOIC)

AGND

GATE1

LDOS1

LDOS2

VCC

OVP

PWRGOOD

CS-

CS+

PGNDH

DH

PGNDL

1

2

3

LDOV

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

VOSENSE

EN

BSTH

BSTL

DL

VID0

VID1

VID2

VID3

VID4

GATE2

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

4

OUTPUT VOLTAGE

Unless specified: VCC =5.00V; GND =PGND =0V; VOSENSE

=V

O

; 0mV <(CS+-CS-) <60mV; T

A

=25

o

C

PARAMETER CONDITIONS VID

43210

MIN TYP MAX UNITS

Output Voltage I

O

=2A in Application Circuit 01111 1.274 1.300 1.326

01110 1.323 1.350 1.377

01101 1.372 1.400 1.428

01100 1.421 1.450 1.479

01011 1.470 1.500 1.530

01010 1.527 1.550 1.573

01001 1.576 1.600 1.624

01000 1.625 1.650 1.675

00111 1.675 1.700 1.726

00110 1.724 1.750 1.776

00101 1.773 1.800 1.827

00100 1.822 1.850 1.878

00011 1.871 1.900 1.929

00010 1.921 1.950 1.979

00001 1.970 2.000 2.030

00000 2.019 2.050 2.081

11111 1.940 2.000 2.060

11110 2.058 2.100 2.142

11101 2.156 2.200 2.244

11100 2.254 2.300 2.346

11011 2.352 2.400 2.448

11010 2.450 2.500 2.550

11001 2.548 2.600 2.652

11000 2.646 2.700 2.754

10111 2.744 2.800 2.856

10110 2.842 2.900 2.958

10101 2.940 3.000 3.060

10100 3.038 3.100 3.162

10011 3.136 3.200 3.264

10010 3.234 3.300 3.366

10001 3.332 3.400 3.468

10000 3.430 3.500 3.570

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

5

1

2

V

5

V

E

N

V

I

D

3

V

I

D

2

V

I

D

1

V

I

D

0

O

V

P

V

I

D

4

P

W

R

G

D

V

C

C

_

C

O

R

E

V

L

I

N

2

V

I

N

L

I

N

V

L

I

N

1

C

1

0

.

1

u

F

L

14

u

H

R

4

5

m

O

h

m

C

1

8

0

.

1

u

F

+

C

1

4

1

5

0

0

u

F

+

C

1

5

1

5

0

0

u

F

+

C

1

6

1

5

0

0

u

F

+

C

1

7

1

5

0

0

u

F

+

C

3

1

5

0

0

u

F

+

C

2

1

5

0

0

u

F

R

1

1

0

C

1

3

0

.

1

u

F

Q

2

B

U

K

5

5

6

Q

1

B

U

K

5

5

6

C

5

0

.

1

u

F

Q

3

B

U

K

5

5

6

+

C

1

1

3

3

0

u

F

+

C

1

2

3

3

0

u

F

R

5

2

.

3

2

k

U

1

S

C

1

1

6

4

/

5

C

S

W

1 56

7 8 91

0

1

1

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

1

3

1

2

1

4

2

42

2

3

3

4

A

G

N

D

V

C

C

O

V

P

P

W

R

G

O

O

D

C

S

-

C

S

+

P

G

N

D

H

D

H

B

S

T

H

E

N

V

O

S

E

N

S

E

V

I

D

4

V

I

D

3

V

I

D

2

V

I

D

1

V

I

D

0

D

L

P

G

N

D

L

B

S

T

L

G

A

T

E

2

G

A

T

E

1

V

D

D

L

D

O

S

1

L

D

O

S

2

Q

4

B

U

K

5

5

6

+

C

9

3

3

0

u

F

+

C

1

0

3

3

0

u

F

R

6

1

.

0

0

k

R

1

2

*

R

1

3

*

R

1

5

*

R

1

4

*

+

C

2

1

3

3

0

u

F

+

C

2

2

3

3

0

u

F

R

1

6

T

B

D

R

1

7

1

0

0

k

R

1

8

1

0

0

k

N

O

T

E

:

F

O

R

S

C

1

1

6

4

,

R

1

2

,

R

1

3

,

R

1

4

A

N

D

R

1

4

A

R

E

N

O

T

R

E

Q

U

I

R

E

D

,

C

O

N

N

E

C

T

L

D

O

S

1

(

P

I

N

3

)

D

I

R

E

C

T

L

Y

T

O

V

L

I

N

1

T

O

G

E

N

E

R

A

T

E

2

.

5

V

O

U

T

P

U

T

.

C

O

N

N

E

C

T

L

D

O

S

2

(

P

I

N

4

)

D

I

R

E

C

T

L

Y

T

O

V

L

I

N

2

T

O

G

E

N

E

R

A

T

E

1

.

5

V

O

U

T

P

U

T

.

*

S

E

E

"

S

E

T

T

I

N

G

L

D

O

O

U

T

P

U

T

V

O

L

T

A

G

E

"

T

A

B

L

E

*

*

R

1

7

,

R

1

8

R

E

Q

U

I

R

E

D

I

F

V

I

N

L

I

N

C

A

N

B

E

P

R

E

S

E

N

T

W

I

T

H

O

U

T

1

2

V

B

E

I

N

G

P

R

E

S

E

N

T

.

*

*

*

*

(

N

O

R

M

A

L

L

Y

3

.

3

V

)

APPLICATION CIRCUIT

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

6

MATERIALS LIST

Qty. Reference Part/Description Vendor Notes

4 C1,C5,C13,C

18

0.1F Ceramic Various

6 C2,C3,C14-

C17

1500F/6.3V SANYO MV-GX or equiv. Low ESR

6 C9-C12,

C21, C22

330F/6.3V Various

1 L1 4H 8 Turns 16AWG on MICROMETALS T50-52D core

4 Q1,Q2,Q3,

Q4

See notes See notes FET selection requires trade-off between efficiency and

cost. Absolute maximum R

DS(ON)

=22 m for Q1,Q2

1 R4 5m IRC OAR-1 Series

1 R5 2.32k, 1%, 1/8W Various

1 R6 1k, 1%, 1/8W Various

1 R1 10, 5%, 1/8W Various

1 R12 1%, 1/8W Various See Table Below (Not required for SC1164)

1 R13 1%, 1/8W Various See Table Below (Not required for SC1164)

1 R14 1%, 1/8W Various See Table Below (Not required for SC1164)

1 R15 1%, 1/8W Various See Table Below (Not required for SC1164)

2 R17,R18 100k, 5%,1/8W Various Required if Voltage is applied to the linear FET(s) without

12V applied to SC1164/5

1 U1 SC1164/5CSW SEMTECH

SETTING LDO OUTPUT VOLTAGE

error t significan

cause not does term ) R I ( the that

so enough low be must R and R

ion clarificat for diagram layout See

resistor feedback Bottom R

resistor feedback Top R

current bias pin Feedback I

: Where

) R I (

R

) R R ( 265 . 1

V

A FB

B A

B

A

FB

A FB

B

B A

OUT

=

=

=

+

+

=

R

B

R

A

VOUT LDO1 (LDO2) R12 (R14) R13 (R15)

3.45V 105 182

3.30V 105 169

3.10V 102 147

2.90V 100 130

2.80V 100 121

2.50V 100 97.6

1.50V 100 18.7

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

7

70%

75%

80%

85%

90%

95%

0 2 4 6 8 10 12 14 16

Io (Amps)

E

f

f

i

c

i

e

n

c

y

3.5V Std

3.5V Sync

3.5V Sync Lo Rds

70%

75%

80%

85%

90%

95%

0 2 4 6 8 10 12 14 16

Io (Amps)

E

f

f

i

c

i

e

n

c

y

2.5V Std

2.5V Sync

2.5V Sync Lo Rds

70%

75%

80%

85%

90%

95%

0 2 4 6 8 10 12 14 16

Io (Amps)

E

f

f

i

c

i

e

n

c

y

2.8V Std

2.8V Sync

2.8V Sync Lo Rds

70%

75%

80%

85%

90%

95%

0 2 4 6 8 10 12 14 16

Io (Amps)

E

f

f

i

c

i

e

n

c

y

2.0V Std

2.0V Sync

2.0V Sync Lo Rds

Typical Ripple, Vo=2.8V, Io=10A

Typical Efficiency at Vo=2.5V

Typical Efficiency at Vo=3.5V Typical Efficiency at Vo=2.8V

Typical Efficiency at Vo=2.0V

Transient Response Vo=2.8V, Io=300mA to 10A

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

8

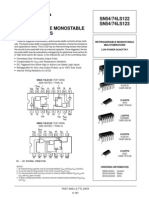

LAYOUT GUIDELINES

Careful attention to layout requirements are necessary

for successful implementation of the SC1164/5 PWM

controller. High currents switching at 200kHz are pre-

sent in the application and their effect on ground plane

voltage differentials must be understood and mini-

mized.

1). The high power parts of the circuit should be laid out

first. A ground plane should be used, the number and

position of ground plane interruptions should be such

as to not unnecessarily compromise ground plane in-

tegrity. Isolated or semi-isolated areas of the ground

plane may be deliberately introduced to constrain

ground currents to particular areas, for example the in-

put capacitor and bottom FET ground.

2). The loop formed by the Input Capacitor(s) (Cin), the

Top FET (Q1) and the Bottom FET (Q2) must be kept

as small as possible. This loop contains all the high cur-

rent, fast transition switching. Connections should be as

wide and as short as possible to minimize loop induc-

tance. Minimizing this loop area will a) reduce EMI, b)

lower ground injection currents, resulting in electrically

cleaner grounds for the rest of the system and c) mini-

mize source ringing, resulting in more reliable gate

switching signals.

3). The connection between the junction of Q1, Q2 and

the output inductor should be a wide trace or copper

region. It should be as short as practical. Since this

connection has fast voltage transitions, keeping this

connection short will minimize EMI. The connection be-

tween the output inductor and the sense resistor should

be a wide trace or copper area, there are no fast volt-

age or current transitions in this connection and length

is not so important, however adding unnecessary

impedance will reduce efficiency.

Layout diagram for the SC1164/5

Vout

12V IN

5V Vo Lin1

Vo Lin2

5V

4uH

5mOhm

+

Cout

+

Cin

10

Q2

0.1uF

Q3

+

Cout Lin1

2.32k

Q4

+

Cout Lin2

1.00k

RB1

RA1

RA2

RB2

+

Cin Lin

SC1164/5

AGND

1

VCC

5

OVP

6

PWRGOOD

7

CS-

8

CS+

9

PGNDH

10

DH

11

BSTH

15

EN

16

VOSENSE

17

VID4

18

VID3

19

VID2

20

VID1

21

VID0

22

DL

13

PGNDL

12

BSTL

14

GATE2

24

GATE1

2

LDVO

23

LDOS1

3

LDOS2

4 Q1

0.1uF

Heavy lines indicate

high current paths.

are not required. LDOS1 connects to

For SC1164, RA1, RA2, RB1 and RB2

Vo Lin1, LDOS2 connects to Vo Lin2

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

9

Vout

5V

+

+

4) The Output Capacitor(s) (Cout) should be located

as close to the load as possible, fast transient load

currents are supplied by Cout only, and connections

between Cout and the load must be short, wide cop-

per areas to minimize inductance and resistance.

5) The SC1164/5 is best placed over a quiet ground

plane area, avoid pulse currents in the Cin, Q1, Q2

loop flowing in this area. PGNDH and PGNDL should

be returned to the ground plane close to the package.

The AGND pin should be connected to the ground

side of (one of) the output capacitor(s). If this is not

possible, the AGND pin may be connected to the

ground path between the Output Capacitor(s) and the

Cin, Q1, Q2 loop. Under no circumstances should

AGND be returned to a ground inside the Cin, Q1, Q2

loop.

6) Vcc for the SC1164/5 should be supplied from the

5V supply through a 10 resistor, the Vcc pin should

be decoupled directly to AGND by a 0.1F ceramic

capacitor, trace lengths should be as short as possi-

ble.

7) The Current Sense resistor and the divider across

it should form as small a loop as possible, the traces

running back to CS+and CS- on the SC1164/5 should

run parallel and close to each other. The 0.1F ca-

pacitor should be mounted as close to the CS+and

CS- pins as possible.

8) Ideally, the grounds for the two LDO sections

should be returned to the ground side of (one of) the

output capacitor(s).

Currents in various parts of the power section

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

10

COMPONENT SELECTION

SWITCHING SECTION

OUTPUT CAPACITORS - Selection begins with the

most critical component. Because of fast transient load

current requirements in modern microprocessor core

supplies, the output capacitors must supply all transient

load current requirements until the current in the output

inductor ramps up to the new level. Output capacitor

ESR is therefore one of the most important criteria. The

maximum ESR can be simply calculated from:

step current Transient I

excursion voltage transient Maximum V

Where

I

V

R

t

t

t

t

ESR

=

=

Each Capacitor Total

Technology C

(F)

ESR

(m)

Qty.

Rqd.

C

(F)

ESR

(m)

Low ESR Tantalum 330 60 6 2000 10

OS-CON 330 25 3 990 8.3

Low ESR Aluminum 1500 44 5 7500 8.8

( )

O IN

t

ESR

V V

I

C R

L

OSC

IN

L

f L 4

V

I

RIPPLE

=

IN

O

) on ( DS

2

O COND

V

V

cycle duty =

where

R I P

=

2

IN O SW

10 V I P

=

4

f ) t t ( V I

P

OSC f r IN O

SW

+

=

OSC IN RR RR

f V Q P =

For example, to meet a 100mV transient limit with a

10A load step, the output capacitor ESR must be less

than 10m. To meet this kind of ESR level, there are

three available capacitor technologies.

The choice of which to use is simply a cost/perfor-

mance issue, with Low ESR Aluminum being the

cheapest, but taking up the most space.

INDUCTOR - Having decided on a suitable type and

value of output capacitor, the maximum allowable

value of inductor can be calculated. Too large an in-

ductor will produce a slow current ramp rate and will

cause the output capacitor to supply more of the tran-

sient load current for longer - leading to an output volt-

age sag below the ESR excursion calculated above.

The maximum inductor value may be calculated from:

The calculated maximum inductor value assumes 100%

duty cycle, so some allowance must be made. Choosing

an inductor value of 50 to 75% of the calculated maxi-

mum will guarantee that the inductor current will ramp

fast enough to reduce the voltage dropped across the

ESR at a faster rate than the capacitor sags, hence en-

suring a good recovery from transient with no additional

excursions.

We must also be concerned with ripple current in the

output inductor and a general rule of thumb has been to

allow 10% of maximum output current as ripple current.

Note that most of the output voltage ripple is produced

by the inductor ripple current flowing in the output capac-

itor ESR. Ripple current can be calculated from:

Ripple current allowance will define the minimum permit-

ted inductor value.

POWER FETS - The FETs are chosen based on several

criteria with probably the most important being power

dissipation and power handling capability.

TOP FET - The power dissipation in the top FET is a

combination of conduction losses, switching losses and

bottom FET body diode recovery losses.

a) Conduction losses are simply calculated as:

b) Switching losses can be estimated by assuming a

switching time, if we assume 100ns then:

or more generally,

c) Body diode recovery losses are more difficult to esti-

mate, but to a first approximation, it is reasonable to as-

sume that the stored charge on the bottom FET body

diode will be moved through the top FET as it starts to

turn on. The resulting power dissipation in the top FET

will be:

To a first order approximation, it is convenient to only

consider conduction losses to determine FET suitability.

For a 5V in; 2.8V out at 14.2A requirement, typical FET

losses would be:

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

11

) 1 ( R I P

) on ( DS

2

O COND

=

FET type R

DS(on)

(m) P

D

(W) Package

BUK556H 22 2.48 TO220

IRL2203 7.0 0.79 D

2

PAK

Si4410 13.5 1.53 SO-8

FET type R

DS(on)

(m) P

D

(W) Package

BUK556H 22 1.95 TO220

IRL2203 7.0 0.62 D

2

PAK

Si4410 13.5 1.20 SO-8

BOTTOM FET - Bottom FET losses are almost entirely

due to conduction. The body diode is forced into conduc-

tion at the beginning and end of the bottom switch con-

duction period, so when the FET turns on and off, there

is very little voltage across it, resulting in low switching

losses. Conduction losses for the FET can be deter-

mined by:

For the example above:

Each of the package types has a characteristic thermal

impedance, for the TO-220 package, thermal impedance

is mostly determined by the heatsink used. For the sur-

face mount packages on double sided FR4, 2 oz printed

circuit board material, thermal impedances of 40

o

C/W

for the D

2

PAK and 80

o

C/W for the SO-8 are readily

achievable. The corresponding temperature rise is de-

tailed below:

Temperature rise (

o

C)

FET type Top FET Bottom FET

BUK556H 49.6

(1)

39.0

(1)

IRL2203 31.6 24.8

Si4410 122.4 96

(1) With 20

o

C/W Heatsink

It is apparent that single SO-8 Si4410 are not adequate for

this application, but by using parallel pairs in each posi-

tion, power dissipation will be approximately halved and

temperature rise reduced by a factor of 4.

INPUT CAPACITORS - since the RMS ripple current in

the input capacitors may be as high as 50% of the out-

put current, suitable capacitors must be chosen ac-

cordingly. Also, during fast load transients, there may

be restrictions on input di/dt. These restrictions require

useable energy storage within the converter circuitry,

either as extra output capacitance or, more usually,

additional input capacitors. Choosing low ESR input

capacitors will help maximize ripple rating for a given

size.

PROGRAMMABLE SYNCHRONOUS DC/DC

CONVERTER, DUAL LOW DROPOUT

REGULATOR CONTROLLER

1999 SEMTECH CORP.

October 25, 1999

652 MITCHELL ROAD NEWBURY PARK CA 91320

SC1164/5

12

OUTLINE DRAWING - SO-24

J EDEC MS-013AD

B17104B

ECN 99-667

You might also like

- Skhi 22B DatasheetDocument9 pagesSkhi 22B DatasheetRakesh RoyNo ratings yet

- Isolated Flyback Switching Regulator W - 9V OutputDocument16 pagesIsolated Flyback Switching Regulator W - 9V OutputCasey DialNo ratings yet

- Schema Inverter Gh214aDocument27 pagesSchema Inverter Gh214aTvcrepairNo ratings yet

- LCT B85TDU22H Service ManualDocument59 pagesLCT B85TDU22H Service ManualCristina NistorNo ratings yet

- FAN8082 (KA3082N) : Bi-Directional DC Motor DriverDocument13 pagesFAN8082 (KA3082N) : Bi-Directional DC Motor DriverFrancisco Hernandez MartinezNo ratings yet

- Voltage-Controlled Oscillator: ... The Analog Plus CompanyDocument24 pagesVoltage-Controlled Oscillator: ... The Analog Plus CompanyMoltrevNo ratings yet

- Ka3082 Controlador de Motores CCDocument12 pagesKa3082 Controlador de Motores CCshibatoyanNo ratings yet

- LT1076 5Document8 pagesLT1076 5Marquis DavidNo ratings yet

- Delta PLC DVP SS ModelDocument4 pagesDelta PLC DVP SS ModelTarun SonwaneNo ratings yet

- IC 3842 para FonteDocument8 pagesIC 3842 para FonteTomNedscNo ratings yet

- STP9NK65ZFPDocument16 pagesSTP9NK65ZFPJacson FagundesNo ratings yet

- 3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesDocument12 pages3A, 23V, 340Khz Synchronous Step-Down Converter: General Description FeaturesGiovanni Carrillo VillegasNo ratings yet

- LCD221SD Service ManualDocument41 pagesLCD221SD Service Manual1cvbnmNo ratings yet

- ST 232Document11 pagesST 232Negru P. PlantatieNo ratings yet

- CPWRAN10Document5 pagesCPWRAN10Vasco RodriguesNo ratings yet

- An 1599Document20 pagesAn 1599nisha770No ratings yet

- Datasheet (LT1074)Document16 pagesDatasheet (LT1074)HermesSanchezNo ratings yet

- HV9910BDB7 HV9910B PFC 40W LED Driver Demoboard: Specifications General DescriptionDocument5 pagesHV9910BDB7 HV9910B PFC 40W LED Driver Demoboard: Specifications General DescriptionNT372No ratings yet

- CA3102Document11 pagesCA3102bonaparteCWBNo ratings yet

- AM5898NDocument11 pagesAM5898NGabriel Cosme VazquezNo ratings yet

- LG - 32lb9rta Me Eay41970901 PDFDocument139 pagesLG - 32lb9rta Me Eay41970901 PDFLuděk CsibaNo ratings yet

- LC75816E, 75816W: 1/8 To 1/10 Duty Dot Matrix LCD Display Controllers/Drivers With Key Input FunctionDocument44 pagesLC75816E, 75816W: 1/8 To 1/10 Duty Dot Matrix LCD Display Controllers/Drivers With Key Input FunctionajitajimalNo ratings yet

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDocument10 pagesNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânNo ratings yet

- NCV47821 3.3 V To 20 V Adjustable Dual LDO With Adjustable Current Limit and Diagnostic FeaturesDocument15 pagesNCV47821 3.3 V To 20 V Adjustable Dual LDO With Adjustable Current Limit and Diagnostic FeaturesTestronicpartsNo ratings yet

- Modbus-1 3eDocument4 pagesModbus-1 3ekelpiusNo ratings yet

- Data SheetDocument6 pagesData SheetTuấn Âm Thanh Hi-endNo ratings yet

- UDN2916Document10 pagesUDN2916ejoaomelchiorsNo ratings yet

- DVP20SX211RDocument8 pagesDVP20SX211RcurielvicNo ratings yet

- Uc 3845Document23 pagesUc 3845Bahram RN100% (1)

- Transformer Driver For Isolated Power Supplies: Features ApplicationsDocument29 pagesTransformer Driver For Isolated Power Supplies: Features Applicationsngongpro27No ratings yet

- AM5888SDocument10 pagesAM5888SproctepNo ratings yet

- TB6560AHQ 4-Axis CNC Driver PDFDocument7 pagesTB6560AHQ 4-Axis CNC Driver PDFMai HuyNo ratings yet

- DRV 8811Document22 pagesDRV 8811nelson_loboNo ratings yet

- Ibm Lenovo E420 COMPAL LA-1331Document83 pagesIbm Lenovo E420 COMPAL LA-1331Abubakar SidikNo ratings yet

- Ldrxxyy: Very Low Drop Dual Voltage RegulatorDocument14 pagesLdrxxyy: Very Low Drop Dual Voltage RegulatorCaterine OliveiraNo ratings yet

- Data SheetDocument8 pagesData SheetMauro VianaNo ratings yet

- Ucc 28220Document32 pagesUcc 28220urpublicNo ratings yet

- UC3825ADWDocument15 pagesUC3825ADWmichaelliu123456No ratings yet

- ADC0804 DatasheetDocument48 pagesADC0804 DatasheetSaurabh AnmadwarNo ratings yet

- RD 2015-05-001-V01 Evaluation Board For M909 ModulesDocument24 pagesRD 2015-05-001-V01 Evaluation Board For M909 ModulesasokanenNo ratings yet

- FAN7314 LCD Backlight Inverter Drive IC: Features DescriptionDocument3 pagesFAN7314 LCD Backlight Inverter Drive IC: Features DescriptionMaha DevanNo ratings yet

- MAX1858 Evaluation Kit: General Description FeaturesDocument7 pagesMAX1858 Evaluation Kit: General Description Features9183290782No ratings yet

- Ucc2800 PDFDocument22 pagesUcc2800 PDFgarrycNo ratings yet

- Single Ended Active Clamp/Reset PWM: Features DescriptionDocument16 pagesSingle Ended Active Clamp/Reset PWM: Features Descriptioncatsoithahuong84No ratings yet

- 35W DVD Power Supply With ICE2A265Document12 pages35W DVD Power Supply With ICE2A265BUDINo ratings yet

- Aplication Note For TOP SwitchDocument9 pagesAplication Note For TOP SwitchSunil SonavaneNo ratings yet

- Viper 100Document8 pagesViper 100SeanNo ratings yet

- Elevador VoltajeDocument10 pagesElevador VoltajeFernando AugustoNo ratings yet

- 2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial InterfaceDocument20 pages2.7V 4-Channel/8-Channel 10-Bit A/D Converters With SPI™ Serial Interfacejoseleomi_limaNo ratings yet

- 180w SourceDocument2 pages180w SourceMustata AlexandruNo ratings yet

- Irams 06 Up 60 ADocument18 pagesIrams 06 Up 60 AAndré Roberto EvangelistaNo ratings yet

- Datasheet MC3334Document6 pagesDatasheet MC3334odipasNo ratings yet

- IRAMX16UP60ADocument18 pagesIRAMX16UP60Atheylor1990No ratings yet

- 74 Ls 121Document10 pages74 Ls 121krlossnNo ratings yet

- MCP3040 DatasheetDocument40 pagesMCP3040 Datasheetjiajun898No ratings yet

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsFrom EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsRating: 5 out of 5 stars5/5 (1)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2No ratings yet

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsFrom EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsRating: 3.5 out of 5 stars3.5/5 (6)

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1From EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Rating: 2.5 out of 5 stars2.5/5 (3)