Professional Documents

Culture Documents

E6420 2f800 - Compal - LA-6592P - r10

E6420 2f800 - Compal - LA-6592P - r10

Uploaded by

Vincent TonOriginal Title

Copyright

Available Formats

Share this document

Did you find this document useful?

Is this content inappropriate?

Report this DocumentCopyright:

Available Formats

E6420 2f800 - Compal - LA-6592P - r10

E6420 2f800 - Compal - LA-6592P - r10

Uploaded by

Vincent TonCopyright:

Available Formats

A

COMPAL CONFIDENTIAL

MODEL NAME : PAL51/53

PCB NO : LA-6592P (DAA00001V10)

BOM P/N : 43192931L01

GPIO MAP: E3 Master GPIO Map10102010.xlsx

E3 MACALLAN 14" SG

rPGA Sandy Bridge +

FCBGA PCH Cougar Point-M

2011-1-13

REV : 1.0(A00)

@ : Nopop Component

CONN@ : ME controll and stuff by default

MB Type

BOM P/N

TPM EN/ TCM DIS

43192931L01

1@

3@

TPM DIS/ TCM EN

43192931L02

2@

4@

TPM DIS/ TCM DIS

43192931L03

2@

3@

ATG TPM EN/ TCM DIS

43192931L11

1@

3@

ATG TPM DIS/ TCM EN

43192931L12

2@

4@

ATG TPM DIS/ TCM DIS

43192931L13

2@

3@

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

MB PCB

Part Number

Description

DAA00001V10

PCB 0FE LA-6592P REV0 M/B DIS

Title

Cover Sheet

Size

Rev

1.0

LA-6592P

Date:

Document Number

Thursday, January 13, 2011

Sheet

E

of

75

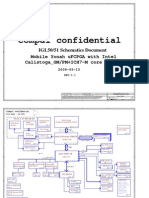

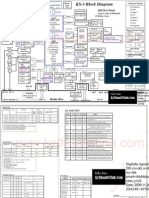

Block Diagram Compal confidential

Model: PAL51/53

DDRIII-DIMM X2

Memory BUS (DDR3)

LVDS Switch

PI3LVD400ZFEX

LVDS CONN

PAGE 24

iLVDS

PAGE 23

dLVDS

HDMI Repeater

HDMI CONN

PAGE 26

PS121

DPE

PAGE 26

PAGE 40

PAGE 46-51

dVGA

VGA

CRT CONN

PAGE 24

FDI

DMI2

Lane x 8

Lane x 4

INTEL

BT

PAGE 43

Camera

SATA Repeater

MAX4951BE

SATA

USB

Trough eDP Cable

E-SATA

PAGE 39

PAGE 25

SATA5

DOCK LAN

iVGA

Video Switch

MAX14885E

DAI

USB[8,9]

Touch Screen

PAGE 6-11

DPC

DPD

VGA

DOCKING PORT

PAGE 12,13

988 pins

PEG

N12M-NS

BANK 0, 1, 2, 3, 4 ,5 ,6 ,7

1066/1333MHz

Sandy Bridge

4MB (Socket 988B)

rPGA CPU

2560

COUGAR POINT-M

USB Port

PAGE 39

BGA

USB Port

PAGE 38

On IO board

iLVDS

2560

2

USB Port

PAGE 14-21

2062

Card reader

SDXC/MMC/MS

PCIE x1

OZ600FJ0LN

PAGE 35

EXPRESS

Card

PCIE5

PCIE2

PAGE 35

PCI Express BUS 100MHz

1/2 Mini Card

Flash

PAGE 37

1/2 Mini Card Full Mini Card

WLAN

WWAN/UWB

PAGE 36

USB10

USB6

PAGE 36

USB4

Smart Card

PAGE 33

CPU XDP Port

PAGE 7

RFID

PAGE 33

PCH XDP Port

PAGE 14

Thermal

PWM FAN

GUARDIAN III

EMC4022

PAGE 22

DOCK LAN

SPI

S-ATA 0/1 6GB/s, S-ATA 2/3/4/5 3GB/s

LPC BUS

China TPM1.2

SSX44B

PAGE 36

PAGE 34

PAGE 14

USH TPM1.2

BCM5882

PAGE 28

FP_USB

PAGE 30

HeadPhone &

MIC Jack

DAI

RJ11

BC BUS

on IO board

E-Module

RJ45

on IO board

PAGE 28

USB7

LAN SWITCH

PI3L720 PAGE 32

INT.Speaker

MDC

HDD

PAGE 14

16M 4K sector

PCIE4

SMSC SIO

ECE5028

PAGE 30

W25Q16BVSSIG

PAGE 33,34

Fingerprint

CONN

PAGE 23

HDA Codec

92HD90B2

SATA Repeater

MAX4951BE

W25X64ZE

64M 4K sector

PAGE 33

PAGE 32

SATA

33MHz

USB5

TDA8034HN

Intel Lewisville

82579LM

HD Audio I/F

Option

PCIE1

on IO board

USB Port

PCI Express BUS 100MHz

PCIE3

PAGE 38

To Docking side

Dig.

MIC

PAGE 29

Trough eDP Cable

PAGE 41

SMSC KBC

MEC5055

PAGE 22

WiFi ON/OFF &

Power ON/OFF SW

PAGE 42

PAGE 31

DELL CONFIDENTIAL/PROPRIETARY

DC/DC Interface

PAGE 44

TP CONN

PAGE 43

LED

KB CONN

PAGE 43

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

PAGE 45

Title

DIS Block Diagram

Size

Rev

1.0

LA-6592P

Date:

Document Number

Thursday, January 13, 2011

Sheet

E

of

75

POWER STATES

Signal

SLP

S3#

SLP

S4#

SLP

S5#

SLP

A#

S0 (Full ON) / M0

HIGH

HIGH

HIGH

HIGH

S3 (Suspend to RAM) / M3

LOW

HIGH

HIGH

S4 (Suspend to DISK) / M3

LOW

LOW

S5 (SOFT OFF) / M3

LOW

S3 (Suspend to RAM) / M-OFF

LOW

State

M

PLANE

SUS

PLANE

RUN

PLANE

ON

ON

ON

ON

HIGH

ON

ON

ON

HIGH

HIGH

ON

ON

LOW

LOW

HIGH

ON

HIGH

HIGH

LOW

ON

ALWAYS

PLANE

USB PORT#

CLOCKS

JUSB2 (Right side 1)

ON

JUSB3 (Right side 2)

OFF

OFF

JESA1 (Right Side ESATA)

OFF

OFF

OFF

JESA1 (Ext Left Side )

ON

OFF

OFF

OFF

WLAN

OFF

ON

OFF

OFF

WWAN

JMINI3(Flash)

USH->BIO

DOCKING

DOCKING

10

Express card

11

Bluetooth

12

Camera

13

LCD Touch

BIO

NA

S4 (Suspend to DISK) / M-OFF

LOW

LOW

HIGH

LOW

ON

OFF

OFF

OFF

OFF

S5 (SOFT OFF) / M-OFF

LOW

LOW

LOW

LOW

ON

OFF

OFF

OFF

OFF

PCH

PM TABLE

C

power

plane

+15V_ALW

+3.3V_SUS

+5V_RUN

+3.3V_M

+5V_ALW

+1.5V_MEM

+3.3V_RUN

+1.05V_M +1.05V_M

+3.3V_ALW_PCH

+1.8V_RUN

+3.3V_RTC_LDO

+1.5V_RUN

+3.3V_M

(M-OFF)

+0.75V_DDR_VTT

+VCC_CORE

+1.05V_RUN_VTT

+1.05V_RUN

State

DESTINATION

SATA

DESTINATION

SATA 0

HDD

SATA 1

ODD/ E3 Module Bay

SATA 2

NA

SATA 3

NA

ESATA

S0

ON

ON

ON

ON

ON

SATA 4

S3

ON

ON

OFF

ON

OFF

SATA 5

S5 S4/AC

ON

OFF

OFF

ON

OFF

S5 S4/AC don't exist

OFF

OFF

OFF

OFF

OFF

Dock

USH

need to update Power Status and PM Table

PCI EXPRESS

Lane 1

MINI CARD-1 WWAN

Lane 2

MINI CARD-2 WLAN

Lane 3

Express card

Lane 4

E3 Module Bay (USB3)

Connetion

Lane 5

1/2vMINI CARD-3 PCIE

Port C

Dock DP port 2

Lane 6

MMI

Port D

Dock DP port 1

Lane 7

10/100/1G LOM

Port E

MB HDMI Conn

Lane 8

None

DSC DP/HDMI Port

DESTINATION

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Index and Config.

Size

Rev

1.0

LA-6592P

Date:

Document Number

Thursday, January 13, 2011

Sheet

1

of

75

EN_INVPWR

FDC654P

Q21

MODC_EN

HDDC_EN

+BL_PWR_SRC

ADAPTER

PGPU_PWR_EN

D

1.05V_VTTPWRGD

+PWR_SRC

ISL95870A

(PU15)

+GPU_CORE

ISL95870AH

(PU13)

+VCC_SA

BATTERY

1.05V_0.8V_PWROK

MAX17411

(PU9)

SI3456BDV

(Q27)

SI3456BDV

(Q30)

+5V_HDD

+5V_MOD

+VCC_GFXCORE

ALWON

CHARGER

+15V_ALW

SN0608098

(PU2)

+5V_ALW

RUN_ON

SI4164DY

(Q50)

+1.5V_MEM

CPU1.5V_S3_GATE

+0.75V_DDR_VTT

NTGS4141N

(Q59)

S13456

(Q54)

SI3456

(Q34)

M_ON

AUX_ON

SI3456

(Q49)

+5V_RUN

RUN_ON

SUS_ON

M_ON

SI3456

(Q38)

PCH_ALW_ON

(PU6)

CPU_VTT_ON

(PU7)

+1.8V_RUN +1.05V_RUN_VTT

RUN_ON

AO4728

(QC3)

SN1003055

NTMS4920

(Q55)

SI3456

(Q58)

B

+1.05V_M

RUN_ON

+VCC_CORE

TPS51311

(PU4)

RUN_ON

0.75V_VR_EN

RT9026GFP

(PU5)

DDR_ON

RT8209BGQW

(PU3)

1.05V_0.8V_PWROK

MAX17411

(PU9)

SN1003055

AUX_EN_WOWL

+3.3V_ALW

+3.3V_WLAN

+3.3V_ALW_PCH

+3.3V_SUS

+3.3V_LAN

+3.3V_RUN

+3.3V_M

Pop option

+1.0V_LAN

Pop option

+3.3V_M

SI4164

(Q63)

+0.8V_VCCSA

+1.5V_CPU_VDDQ

DELL CONFIDENTIAL/PROPRIETARY

+1.05V_RUN

+1.5V_RUN

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Power Rail

Size

Rev

1.0

LA-6592P

Date:

Document Number

Thursday, January 13, 2011

Sheet

1

of

75

@ 2.2K

SMBUS Address [0x9a]

+3.3V_ALW_PCH

@ 2.2K

H14

MEM_SMBCLK

C9

MEM_SMBDATA

202

2N7002

200

DIMMA

SMBUS Address [A0]

DIMMB

SMBUS Address [A4]

2N7002

2.2K

PCH

D

202

+3.3V_LAN

2.2K

C8

G12

M16

28

LAN_SMBDATA

31

200

53

SML1_SMBCLK

A5

SMBUS Address [C8]

LOM

E14

SML1_SMBDATA

3A

LAN_SMBCLK

2.2K

53

3A

2.2K

B4

DOCK_SMB_CLK

A3

DOCK_SMB_DAT

+3.3V_ALW

SMBUS Address

127

129

DOCKING

2.2K

C

2.2K

1B

1B

XDP2

51

2.2K

1A

SMBUS Address [TBD]

+3.3V_ALW_PCH

B6

1A

XDP1

51

2.2K

SMBUS Address [TBD]

2.2K

APR_EC: 0x48

SPR_EC: 0x70

MSLICE_EC: 0x72

USB: 0x59

AUDIO: 0x34

SLICE_BATTERY: 0x17

SLICE_CHARGER: 0x13

2.2K

+3.3V_RUN

14

13

G Sensor

SMBUS Address [0x3B]

+3.3V_ALW

30

B5

LCD_SMBCLK

A4

LCD_SMDATA

WWAN

32

SMBUS Address [TBD]

2.2K

KBC

2.2K

1C

1C

A56

B59

PBAT_SMBCLK

PBAT_SMBDAT

+3.3V_ALW

100 ohm

100 ohm

BATTERY

CONN

SMBUS Address [0x16]

USH

SMBUS Address [0xa4]

2.2K

2.2K

+3.3V_ALW

USH_SMBCLK

M9

1E

A50

B53

USH_SMBDAT

L9

1E

B

2.2K

2.2K

MEC 5055

2B

A49

CARD_SMBCLK

2B

B52

CARD_SMBDAT

+3.3V_SUS

7

8

Express card

SMBUS Address [TBD]

2.2K

2.2K

CHARGER_SMBCLK

10

A47

CHARGER_SMBDAT

1G

1G

+3.3V_ALW

B50

Charger

SMBUS Address [0x12]

2.2K

2.2K

2D

B7

BAY_SMBDAT

2D

A7

BAY_SMBCLK

+3.3V_ALW

29

30

E3 Module Bay

SMBUS Address [0xd2]

2.2K

2.2K

2A

2A

+3.3V_RUN

B49

GPU_SMBCLK

B48

GPU_SMBDAT

Compal Electronics, Inc.

GPU

Title

SMBUS Address [0xXX]

SMBUS TOPOLOGY

Size

Document Number

Rev

1.0

LA-6592P

Date:

5

Thursday, January 13, 2011

Sheet

1

of

75

JCPU1I

(1)PEG_RCOMPO (H22) use 4mil connect to PEG_ICOMPI, then use 4mil connect to RC2.

(2)PEG_ICOMPO use 12mil connect to RC2

JCPU1A

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

B28

B26

A24

B23

16

16

16

16

DMI_CRX_PTX_P0

DMI_CRX_PTX_P1

DMI_CRX_PTX_P2

DMI_CRX_PTX_P3

16

16

16

16

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

DMI_CTX_PRX_N0

DMI_CTX_PRX_N1

DMI_CTX_PRX_N2

DMI_CTX_PRX_N3

G21

E22

F21

D21

16

16

16

16

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

DMI_CTX_PRX_P0

DMI_CTX_PRX_P1

DMI_CTX_PRX_P2

DMI_CTX_PRX_P3

G22

D22

F20

C21

16

16

16

16

16

16

16

16

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

FDI_CTX_PRX_N0

FDI_CTX_PRX_N1

FDI_CTX_PRX_N2

FDI_CTX_PRX_N3

FDI_CTX_PRX_N4

FDI_CTX_PRX_N5

FDI_CTX_PRX_N6

FDI_CTX_PRX_N7

16

16

16

16

16

16

16

16

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

FDI_CTX_PRX_P0

FDI_CTX_PRX_P1

FDI_CTX_PRX_P2

FDI_CTX_PRX_P3

FDI_CTX_PRX_P4

FDI_CTX_PRX_P5

FDI_CTX_PRX_P6

FDI_CTX_PRX_P7

A22

G19

E20

G18

B20

C19

D19

F17

FDI_FSYNC0

FDI_FSYNC1

J18

J17

16 FDI_FSYNC0

16 FDI_FSYNC1

16 FDI_INT

16 FDI_LSYNC0

16 FDI_LSYNC1

DMI_RX#[0]

DMI_RX#[1]

DMI_RX#[2]

DMI_RX#[3]

DMI_RX[0]

DMI_RX[1]

DMI_RX[2]

DMI_RX[3]

DMI_TX#[0]

DMI_TX#[1]

DMI_TX#[2]

DMI_TX#[3]

DMI_TX[0]

DMI_TX[1]

DMI_TX[2]

DMI_TX[3]

A21

H19

E19

F18

B21

C20

D18

E17

FDI0_TX#[0]

FDI0_TX#[1]

FDI0_TX#[2]

FDI0_TX#[3]

FDI1_TX#[0]

FDI1_TX#[1]

FDI1_TX#[2]

FDI1_TX#[3]

FDI0_TX[0]

FDI0_TX[1]

FDI0_TX[2]

FDI0_TX[3]

FDI1_TX[0]

FDI1_TX[1]

FDI1_TX[2]

FDI1_TX[3]

FDI_INT

H20

FDI_LSYNC0

FDI_LSYNC1

J19

H17

DMI

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

FDI0_FSYNC

FDI1_FSYNC

FDI_INT

FDI0_LSYNC

FDI1_LSYNC

(1) EDP_COMPIO use 4mil trace to RC1

(2) EDP_ICOMPO use 12mil to RC1

A18

A17

B16

C15

D15

C17

F16

C16

G15

B

C18

E16

D16

F15

eDP_COMPIO

eDP_ICOMPO

eDP_HPD

eDP_AUX

eDP_AUX#

eDP_TX[0]

eDP_TX[1]

eDP_TX[2]

eDP_TX[3]

eDP

EDP_COMP

J22

J21

H22

PEG_COMP

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

K33

M35

L34

J35

J32

H34

H31

G33

G30

F35

E34

E32

D33

D31

B33

C32

PEG_CRX_GTX_N0

PEG_CRX_GTX_N1

PEG_CRX_GTX_N2

PEG_CRX_GTX_N3

PEG_CRX_GTX_N4

PEG_CRX_GTX_N5

PEG_CRX_GTX_N6

PEG_CRX_GTX_N7

PEG_CRX_GTX_N8

PEG_CRX_GTX_N9

PEG_CRX_GTX_N10

PEG_CRX_GTX_N11

PEG_CRX_GTX_N12

PEG_CRX_GTX_N13

PEG_CRX_GTX_N14

PEG_CRX_GTX_N15

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

J33

L35

K34

H35

H32

G34

G31

F33

F30

E35

E33

F32

D34

E31

C33

B32

PEG_CRX_GTX_P0

PEG_CRX_GTX_P1

PEG_CRX_GTX_P2

PEG_CRX_GTX_P3

PEG_CRX_GTX_P4

PEG_CRX_GTX_P5

PEG_CRX_GTX_P6

PEG_CRX_GTX_P7

PEG_CRX_GTX_P8

PEG_CRX_GTX_P9

PEG_CRX_GTX_P10

PEG_CRX_GTX_P11

PEG_CRX_GTX_P12

PEG_CRX_GTX_P13

PEG_CRX_GTX_P14

PEG_CRX_GTX_P15

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PEG_TX#[14]

PEG_TX#[15]

M29

M32

M31

L32

L29

K31

K28

J30

J28

H29

G27

E29

F27

D28

F26

E25

PEG_CTX_GRX_C_N0

PEG_CTX_GRX_C_N1

PEG_CTX_GRX_C_N2

PEG_CTX_GRX_C_N3

PEG_CTX_GRX_C_N4

PEG_CTX_GRX_C_N5

PEG_CTX_GRX_C_N6

PEG_CTX_GRX_C_N7

PEG_CTX_GRX_C_N8

PEG_CTX_GRX_C_N9

PEG_CTX_GRX_C_N10

PEG_CTX_GRX_C_N11

PEG_CTX_GRX_C_N12

PEG_CTX_GRX_C_N13

PEG_CTX_GRX_C_N14

PEG_CTX_GRX_C_N15

M28

M33

M30

L31

L28

K30

K27

J29

J27

H28

G28

E28

F28

D27

E26

D25

PEG_CTX_GRX_C_P0

PEG_CTX_GRX_C_P1

PEG_CTX_GRX_C_P2

PEG_CTX_GRX_C_P3

PEG_CTX_GRX_C_P4

PEG_CTX_GRX_C_P5

PEG_CTX_GRX_C_P6

PEG_CTX_GRX_C_P7

PEG_CTX_GRX_C_P8

PEG_CTX_GRX_C_P9

PEG_CTX_GRX_C_P10

PEG_CTX_GRX_C_P11

PEG_CTX_GRX_C_P12

PEG_CTX_GRX_C_P13

PEG_CTX_GRX_C_P14

PEG_CTX_GRX_C_P15

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

eDP_TX#[0]

eDP_TX#[1]

eDP_TX#[2]

eDP_TX#[3]

PCI EXPRESS* - GRAPHICS

16

16

16

16

B27

B25

A25

B24

Intel(R) FDI

DMI_CRX_PTX_N0

DMI_CRX_PTX_N1

DMI_CRX_PTX_N2

DMI_CRX_PTX_N3

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

PEG_CRX_GTX_N[0..15] 46

PEG_CRX_GTX_P[0..15] 46

Sandy Bridge_rPGA_Rev1p0

PEG Compensation

DP Compensation

+1.05V_RUN_VTT

PEG_CTX_GRX_N[0..15]

PEG_CTX_GRX_P[0..15] 46

PEG_CTX_GRX_N[0..15] 46

PEG_CTX_GRX_C_P0

PEG_CTX_GRX_C_N0

CC49 2

CC33 2

1 0.22U_0402_16V7K~D

1 0.22U_0402_16V7K~D

PEG_CTX_GRX_P0

PEG_CTX_GRX_N0

PEG_CTX_GRX_C_P1

PEG_CTX_GRX_C_N1

CC50 2

CC34 2

1 0.22U_0402_16V7K~D

1 0.22U_0402_16V7K~D

PEG_CTX_GRX_P1

PEG_CTX_GRX_N1

PEG_CTX_GRX_C_P2

PEG_CTX_GRX_C_N2

CC51 2

CC35 2

1 0.22U_0402_16V7K~D

1 0.22U_0402_16V7K~D

PEG_CTX_GRX_P2

PEG_CTX_GRX_N2

PEG_CTX_GRX_C_P3

PEG_CTX_GRX_C_N3

CC52 2

CC36 2

1 0.22U_0402_16V7K~D

1 0.22U_0402_16V7K~D

PEG_CTX_GRX_P3

PEG_CTX_GRX_N3

PEG_CTX_GRX_C_P4

PEG_CTX_GRX_C_N4

CC53 2

CC37 2

1 0.22U_0402_16V7K~D

1 0.22U_0402_16V7K~D

PEG_CTX_GRX_P4

PEG_CTX_GRX_N4

PEG_CTX_GRX_C_P5

PEG_CTX_GRX_C_N5

CC54 2

CC38 2

1 0.22U_0402_16V7K~D

1 0.22U_0402_16V7K~D

PEG_CTX_GRX_P5

PEG_CTX_GRX_N5

PEG_CTX_GRX_C_P6

PEG_CTX_GRX_C_N6

CC55 2

CC39 2

1 0.22U_0402_16V7K~D

1 0.22U_0402_16V7K~D

PEG_CTX_GRX_P6

PEG_CTX_GRX_N6

PEG_CTX_GRX_C_P7

PEG_CTX_GRX_C_N7

CC56 2

CC40 2

1 0.22U_0402_16V7K~D

1 0.22U_0402_16V7K~D

PEG_CTX_GRX_P7

PEG_CTX_GRX_N7

PEG_CTX_GRX_C_P8

PEG_CTX_GRX_C_N8

CC57 1

CC41 1

2 0.22U_0402_16V7K~D

2 0.22U_0402_16V7K~D

PEG_CTX_GRX_P8

PEG_CTX_GRX_N8

PEG_CTX_GRX_C_P9

PEG_CTX_GRX_C_N9

CC58 1

CC42 1

2 0.22U_0402_16V7K~D

2 0.22U_0402_16V7K~D

PEG_CTX_GRX_P9

PEG_CTX_GRX_N9

PEG_CTX_GRX_C_P10 CC59 1

PEG_CTX_GRX_C_N10 CC43 1

2 0.22U_0402_16V7K~D

2 0.22U_0402_16V7K~D

PEG_CTX_GRX_P10

PEG_CTX_GRX_N10

PEG_CTX_GRX_C_P11 CC60 1

PEG_CTX_GRX_C_N11 CC44 1

2 0.22U_0402_16V7K~D

2 0.22U_0402_16V7K~D

PEG_CTX_GRX_P11

PEG_CTX_GRX_N11

PEG_CTX_GRX_C_P12 CC61 1

PEG_CTX_GRX_C_N12 CC45 1

2 0.22U_0402_16V7K~D

2 0.22U_0402_16V7K~D

PEG_CTX_GRX_P12

PEG_CTX_GRX_N12

PEG_CTX_GRX_C_P13 CC62 1

PEG_CTX_GRX_C_N13 CC46 1

2 0.22U_0402_16V7K~D

2 0.22U_0402_16V7K~D

PEG_CTX_GRX_P13

PEG_CTX_GRX_N13

PEG_CTX_GRX_C_P14 CC63 1

PEG_CTX_GRX_C_N14 CC47 1

2 0.22U_0402_16V7K~D

2 0.22U_0402_16V7K~D

PEG_CTX_GRX_P14

PEG_CTX_GRX_N14

PEG_CTX_GRX_C_P15 CC64 1

PEG_CTX_GRX_C_N15 CC48 1

2 0.22U_0402_16V7K~D

2 0.22U_0402_16V7K~D

PEG_CTX_GRX_P15

PEG_CTX_GRX_N15

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

F22

F19

E30

E27

E24

E21

E18

E15

E13

E10

E9

E8

E7

E6

E5

E4

E3

E2

E1

D35

D32

D29

D26

D20

D17

C34

C31

C28

C27

C25

C23

C10

C1

B22

B19

B17

B15

B13

B11

B9

B8

B7

B5

B3

B2

A35

A32

A29

A26

A23

A20

A3

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS

Sandy Bridge_rPGA_Rev1p0

+1.05V_RUN_VTT

PEG_CTX_GRX_P[0..15]

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

P9

P8

P6

P5

P3

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

M34

L33

L30

L27

L9

L8

L6

L5

L4

L3

L2

L1

K35

K32

K29

K26

J34

J31

H33

H30

H27

H24

H21

H18

H15

H13

H10

H9

H8

H7

H6

H5

H4

H3

H2

H1

G35

G32

G29

G26

G23

G20

G17

G11

F34

F31

F29

RC2

24.9_0402_1%~D

RC1

24.9_0402_1%~D

PEG_COMP

EDP_COMP

eDP_COMPIO and ICOMPO signals should be shorted near

balls and routed with typical impedance <25 mohms

PEG_ICOMPI and RCOMPO signals should be shorted and routed

with - max length = 500 mils - typical impedance = 43 mohms

PEG_ICOMPO signals should be routed with - max length = 500 mils

- typical impedance = 14.5 mohms

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Sandy Bridge (1/6)

Size

Document Number

Date:

Thursday, January 13, 2011

Rev

1.0

LA-6592P

Sheet

1

of

75

Follow DG Rev0.71 SM_DRAMPWROK topology

+1.5V_CPU_VDDQ

+1.05V_RUN_VTT

+3.3V_ALW_PCH

2

2

D

SYS_PWROK_XDP

RC64

39_0402_5%~D

+1.05V_RUN_VTT

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

9

9

CFG10

CFG11

CFG10

CFG11

XDP_OBS4

XDP_OBS5

The resistor for HOOK2 should beplaced

such that the stub is very small on CFG0 net

H_CPUPWRGD

1

RC51

@ RC6

1

RC71

@ RC9

1

RC1251

RC127

14,16 SIO_PWRBTN#_R

CFG0

+1.05V_RUN_VTT

12,13,14,15,28,36 DDR_XDP_WAN_SMBDAT

12,13,14,15,28,36 DDR_XDP_WAN_SMBCLK

H_THERMTRIP#

2

56_0402_5%~D

H_CATERR#

2

49.9_0402_1%~D

H_PROCHOT#

2

62_0402_5%~D

2 H_THERMTRIP#_R AN32

0_0402_5%~D

CLOCKS

@ RC13 1

@ RC15 1

2 0_0402_5%~D

2 0_0402_5%~D

DPLL_REF_CLK

DPLL_REF_CLK#

A16

A15

CPU_DPLL @ RC16 1

CPU_DPLL# @RC17 1

2 0_0402_5%~D

2 0_0402_5%~D

CLK_CPU_DMI 15

CLK_CPU_DMI# 15

XDP_RST#_R

1

@ RC48

@RC48

PROCHOT#

Max 500mils

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

AK1

A5

A4

SM_RCOMP2 --> 15mil

SM_RCOMP1/0 --> 20mil

THERMTRIP#

1

@ RC25

VCCPWRGOOD_0_R

0_0402_5%~D

AP33

PM_DRAM_PWRGD_CPU

PCH_PLTRST#_R

V8

AR33

UNCOREPWRGOOD

SM_DRAMPWROK

RESET#

JTAG & BPM

18 H_CPUPWRGD

PM_SYNC

PWR MANAGEMENT

AM34

TCK

TMS

TRST#

TDI

TDO

AP29

AP27

XDP_PRDY#

XDP_PREQ#

AR26

AR27

AP30

XDP_TCLK

XDP_TMS

XDP_TRST#

AR28

AP26

XDP_TDI_R

XDP_TDO_R

CFG16

CFG17

9

9

CFG0

CFG1

CFG0

CFG1

9

9

CFG2

CFG3

CFG2

CFG3

9

9

CFG8

CFG9

CFG8

CFG9

9

9

CFG4

CFG5

CFG4

CFG5

9

9

CFG6

CFG7

CFG6

CFG7

9

9

CLK_XDP

CLK_XDP#

XDP_RST#_R

XDP_DBRESET#

XDP_TDO

XDP_TRST#

XDP_TDI

XDP_TMS

1

1K_0402_5%~D

1

RH107

1

@ RH106

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

PLTRST_XDP# 17

C

2

0_0402_5%~D

2

0_0402_5%~D

CLK_CPU_ITP 15

CLK_CPU_ITP# 15

9 CLK_XDP_ITP

9 CLK_XDP_ITP#

1

@ RH109

1

@ RH108

2

0_0402_5%~D

2

0_0402_5%~D

1

CC177

0.047U_0402_16V4Z~D

1

@ RC46

1

@RC47

@

RC47

15 DDR_HVREF_RST_PCH

42 DDR_HVREF_RST_GATE

2

0_0402_5%~D

2

0_0402_5%~D

PU/PD for JTAG signals

+3.3V_RUN

XDP_DBRESET#

2

RC19

DBR#

DDR3_DRAMRST# 12

QC2

BSS138W-7-F_SOT323-3~D

DDR_HVREF_RST

2

PRDY#

PREQ#

H_PM_SYNC

RC50

4.99K_0402_1%~D

place RC129 near CPU

16 H_PM_SYNC

CLK_XDP

2

0_0402_5%~D

SM_DRAMRST#

DDR3_DRAMRST#_CPU

R8

CFG16

CFG17

CLK_CPU_DPLL 15

CLK_CPU_DPLL# 15

CLK_XDP#

PECI

2

RC8

CATERR#

Close to JCBU1

1

@ RC129

CPU_DMI

CPU_DMI#

AL32

A28

A27

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

GND1

OBSFN_C0

OBSFN_C1

GND3

OBSDATA_C0

OBSDATA_C1

GND5

OBSDATA_C2

OBSDATA_C3

GND7

OBSFN_D0

OBSFN_D1

GND9

OBSDATA_D0

OBSDATA_D1

GND11

OBSDATA_D2

OBSDATA_D3

GND13

ITPCLK/HOOK4

ITPCLK#/HOOK5

VCC_OBS_CD

RESET#/HOOK6

DBR#/HOOK7

GND15

TD0

TRST#

TDI

TMS

GND17

SAMTE_BSH-030-01-L-D-A

H_PROCHOT#_R

56_0402_5%~D

BCLK

BCLK#

GND0

OBSFN_A0

OBSFN_A1

GND2

OBSDATA_A0

OBSDATA_A1

GND4

OBSDATA_A2

OBSDATA_A3

GND6

OBSFN_B0

OBSFN_B1

GND8

OBSDATA_B0

OBSDATA_B1

GND10

OBSDATA_B2

OBSDATA_B3

GND12

PWRGOOD/HOOK0

HOOK1

VCC_OBS_AB

HOOK2

HOOK3

GND14

SDA

SCL

TCK1

TCK0

GND16

1

RC57

22 H_THERMTRIP#

DDR_XDP_WAN_SMBDAT_R1

DDR_XDP_WAN_SMBCLK_R1

AN33

H_PECI

42,58,60 H_PROCHOT#

AL33

SKTOCC#

DDR3

MISC

H_CATERR#

PROC_SELECT#

MISC

AN34

41 CPU_DETECT#

18

XDP_HOOK2

SYS_PWROK_XDP

Keep R1132, R1133, R1136-R119

for slew rate control.

JCPU1B

C26

C

H_CPUPWRGD_XDP

CFD_PWRBTN#_XDP

XDP_TCLK

THERMAL

1

@ RC126

1

@ RC128

1

RC44

16,41 SYS_PWROK

XDP_OBS6

XDP_OBS7

2

2 1K_0402_5%~D

0_0402_5%~D

2

2 1K_0402_5%~D

0_0402_5%~D

2

2 0_0402_5%~D

0_0402_5%~D

+1.05V_RUN_VTT

@JXDP1

@

JXDP1

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

XDP_PREQ#

XDP_PRDY#

Place near JXDP1

QC1

SSM3K7002FU_SC70-3~D

2

G

11,44 RUN_ON_CPU1.5VS3#

@ RC124

1K_0402_5%~D

2 PM_DRAM_PWRGD_CPU

130_0402_5%~D

1

RC28

74AHC1G09GW_TSSOP5~D

16 PM_DRAM_PWRGD

RUNPWROK_AND

1 1

+3.3V_ALW_PCH

2

200_0402_5%~D

1

RC18

UC2

1 B

41,42 RUNPWROK

RC12

200_0402_5%~D

CC66

0.1U_0402_16V4Z~D

0.1U_0402_16V4Z~D

CC1561

2

CC65

0.1U_0402_16V4Z~D

+3.3V_ALW_PCH

AL35

XDP_DBRESET#_R

2

@ RC26

AT28

AR29

AR30

AT30

AP32

AR31

AT31

AR32

XDP_OBS0_R

XDP_OBS1_R

XDP_OBS2_R

XDP_OBS3_R

XDP_OBS4_R

XDP_OBS5_R

XDP_OBS6_R

XDP_OBS7_R

2

2

2

2

2

2

2

2

@ RC30

@ RC31

@ RC33

@ RC34

@ RC36

@ RC37

@ RC38

@ RC39

1

1

1

1

1

1

1

1

XDP_DBRESET#

0_0402_5%~D

0_0402_5%~D

0_0402_5%~D

0_0402_5%~D

0_0402_5%~D

0_0402_5%~D

0_0402_5%~D

0_0402_5%~D

0_0402_5%~D

XDP_DBRESET# 14,16

XDP_OBS0

XDP_OBS1

XDP_OBS2

XDP_OBS3

XDP_OBS4

XDP_OBS5

XDP_OBS6

XDP_OBS7

XDP_TDI_R

1

1K_0402_5%~D

+1.05V_RUN_VTT

XDP_TDI

2

0_0402_5%~D

1

@ RC23

XDP_TDO_R

1

@ RC24

XDP_TDO

2

0_0402_5%~D

For ESD concern, please put near CPU

XDP_TMS

RC27 2

1 51_0402_1%~D

XDP_TDI_R

RC29 2

1 51_0402_1%~D

XDP_PREQ# @ RC32 2

1 51_0402_1%~D

XDP_TDO

RC35 2

1 51_0402_1%~D

XDP_TCLK

RC40 2

XDP_TRST#

RC41 2

51_0402_1%~D

Sandy Bridge_rPGA_Rev1p0

51_0402_1%~D

PCH_PLTRST#_BUF

1

2

1

2

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

DELL CONFIDENTIAL/PROPRIETARY

@ RC11

0_0402_5%~D

2

SN74LVC1G07DCKR_SC70-5~D

Open drain buffer

Avoid stub in the PWRGD path

while placing resistors RC25 & RC130

1

2

2 PCH_PLTRST#_R

43_0402_5%~D

1

1

RC10

5

P

RC45

200_0402_1%~D

NC

RC43

25.5_0402_1%~D

RC42

140_0402_1%~D

1

14,17 PCH_PLTRST#

SM_RCOMP2

SM_RCOMP1

SM_RCOMP0

RC130

10K_0402_5%~D

RC4

75_0402_1%~D

2

UC1

CC140

0.1U_0402_16V4Z~D

VCCPWRGOOD_0_R

+1.05V_RUN_VTT

+3.3V_RUN

Buffered reset to CPU

Title

Sandy Bridge (2/6)

Size

Document Number

Date:

Thursday, January 13, 2011

Rev

1.0

LA-6592P

Sheet

1

of

75

JCPU1D

JCPU1C

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D4

DDR_A_D5

DDR_A_D6

DDR_A_D7

DDR_A_D8

DDR_A_D9

DDR_A_D10

DDR_A_D11

DDR_A_D12

DDR_A_D13

DDR_A_D14

DDR_A_D15

DDR_A_D16

DDR_A_D17

DDR_A_D18

DDR_A_D19

DDR_A_D20

DDR_A_D21

DDR_A_D22

DDR_A_D23

DDR_A_D24

DDR_A_D25

DDR_A_D26

DDR_A_D27

DDR_A_D28

DDR_A_D29

DDR_A_D30

DDR_A_D31

DDR_A_D32

DDR_A_D33

DDR_A_D34

DDR_A_D35

DDR_A_D36

DDR_A_D37

DDR_A_D38

DDR_A_D39

DDR_A_D40

DDR_A_D41

DDR_A_D42

DDR_A_D43

DDR_A_D44

DDR_A_D45

DDR_A_D46

DDR_A_D47

DDR_A_D48

DDR_A_D49

DDR_A_D50

DDR_A_D51

DDR_A_D52

DDR_A_D53

DDR_A_D54

DDR_A_D55

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

DDR_A_D60

DDR_A_D61

DDR_A_D62

DDR_A_D63

12 DDR_A_BS0

12 DDR_A_BS1

12 DDR_A_BS2

12 DDR_A_CAS#

12 DDR_A_RAS#

12 DDR_A_WE#

DDR_A_BS0

DDR_A_BS1

DDR_A_BS2

DDR_A_CAS#

DDR_A_RAS#

DDR_A_WE#

C5

D5

D3

D2

D6

C6

C2

C3

F10

F8

G10

G9

F9

F7

G8

G7

K4

K5

K1

J1

J5

J4

J2

K2

M8

N10

N8

N7

M10

M9

N9

M7

AG6

AG5

AK6

AK5

AH5

AH6

AJ5

AJ6

AJ8

AK8

AJ9

AK9

AH8

AH9

AL9

AL8

AP11

AN11

AL12

AM12

AM11

AL11

AP12

AN12

AJ14

AH14

AL15

AK15

AL14

AK14

AJ15

AH15

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AE10

AF10

V6

SA_BS[0]

SA_BS[1]

SA_BS[2]

AE8

AD9

AF9

SA_CAS#

SA_RAS#

SA_WE#

SA_CLK[0]

SA_CLK#[0]

SA_CKE[0]

SA_CLK[1]

SA_CLK#[1]

SA_CKE[1]

AB6

AA6

V9

M_CLK_DDR0

M_CLK_DDR#0

DDR_CKE0_DIMMA

AA5

AB5

V10

M_CLK_DDR1

M_CLK_DDR#1

DDR_CKE1_DIMMA

RSVD_TP[1]

RSVD_TP[2]

RSVD_TP[3]

AB4

AA4

W9

RSVD_TP[4]

RSVD_TP[5]

RSVD_TP[6]

AB3

AA3

W10

SA_CS#[0]

SA_CS#[1]

RSVD_TP[7]

RSVD_TP[8]

AK3

AL3

AG1

AH1

DDR_CS0_DIMMA#

DDR_CS1_DIMMA#

SA_ODT[0]

SA_ODT[1]

RSVD_TP[9]

RSVD_TP[10]

AH3

AG3

AG2

AH2

M_ODT0

M_ODT1

C4

G6

J3

M6

AL6

AM8

AR12

AM15

DDR_A_DQS#0

DDR_A_DQS#1

DDR_A_DQS#2

DDR_A_DQS#3

DDR_A_DQS#4

DDR_A_DQS#5

DDR_A_DQS#6

DDR_A_DQS#7

D4

F6

K3

N6

AL5

AM9

AR11

AM14

DDR_A_DQS0

DDR_A_DQS1

DDR_A_DQS2

DDR_A_DQS3

DDR_A_DQS4

DDR_A_DQS5

DDR_A_DQS6

DDR_A_DQS7

AD10

W1

W2

W7

V3

V2

W3

W6

V1

W5

AD8

V4

W4

AF8

V5

V7

DDR_A_MA0

DDR_A_MA1

DDR_A_MA2

DDR_A_MA3

DDR_A_MA4

DDR_A_MA5

DDR_A_MA6

DDR_A_MA7

DDR_A_MA8

DDR_A_MA9

DDR_A_MA10

DDR_A_MA11

DDR_A_MA12

DDR_A_MA13

DDR_A_MA14

DDR_A_MA15

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

13 DDR_B_D[0..63]

M_CLK_DDR0 12

M_CLK_DDR#0 12

DDR_CKE0_DIMMA 12

M_CLK_DDR1 12

M_CLK_DDR#1 12

DDR_CKE1_DIMMA 12

DDR_CS0_DIMMA# 12

DDR_CS1_DIMMA# 12

M_ODT0

M_ODT1

12

12

DDR_A_DQS#[0..7]

DDR_A_DQS[0..7]

12

12

DDR_A_MA[0..15] 12

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

13 DDR_B_BS0

13 DDR_B_BS1

13 DDR_B_BS2

13 DDR_B_CAS#

13 DDR_B_RAS#

13 DDR_B_WE#

DDR_B_D0

DDR_B_D1

DDR_B_D2

DDR_B_D3

DDR_B_D4

DDR_B_D5

DDR_B_D6

DDR_B_D7

DDR_B_D8

DDR_B_D9

DDR_B_D10

DDR_B_D11

DDR_B_D12

DDR_B_D13

DDR_B_D14

DDR_B_D15

DDR_B_D16

DDR_B_D17

DDR_B_D18

DDR_B_D19

DDR_B_D20

DDR_B_D21

DDR_B_D22

DDR_B_D23

DDR_B_D24

DDR_B_D25

DDR_B_D26

DDR_B_D27

DDR_B_D28

DDR_B_D29

DDR_B_D30

DDR_B_D31

DDR_B_D32

DDR_B_D33

DDR_B_D34

DDR_B_D35

DDR_B_D36

DDR_B_D37

DDR_B_D38

DDR_B_D39

DDR_B_D40

DDR_B_D41

DDR_B_D42

DDR_B_D43

DDR_B_D44

DDR_B_D45

DDR_B_D46

DDR_B_D47

DDR_B_D48

DDR_B_D49

DDR_B_D50

DDR_B_D51

DDR_B_D52

DDR_B_D53

DDR_B_D54

DDR_B_D55

DDR_B_D56

DDR_B_D57

DDR_B_D58

DDR_B_D59

DDR_B_D60

DDR_B_D61

DDR_B_D62

DDR_B_D63

C9

A7

D10

C8

A9

A8

D9

D8

G4

F4

F1

G1

G5

F5

F2

G2

J7

J8

K10

K9

J9

J10

K8

K7

M5

N4

N2

N1

M4

N5

M2

M1

AM5

AM6

AR3

AP3

AN3

AN2

AN1

AP2

AP5

AN9

AT5

AT6

AP6

AN8

AR6

AR5

AR9

AJ11

AT8

AT9

AH11

AR8

AJ12

AH12

AT11

AN14

AR14

AT14

AT12

AN15

AR15

AT15

DDR_B_BS0

DDR_B_BS1

DDR_B_BS2

AA9

AA7

R6

SB_BS[0]

SB_BS[1]

SB_BS[2]

AA10

AB8

AB9

SB_CAS#

SB_RAS#

SB_WE#

DDR_B_CAS#

DDR_B_RAS#

DDR_B_WE#

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

DDR SYSTEM MEMORY B

12 DDR_A_D[0..63]

DDR SYSTEM MEMORY A

SB_CLK[0]

SB_CLK#[0]

SB_CKE[0]

AE2

AD2

R9

M_CLK_DDR2

M_CLK_DDR#2

DDR_CKE2_DIMMB

SB_CLK[1]

SB_CLK#[1]

SB_CKE[1]

AE1

AD1

R10

M_CLK_DDR3

M_CLK_DDR#3

DDR_CKE3_DIMMB

RSVD_TP[11]

RSVD_TP[12]

RSVD_TP[13]

AB2

AA2

T9

RSVD_TP[14]

RSVD_TP[15]

RSVD_TP[16]

AA1

AB1

T10

SB_CS#[0]

SB_CS#[1]

RSVD_TP[17]

RSVD_TP[18]

AD3

AE3

AD6

AE6

SB_ODT[0]

SB_ODT[1]

RSVD_TP[19]

RSVD_TP[20]

AE4

AD4

AD5

AE5

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

D7

F3

K6

N3

AN5

AP9

AK12

AP15

DDR_B_DQS#0

DDR_B_DQS#1

DDR_B_DQS#2

DDR_B_DQS#3

DDR_B_DQS#4

DDR_B_DQS#5

DDR_B_DQS#6

DDR_B_DQS#7

C7

G3

J6

M3

AN6

AP8

AK11

AP14

DDR_B_DQS0

DDR_B_DQS1

DDR_B_DQS2

DDR_B_DQS3

DDR_B_DQS4

DDR_B_DQS5

DDR_B_DQS6

DDR_B_DQS7

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

DDR_CS2_DIMMB#

DDR_CS3_DIMMB#

M_ODT2

M_ODT3

M_CLK_DDR2 13

M_CLK_DDR#2 13

DDR_CKE2_DIMMB 13

M_CLK_DDR3 13

M_CLK_DDR#3 13

DDR_CKE3_DIMMB 13

DDR_CS2_DIMMB# 13

DDR_CS3_DIMMB# 13

M_ODT2

M_ODT3

13

13

DDR_B_DQS#[0..7]

13

DDR_B_DQS[0..7]

13

DDR_B_MA[0..15] 13

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

AA8

T7

R7

T6

T2

T4

T3

R2

T5

R3

AB7

R1

T1

AB10

R5

R4

DDR_B_MA0

DDR_B_MA1

DDR_B_MA2

DDR_B_MA3

DDR_B_MA4

DDR_B_MA5

DDR_B_MA6

DDR_B_MA7

DDR_B_MA8

DDR_B_MA9

DDR_B_MA10

DDR_B_MA11

DDR_B_MA12

DDR_B_MA13

DDR_B_MA14

DDR_B_MA15

Sandy Bridge_rPGA_Rev1p0

Sandy Bridge_rPGA_Rev1p0

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Sandy Bridge (3/6)

Size

Document Number

Date:

Thursday, January 13, 2011

Rev

1.0

LA-6592P

Sheet

1

of

75

CFG Straps for Processor

CFG2

JCPU1E

RSVD1

2

49.9_0402_1%~D

1

@RC122

@

RC122

7

7

CFG16

CFG17

+VCC_CORE

RSVD1

RSVD2

RSVD3

RSVD4

@RC120

@

RC120

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

AJ31

AH31

AJ33

AH33

VAXG_VAL_SENSE

VSSAXG_VAL_SENSE

VCC_VAL_SENSE

VSS_VAL_SENSE

AJ26

RSVD5

+DIMM0_1_VREF_CPU B4

+DIMM0_1_CA_CPU D1

RSVD6

RSVD7

RSVD3

2

49.9_0402_1%~D

RSVD28

RSVD29

RSVD30

RSVD31

RSVD32

L7

AG7

AE7

AK2

W8

@ T1

@ T2

@ T3

@ T4

@ T5

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

RSVD33

RSVD34

RSVD35

AT26

AM33

AJ27

@ T6

@ T7

@ T8

PAD~D

PAD~D

PAD~D

RSVD37

RSVD38

RSVD39

RSVD40

T8

J16

H16

G16

@ T11

@ T13

@ T15

@ T16

PAD~D

PAD~D

PAD~D

PAD~D

RSVD41

RSVD42

RSVD43

RSVD44

RSVD45

AR35

AT34

AT33

AP35

AR34

@ T17

@ T18

@ T19

@ T20

@ T21

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PEG Static Lane Reversal - CFG2 is for the 16x

CFG2

CFG4

@ RC52

1K_0402_5%~D

follow DG0.9 change to 1Kohm 5%

Display Port Presence Strap

1

@RC96

@

RC96

1

@RC97

@

RC97

+DIMM0_1_VREF_CPU

+DIMM0_1_CA_CPU

@ T28

@ T29

@ T30

@ T31

@ T33

@ T35

@ T36

@ T37

@ T38

@ T40

@ T41

@ T42

@ T43

@ T44

@ T45

@ T46

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

F25

F24

F23

D24

G25

G24

E23

D23

C30

A31

B30

B29

D30

B31

A30

C29

@ T47

@ T48

@ T155

PAD~D

PAD~D

PAD~D

J20

B18

A19

@ T52

PAD~D

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD23

CFG4

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

@ T23

@ T24

@ T25

@ T26

@ T27

B34

A33

A34

B35

C35

1 : Disabled; No Physical Display Port

attached to Embedded Display Port

0 : Enabled; An external Display Port device is

connected to the Embedded Display Port

PAD~D

PAD~D

PAD~D

PAD~D

PAD~D

CFG6

CFG5

RSVD51

RSVD52

VCC_DIE_SENSE

RSVD54

RSVD55

AJ32

AK32

@ T32 PAD~D

@ T34 PAD~D

AH27

@ T39 PAD~D

1

@RC121

@

RC121

@ T22 PAD~D

@ RC54

1K_0402_5%~D

AN35

AM35

@ RC53

1K_0402_5%~D

RSVD2

2

49.9_0402_1%~D

RSVD4

2

49.9_0402_1%~D

+DIMM0_1_VREF_CPU

2

1K_0402_5%~D

+DIMM0_1_CA_CPU

2

1K_0402_5%~D

RESERVED

@RC123

@

RC123

1:(Default) Normal Operation; Lane #

definition matches socket pin map definition

0:Lane Reversed

AK28

AK29

AL26

AL27

AK26

AL29

AL30

AM31

AM32

AM30

AM28

AM26

AN28

AN31

AN26

AM27

AK31

AN29

+VCC_GFXCORE

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

PAD~D

PAD~D

PAD~D

PAD~D

7

7

7

7

7

7

7

7

7

7

7

7

@ T9

@ T10

@ T12

@ T14

@RC51

@

RC51

1K_0402_5%~D

CLK_XDP_ITP 7

CLK_XDP_ITP# 7

PCIE Port Bifurcation Straps

RSVD24

RSVD25

VCCIO_SEL

J15

RSVD56

RSVD57

RSVD58

AT2

AT1

AR1

@ T49 PAD~D

@ T50 PAD~D

@ T51 PAD~D

B1

@ T53 PAD~D

11: (Default) x16 - Device 1 functions 1 and 2 disabled

CFG[6:5]

RSVD27

KEY

10: x8, x8 - Device 1 function 1 enabled ; function 2

disabled

01: Reserved - (Device 1 function 1 disabled ; function

2 enabled)

00: x8,x4,x4 - Device 1 functions 1 and 2 enabled

CFG7

1

Sandy Bridge_rPGA_Rev1p0

@ RC56

1K_0402_5%~D

PEG DEFER TRAINING

CFG7

1: (Default) PEG Train immediately

following xxRESETB de assertion

0: PEG Wait for BIOS for training

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Sandy Bridge (4/6)

Size

Rev

1.0

LA-6592P

Date:

Document Number

Thursday, January 13, 2011

Sheet

1

of

75

JCPU1F

POWER

+1.05V_RUN_VTT

+VCC_CORE

+VCC_CORE

CC120

CC121

CC122

CC123

CC124

22U_0805_6.3VAM~D 22U_0805_6.3VAM~D 22U_0805_6.3VAM~D 22U_0805_6.3VAM~D 22U_0805_6.3VAM~D

2

2

2

2

2

CC125

22U_0805_6.3VAM~D

+VCC_CORE

1

+

1

+ @CC130

470U_D2_2V-M~D

CC129

470U_D2_2V-M~D

2 3

2 3

+

2 3

+ @CC133

470U_D2_2V-M~D

2 3

2 3

1

CC131

470U_D2_2V-M~D

CC132

470U_D2_2V-M~D

2 3

CC134

470U_D2_2V-M~D

+1.05V_RUN_VTT

1

PEG AND DDR

Note: Place the PU resistors close to CPU

R1555 close to CPU 300 - 1500mils

2

RC60

75_0402_1%~D

H_CPU_SVIDALRT#

1

RC61

2

43_0402_5%~D

VIDALERT_N

58

+1.05V_RUN_VTT

CAD Note: Place the PU

resistors close to CPU

R1558 close to CPU 300 - 1500mils

RC63

130_0402_1%~D

VIDALERT#

VIDSCLK

VIDSOUT

AJ29

AJ30

AJ28

H_CPU_SVIDALRT#

VIDSCLK

VIDSOUT

VIDSCLK

58

VIDSOUT

Iccmax current changed for PDDG Rev0.7

58

CPU Power Rail Table

SVID note: VIDALERT# trace

routing need to be routed between

VIDSCLK and VIDSOUT signals

Voltage Rail

Voltage

VCC

0.65-1.3

VCCIO

+VCC_CORE

RC66

100_0402_1%~D

Place RC66, RC70near CPU

VCC_SENSE

VSS_SENSE

AJ35

AJ34

S0 Iccmax

Current (A)

8.5

0.0-1.1

26

VCCPLL

1.8

VDDQ

1.5

VCCSA

VCCSENSE_R

1

VSSSENSE_R @ RC67 1

@ RC68

2

2 0_0402_5%~D

0_0402_5%~D

VTT_SENSE_R

1

VSSIO_SENSE_R @ RC1321

@ RC133

2

2 0_0402_5%~D

0_0402_5%~D

VCCSENSE

VSSSENSE

VCCIO_SENSE

VSSIO_SENSE

B10

A10

VTT_SENSE

VTT_GND

RC70

100_0402_1%~D

57

57

58

58

0.65-0.9

+1.5V_MEM

1.5

12-16

Description

5A to Mem controller(+1.5V_CPU_VDDQ)

5-6A to 2 DIMMs/channel

2-5A to +1.5V_RUN & +0.75V_DDR_VTT

A

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

Sandy Bridge_rPGA_Rev1p0

Title

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Sandy Bridge (5/6)

Size

Document Number

Rev

1.0

LA-6592P

Date:

53

1.05

VAXG

J23

CC115

CC116

CC117

CC118

CC119

22U_0805_6.3VAM~D 22U_0805_6.3VAM~D 22U_0805_6.3VAM~D 22U_0805_6.3VAM~D 22U_0805_6.3VAM~D

2

2

2

2

2

VCCIO40

SVID

SENSE LINES

CC86

22U_0805_6.3VAM~D

CC70

22U_0805_6.3VAM~D

CC85

22U_0805_6.3VAM~D

CC110

CC111

CC112

CC113

CC114

22U_0805_6.3VAM~D 22U_0805_6.3VAM~D 22U_0805_6.3VAM~D 22U_0805_6.3VAM~D 22U_0805_6.3VAM~D

2

2

2

2

2

CC109

330U_D2_2VM_R6M~D

1

C

E11

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

CC108

330U_D2_2VM_R6M~D

+VCC_CORE

VCCIO25

VCCIO26

VCCIO27

VCCIO28

VCCIO29

VCCIO30

VCCIO31

VCCIO32

VCCIO33

VCCIO34

VCCIO35

VCCIO36

VCCIO37

VCCIO38

VCCIO39

CC107

330U_D2_2VM_R6M~D

CC73

10U_0805_4VAM~D

@ CC93

22U_0805_6.3VAM~D

CC84

22U_0805_6.3VAM~D

1

CC88

10U_0805_4VAM~D

@ CC92

22U_0805_6.3VAM~D

CC77

10U_0805_4VAM~D

CC83

22U_0805_6.3VAM~D

1

CC72

10U_0805_4VAM~D

@ CC91

22U_0805_6.3VAM~D

CC76

10U_0805_4VAM~D

CC82

22U_0805_6.3VAM~D

1

CC71

10U_0805_4VAM~D

AH13

AH10

AG10

AC10

Y10

U10

P10

L10

J14

J13

J12

J11

H14

H12

H11

G14

G13

G12

F14

F13

F12

F11

E14

E12

@ CC90

22U_0805_6.3VAM~D

CC68

10U_0805_4VAM~D

VCCIO1

VCCIO2

VCCIO3

VCCIO4

VCCIO5

VCCIO6

VCCIO7

VCCIO8

VCCIO9

VCCIO10

VCCIO11

VCCIO12

VCCIO13

VCCIO14

VCCIO15

VCCIO16

VCCIO17

VCCIO18

VCCIO19

VCCIO20

VCCIO21

VCCIO22

VCCIO23

VCCIO24

CC81

22U_0805_6.3VAM~D

1

CC87

10U_0805_4VAM~D

8.5A

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

CC89

22U_0805_6.3VAM~D

CC75

10U_0805_4VAM~D

AG34

AG33

AG32

AG31

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

Y35

Y34

Y33

Y32

Y31

Y30

Y29

Y28

Y27

Y26

V35

V34

V33

V32

V31

V30

V29

V28

V27

V26

U35

U34

U33

U32

U31

U30

U29

U28

U27

U26

R35

R34

R33

R32

R31

R30

R29

R28

R27

R26

P35

P34

P33

P32

P31

P30

P29

P28

P27

P26

CC80

22U_0805_6.3VAM~D

CC79

22U_0805_6.3VAM~D

CC67

10U_0805_4VAM~D

CC69

22U_0805_6.3VAM~D

CC78

22U_0805_6.3VAM~D

CORE SUPPLY

53AAG35

1

Thursday, January 13, 2011

Sheet

1

10

of

75

+1.5V_CPU_VDDQ Source

4

2

RUN_ON_CPU1.5VS3

RUN_ON_CPU1.5VS3#

QC4B

DMN66D0LDW-7_SOT363-6~D

4

+1.5V_CPU_VDDQ

1

2

3

@ RC73

20K_0402_5%~D

8

7

6

5

CC135

10U_0805_6.3V6M~D

RC72

100K_0402_5%~D

RC74

100K_0402_5%~D

QC3

AO4728L_SO8~D

+15V_ALW

1

+3.3V_ALW2

+1.5V_MEM

JCPU1H

1

CC136

4700P_0402_25V7K~D

+V_DDR_REF

3

1

QC4A

DMN66D0LDW-7_SOT363-6~D

2

1

2

0_0402_5%~D

1

@ RC79

42 CPU1.5V_S3_GATE

2

0_0402_5%~D

1

@ RC134

VREF

SM_VREF

1 0.1U_0402_10V7K~D

CC1792

1 0.1U_0402_10V7K~D

CC1492

1 0.1U_0402_10V7K~D

CC1502

1 0.1U_0402_10V7K~D

AL1

+V_SM_VREF should

have 10 mil trace width

@ CC171

10U_0603_6.3V6M~D

CC170

10U_0805_4VAM~D

M27

M26

L26

J26

J25

J24

H26

H25

VCCSA_SENSE

1

+

2

PAD-OPEN 4x4m

C22

C24

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS

AJ22

AJ19

AJ16

AJ13

AJ10

AJ7

AJ4

AJ3

AJ2

AJ1

AH35

AH34

AH32

AH30

AH29

AH28

AH26

AH25

AH22

AH19

AH16

AH7

AH4

AG9

AG8

AG4

AF6

AF5

AF3

AF2

AE35

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE9

AD7

AC9

AC8

AC6

AC5

AC3

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

Y9

Y8

Y6

Y5

Y3

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

U9

U8

U6

U5

U3

U2

1

+

CC172

330U_D2_2VM_R6M~D

Sandy Bridge_rPGA_Rev1p0

2

0_0402_5%~D

+GND_VCC_SA 61

+VCCSA_SENSE 61

1

@ RC138

H_FC_C22

2

0_0402_5%~D

VCCSA_VID_1 61

Sandy Bridge_rPGA_Rev1p0

RC83

10K_0402_5%~D

FC_C22

VCCSA_VID1

+VCC_SA

H23

DDR3 -1.5V RAILS

6A

VCCSA1

VCCSA2

VCCSA3

VCCSA4

VCCSA5

VCCSA6

VCCSA7

VCCSA8

CC169

10U_0805_4VAM~D

SA RAIL

CC167

330U_D2_2VM_R6M~D

CC166

10U_0805_4VAM~D

1

@ RC137

MISC

+1.5V_MEM

@ PJP2

1

CC165

10U_0805_4VAM~D

AF7

AF4

AF1

AC7

AC4

AC1

Y7

Y4

Y1

U7

U4

U1

P7

P4

P1

5A

CC164

10U_0805_4VAM~D

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

PAD-OPEN 4x4m

CC163

10U_0805_4VAM~D

VCCPLL1

VCCPLL2

VCCPLL3

CC168

10U_0805_4VAM~D

+

2

CC1782

+V_SM_VREF_CNT

CC162

10U_0805_4VAM~D

CC176

330U_D2_2.5VM_R6M~D

CC175

1U_0402_6.3V6K~D

CC174

1U_0402_6.3V6K~D

2

A

CC173

10U_0805_4VAM~D

B6

A6

A2

VCC_AXG_SENSE 58

VSS_AXG_SENSE 58

@ PJP1

3A

+1.8V_RUN

AK35

AK34

CC161

10U_0805_4VAM~D

VAXG_SENSE

VSSAXG_SENSE

+1.5V_CPU_VDDQ

GRAPHICS

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

VAXG50

VAXG51

VAXG52

VAXG53

VAXG54

1.8V RAIL

CC148

22U_0805_6.3VAM~D

CC139

22U_0805_6.3VAM~D

CC147

22U_0805_6.3VAM~D

CC146

22U_0805_6.3VAM~D

CC153

22U_0805_6.3VAM~D

CC145

22U_0805_6.3VAM~D

CC152

22U_0805_6.3VAM~D

CC141

22U_0805_6.3VAM~D

CC151

22U_0805_6.3VAM~D

CC144

22U_0805_6.3VAM~D

CC138

22U_0805_6.3VAM~D

CC137

22U_0805_6.3VAM~D

AT24

AT23

AT21

AT20

AT18

AT17

AR24

AR23

AR21

AR20

AR18

AR17

AP24

AP23

AP21

AP20

AP18

AP17

AN24

AN23

AN21

AN20

AN18

AN17

AM24

AM23

AM21

AM20

AM18

AM17

AL24

AL23

AL21

AL20

AL18

AL17

AK24

AK23

AK21

AK20

AK18

AK17

AJ24

AJ23

AJ21

AJ20

AJ18

AJ17

AH24

AH23

AH21

AH20

AH18

AH17

SENSE

LINES

JCPU1G

26A

2

0_0402_5%~D

RUN_ON_CPU1.5VS3

POWER

+VCC_GFXCORE

RC78

100K_0402_5%~D

RUN_ON_CPU1.5VS3# 7,44

1

@ RC77

37,41,44,55,63 RUN_ON

+V_SM_VREF_CNT

QC5

NTR4503NT1G_SOT23-3~D

AT35

AT32

AT29

AT27

AT25

AT22

AT19

AT16

AT13

AT10

AT7

AT4

AT3

AR25

AR22

AR19

AR16

AR13

AR10

AR7

AR4

AR2

AP34

AP31

AP28

AP25

AP22

AP19

AP16

AP13

AP10

AP7

AP4

AP1

AN30

AN27

AN25

AN22

AN19

AN16

AN13

AN10

AN7

AN4

AM29

AM25

AM22

AM19

AM16

AM13

AM10

AM7

AM4

AM3

AM2

AM1

AL34

AL31

AL28

AL25

AL22

AL19

AL16

AL13

AL10

AL7

AL4

AL2

AK33

AK30

AK27

AK25

AK22

AK19

AK16

AK13

AK10

AK7

AK4

AJ25

DELL CONFIDENTIAL/PROPRIETARY

Compal Electronics, Inc.

PROPRIETARY NOTE: THIS SHEET OF ENGINEERING DRAWING AND SPECIFICATIONS CONTAINS CONFIDENTIAL

TRADE SECRET AND OTHER PROPRIETARY INFORMATION OF DELL INC. ("DELL") THIS DOCUMENT MAY NOT

BE TRANSFERRED OR COPIED WITHOUT THE EXPRESS WRITTEN AUTHORIZATION OF DELL. IN ADDITION,

NEITHER THIS SHEET NOR THE INFORMATION IT CONTAINS WAY BE USED BY OR DISCLOSED TO ANY THIRD

PARTY WITHOUT DELL'S EXPRESS WRITTEN CONSENT.

Title

Sandy Bridge (6/6)

Size

Rev

1.0

LA-6592P

Date:

Document Number

Thursday, January 13, 2011

Sheet

1

11

of

75

+DIMM0_1_VREF_CPU

+DIMM0_1_VREF_DQ

2

0_0402_5%~D

2

0_0402_5%~D

All VREF traces should

have 10 mil trace width

8 DDR_A_D[0..63]

D

CD2

0.1U_0402_16V4Z~D

8 DDR_A_DQS#[0..7]

DDR_A_D0

DDR_A_D1

DDR_A_D2

DDR_A_D3

DDR_A_D8

DDR_A_D9

DDR_A_DQS#1

DDR_A_DQS1

8 DDR_A_DQS[0..7]

Populate RD1 for Intel DDR3

VREFDQ multiple methods M1

8 DDR_A_MA[0..15]

DDR_A_D10

DDR_A_D11

DDR_A_D16

DDR_A_D17

DDR_A_DQS#2

DDR_A_DQS2

Layout Note:

Place near JDIMMA

DDR_A_D18

DDR_A_D19

DDR_A_D24

DDR_A_D25

+1.5V_MEM

DDR_A_D26

DDR_A_D27

CD6

1U_0402_6.3V6K~D

CD5

1U_0402_6.3V6K~D

CD4

1U_0402_6.3V6K~D

CD3

1U_0402_6.3V6K~D

8 DDR_CKE0_DIMMA

8

DDR_A_BS2

DDR_CKE0_DIMMA

DDR_A_BS2

DDR_A_MA12

DDR_A_MA9

DDR_A_MA8

DDR_A_MA5

+1.5V_MEM

DDR_A_MA3

DDR_A_MA1

+

2

8 M_CLK_DDR0

8 M_CLK_DDR#0

CD14

330U_SX_2VY~D

@ CD13

10U_0603_6.3V6M~D

CD12

10U_0603_6.3V6M~D

CD11

10U_0603_6.3V6M~D

CD10

10U_0603_6.3V6M~D

CD9

10U_0603_6.3V6M~D

CD8

10U_0603_6.3V6M~D

CD7

10U_0603_6.3V6M~D

DDR_A_BS0

8

8

DDR_A_WE#

DDR_A_CAS#

8 DDR_CS1_DIMMA#

M_CLK_DDR0

M_CLK_DDR#0

DDR_A_MA10

DDR_A_BS0

DDR_A_WE#

DDR_A_CAS#

DDR_A_MA13

DDR_CS1_DIMMA#

DDR_A_D40

DDR_A_D41

B

+0.75V_DDR_VTT

DDR_A_D42

DDR_A_D43

CD20

1U_0402_6.3V6K~D

CD19

1U_0402_6.3V6K~D

CD18

1U_0402_6.3V6K~D

CD17

1U_0402_6.3V6K~D

DDR_A_D48

DDR_A_D49

DDR_A_DQS#6

DDR_A_DQS6

DDR_A_D50

DDR_A_D51

DDR_A_D56

DDR_A_D57

DDR_A_D58

DDR_A_D59

RD21

CD22

2.2U_0603_6.3V6K~D

CD21

0.1U_0402_16V4Z~D

1

RD3

2 10K_0402_5%~D

+3.3V_RUN

2

10K_0402_5%~D

1

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

63

65

67

69

71

VREF_DQ

VSS

DQ0

DQ1

VSS

DM0

VSS

DQ2

DQ3

VSS

DQ8

DQ9

VSS

DQS1#

DQS1

VSS

DQ10

DQ11

VSS

DQ16

DQ17

VSS

DQS2#

DQS2

VSS

DQ18

DQ19

VSS

DQ24

DQ25

VSS

DM3

VSS

DQ26

DQ27

VSS

73

75

77

79

81

83

85

87

89

91

93

95

97

99

101

103

105

107

109

111

113

115

117

119

121

123

125

127

129

131

133

135

137

139

141

143

145

147

149

151

153

155

157

159

161

163

165

167

169

171

173

175

177

179

181

183

185

187

189

191

193

195

197

199

201

203

CKE0

VDD

NC

BA2

VDD

A12/BC#

A9

VDD

A8

A5

VDD

A3

A1

VDD

CK0

CK0#

VDD

A10/AP

BA0

VDD

WE#

CAS#

VDD

A13

S1#

VDD

TEST

VSS

DQ32

DQ33

VSS

DQS4#

DQS4

VSS

DQ34

DQ35

VSS

DQ40

DQ41

VSS

DM5

VSS

DQ42

DQ43

VSS

DQ48

DQ49

VSS

DQS6#

DQS6

VSS

DQ50

DQ51

VSS

DQ56

DQ57

VSS

DM7

VSS

DQ58